Synopsys 3DIC Compiler 2024.09 Linux Synopsys Avalon 2024.09 Linux Synopsys Certitude 2025.06/2024.09 Linux Synopsys Chamber Matching 2022.12 Synopsys CODE V 2025.03 Synopsys LightTools 2025.03 Synopsys LucidShape 2024.09 Synopsys LucidShape CAA V5 Based 2024.09 Synopsys coreTools 2025.06/2024.09 Linux64 Synopsys Custom Compiler 2024.09-SP1 Linux Synopsys Custom WaveView 2025.06 Synopsys DVE 2025.06/2024.09 Linux64 Synopsys Embedit 2025.06 Linux64 Synopsys ESP 2024.09 Linux64 Synopsys Euclide 2025.06 Win/Linux Synopsys FineSim 2025.06 Linux64 Synopsys Formality 2025.06/2024.09 Linux64 Synopsys Fusion Compiler 2025.06/2024.09 Linux64 Synopsys HSPICE 2025.06/2024.09 Win64/Linux64 Synopsys IC Compiler 2025.06/2024.09 Linux64 Synopsys IC Compiler II 2025.06/2024.09 Linux64 Synopsys IC Validator 2025.06/2024.09 Linux64 Synopsys IC Validator Workbench 2024.09 Linux64 Synopsys ICE Speed Adaptor 2023.09 Linux64 Synopsys Laker OA 2023.09 Linux64 Synopsys Library Compiler 2025.06/2023.12-SP3 Linux64 Synopsys LucidDrive 2024.03...

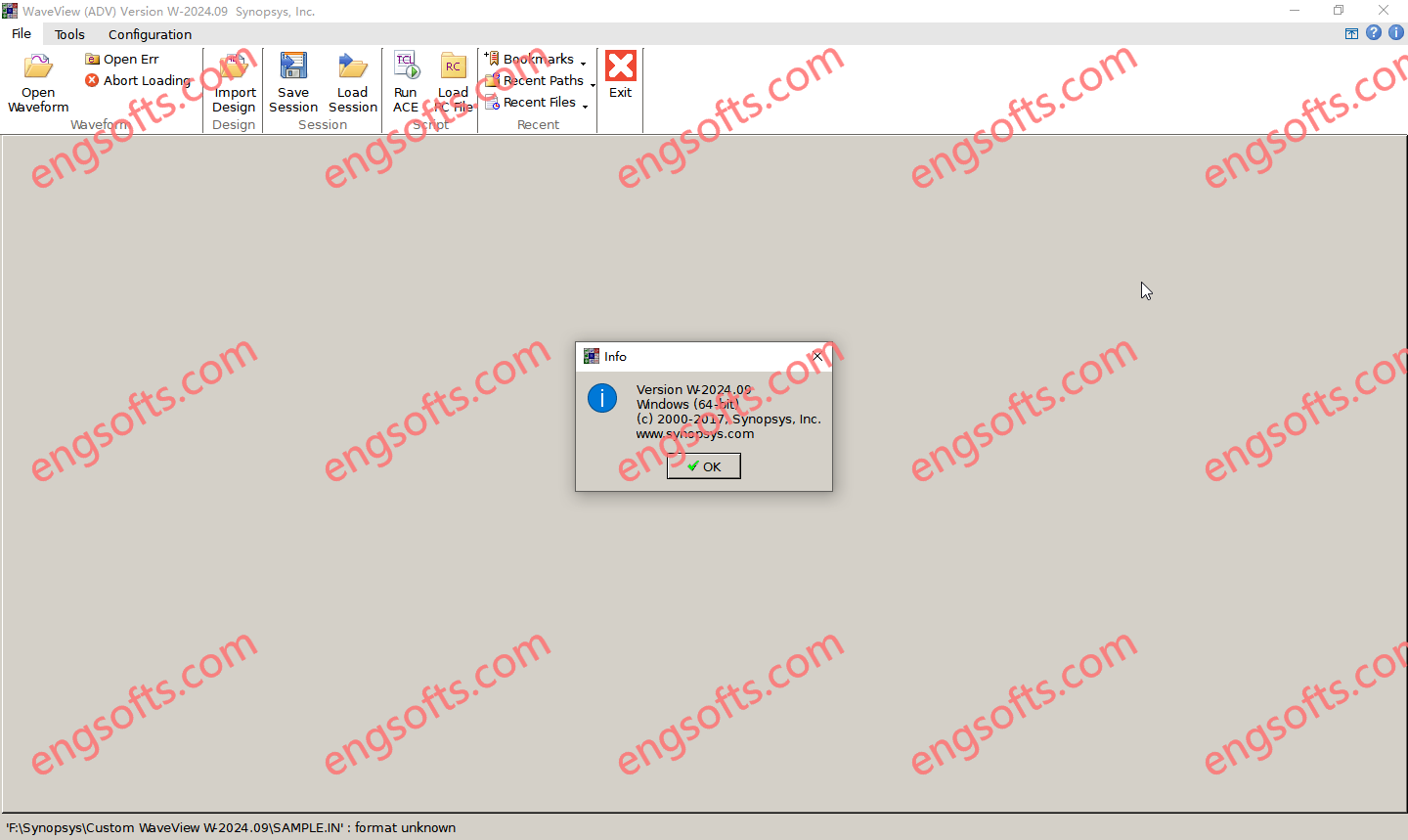

Custom WaveView ADV 提供完整的晶体管级分析和调试环境,用于 SPICE 和 FastSPICE 仿真的预处理和后处理。Custom WaveView ADV 与 Synopsys 的 HSPICE®、FineSim® 和 CustomSim™ 集成,可简化 SPICE 和 FastSPICE 仿真的调试和分析流程,并提高设计效率。 Custom WaveView ADV 与 Synopsys 电路仿真器的结合为设计团队提供了高性能、高效率的仿真调试和分析环境,适用于复杂的 SoC 设计。 Synopsys Custom WaveView ADV 2024.09 Win/Linux64 Tested Picture Custom WaveView ADV 是一款基于网表的调试环境,适用于 SPICE 和 FastSPICE 仿真器,例如 HSPICE、FineSim 和 CustomSim。 Custom WaveView ADV 还与 Custom WaveView 紧密集成,支持波形交叉探测。这些工具协同工作,帮助设计人员在高效的设计调试和波形分析环境中快速执行定制的高级分析。 Custom WaveView ADV 设计浏览器 Custom WaveView ADV 设计浏览器可以快速访问最复杂的层次结构设计数据,并完整显示设计和文件信息。设计浏览器可以导入网表,并允许遍历设计层次结构、显示信号和元件列表,以及追踪层次结构中包含的连接。图 1 所示的这些视图协同工作,可以快速访问设计层次结构的所有内容。除了显示设计层次结构之外,设计浏览器还会显示包含该设计的相关文件层次结构。强大的搜索功能允许用户根据字符串、信号、实例和模块名称在层次结构中查找设计组件。 More for English: Synopsys Custom WaveView ADV 2024.09

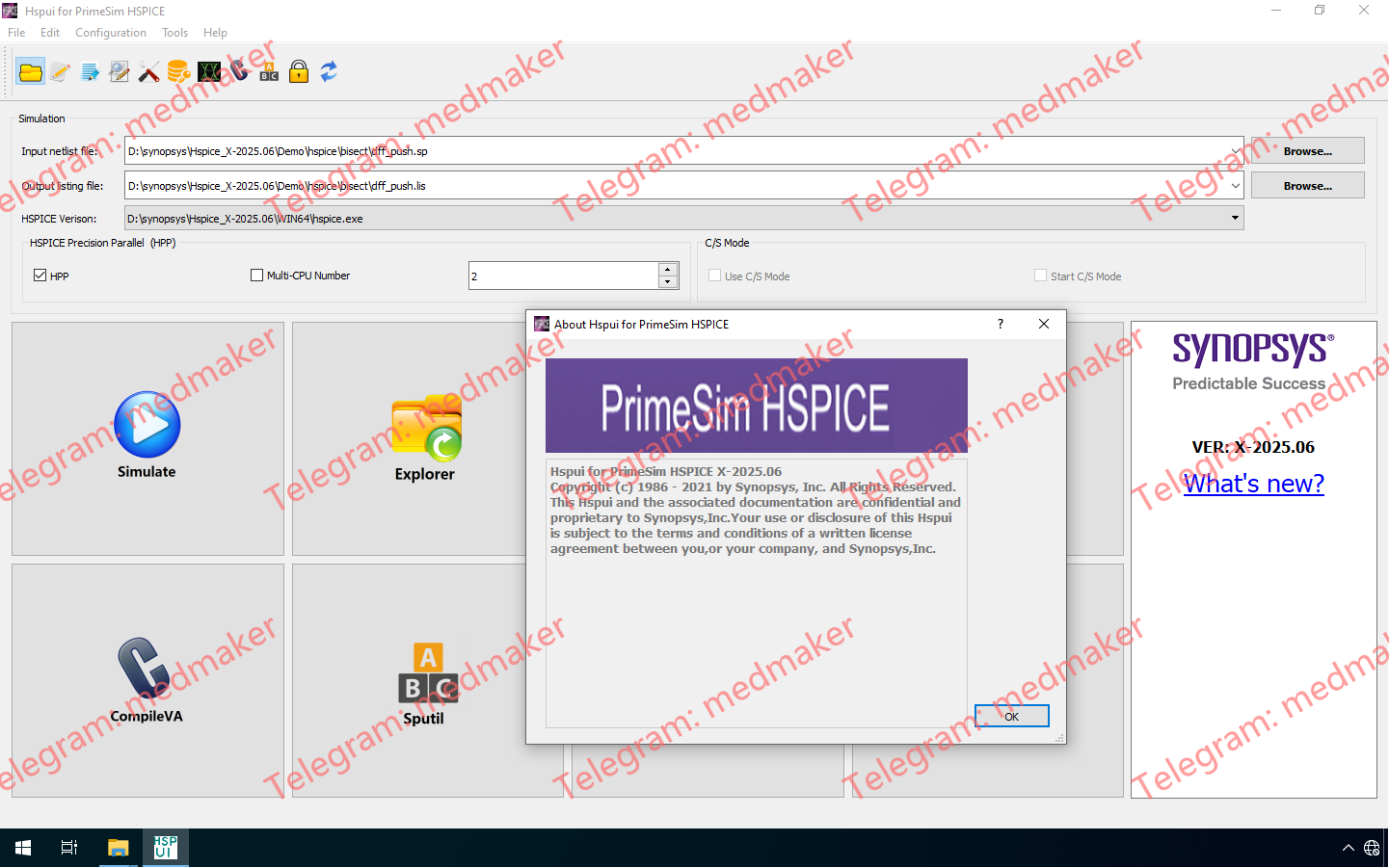

PrimeSim HSPICE is the industry’s ‘gold standard’ for accurate circuit simulation and offers foundry-certified MOS device models with state-of-the-art simulation and analysis algorithms. With extensive usage in chip/package/board/backplane signal integrity simulation, cell and memory characterization, and analog mixed signal IC design, PrimeSim HSPICE is the industry’s most popular, trusted and comprehensive circuit simulator. Available versions: 2025.x , 2024.x ,… Synopsys PrimeSim HSPICE 2025.6 Win64 Tested Picture PrimeSim™ SPICE is a high-performance SPICE circuit simulator for analog, RF, and mixed-signal applications. PrimeSim SPICE offers a unique multi-core/multi-machine scaling and heterogeneous compute acceleration on GPU/CPU delivering faster runtime with sign-off accuracy. PrimeSim SPICE supports high-frequency noise analysis, efficient S-Parameter handling while offering advanced analysis capabilities for periodic and non-periodic time-domain and frequency-domain...

QuantumATK原子尺度建模软件能够进行大规模、更逼真的材料模拟,它将从第一性原理密度泛函理论(DFT)到半经验和经典力场分析等多种模拟方法集成到一个易于使用的平台中。QuantumATK加速了半导体和材料的研发,并通过在众多高科技行业的材料筛选过程中实现更高效的工作流程,降低了时间和成本。 Available versions: 2025.x ,2024.x ,2023.x ,… Synopsys QuantumATK 2025.06 Tested Picture QuantumATK X-2025.06 版本新增功能和改进亮点包括:针对半导体行业及其他领域,针对不同原子尺度建模方法和应用的改进。 DFT 和半经验方法的 GPU 加速 体材料和 NEGF 器件计算中最耗时的部分(包括 SCF、能带结构、PDOS、PLDOS 和透射光谱)平均加速 10 倍以上。 支持多节点和多 GPU,加速倍数与 GPU 数量呈线性关系。 使用 DFT 计算 5,000 个原子或使用半经验 NEGF 计算 30,000 个原子的运行时间从数天缩短至数小时。 CPU 上的 DFT 性能改进 所有 SCF 计算速度提升约 2 倍 &使用 MetaGGA、GGA 和 Hubbard U 对中小规模体系(几百个原子)进行几何优化。 PDOS、FatBandstructure 和 MAE 分析速度提升高达约 5 倍,且速度提升幅度随投影数量的增加而增加。 更广泛的机器学习势 (MLP) 支持 用于训练新的通用 MACE 模型并针对特定体系/过程进行微调的框架,可提高精度。 用于导入、快速测试和使用基于 DeepMD、ORB、SevenNet、MACE、CHGNet 等的新兴 MLP 模型的接口。 MLP 的多 GPU 加速可实现大规模 MD 模拟,例如: 使用 MACE 模拟 100,000 个原子,使用 MTP 模拟 1,000,000 个原子。 室温扩散 模拟室温扩散和提取扩散系数的新方法: 加速集体可变超动力学 (CVHD) 比标准 MD 模拟速度提升高达 300 倍,能够捕捉罕见事件。 采用新的 Lanczos 和 ARTn 鞍点搜索方法的自适应动力学蒙特卡罗 (AKMC) 能够迭代地探测新的状态、可能的跃迁以及它们之间的能量势垒。 表面工艺模拟改进 支持沉积/蚀刻工艺中复杂的衬底形状,例如 U 形和二维材料。 采用可变时间步长的 MD 模拟,可精确模拟冲击过程。 无需在整个模拟过程中使用较小的时间步长即可实现表面过程。 改进的NEB反应势垒方法 用于在NEB中设置复杂反应路径的新型顺序IDDP方法。 改进和加速NEB反应路径优化的新技术。 将NEB与用于鞍点搜索的新型Dimer和Lanczos方法相结合,可使过渡态搜索和反应势垒计算的速度提高2-3倍。 访问QuantumATK 文档页面 有关安装指南、手册、入门教程等更多详细信息。 More Information in English:...

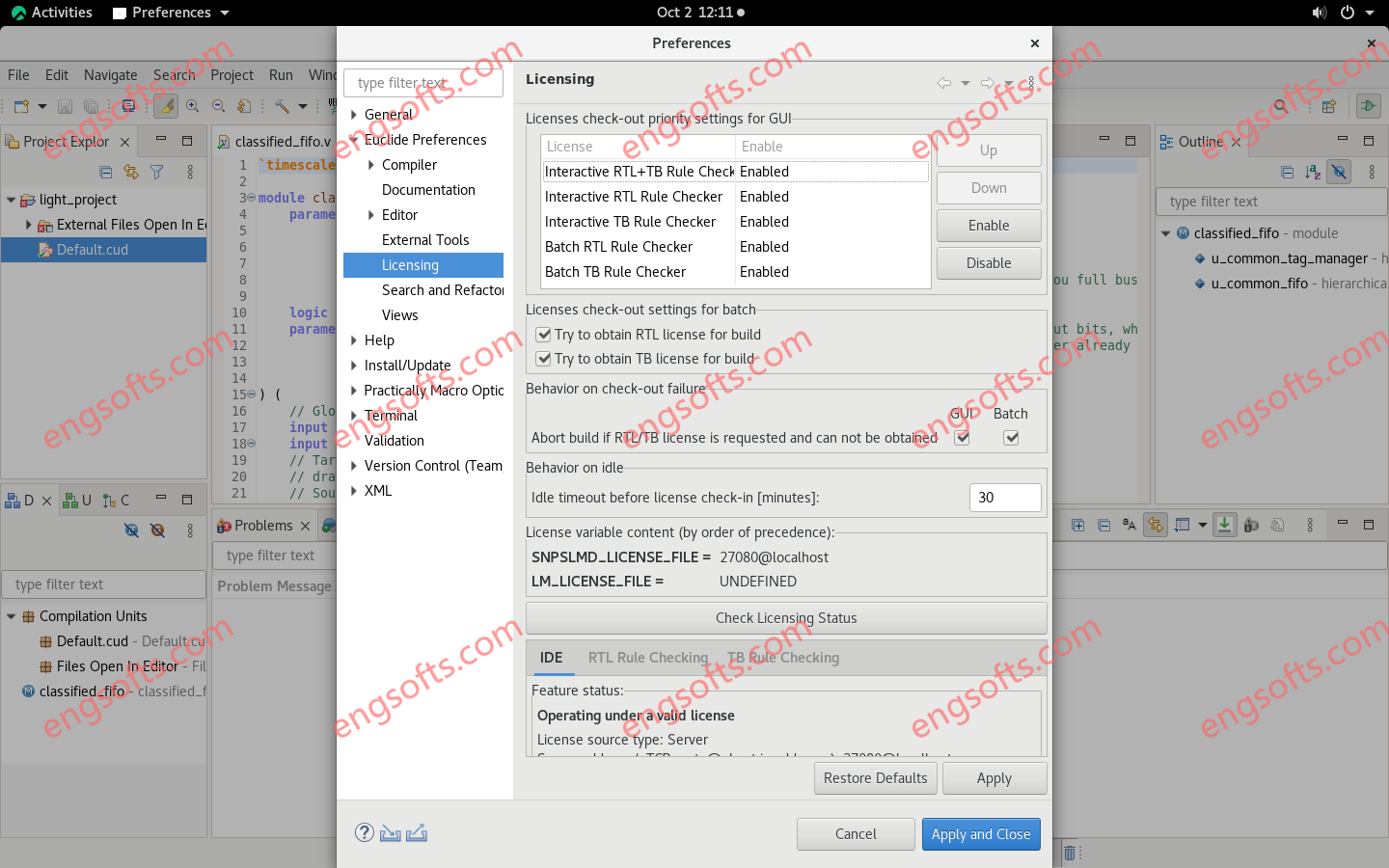

Synopsys Euclide IDE 简化了 RTL 代码编写,提供实时错误检测,并针对 SystemVerilog 和 UVM 开发中的设计和验证流程优化代码。它提供针对 Synopsys VCS 仿真和 ZeBu 仿真优化的上下文相关自动补全和内容辅助功能,从而在整个项目周期中提升代码质量。Euclide 集成了 Verdi 调试功能,可提供即时反馈,最大限度地减少实现错误并提高项目收敛速度。 可用版本: 2025.x , 2024.x , 2023.x ,… Synopsys Euclide 2025.06 Linux Tested Picture 主要优势 加速编码 提供自动补全、信号快速参考和模块实例化功能 快速检查 在编写代码的同时进行实时检查,通常只需几秒钟即可生成反馈 易于审查 轻松浏览设计和测试平台层次结构,并使用语义着色进行查看 More Information in English: Synopsys Euclide 2025.06 Linux

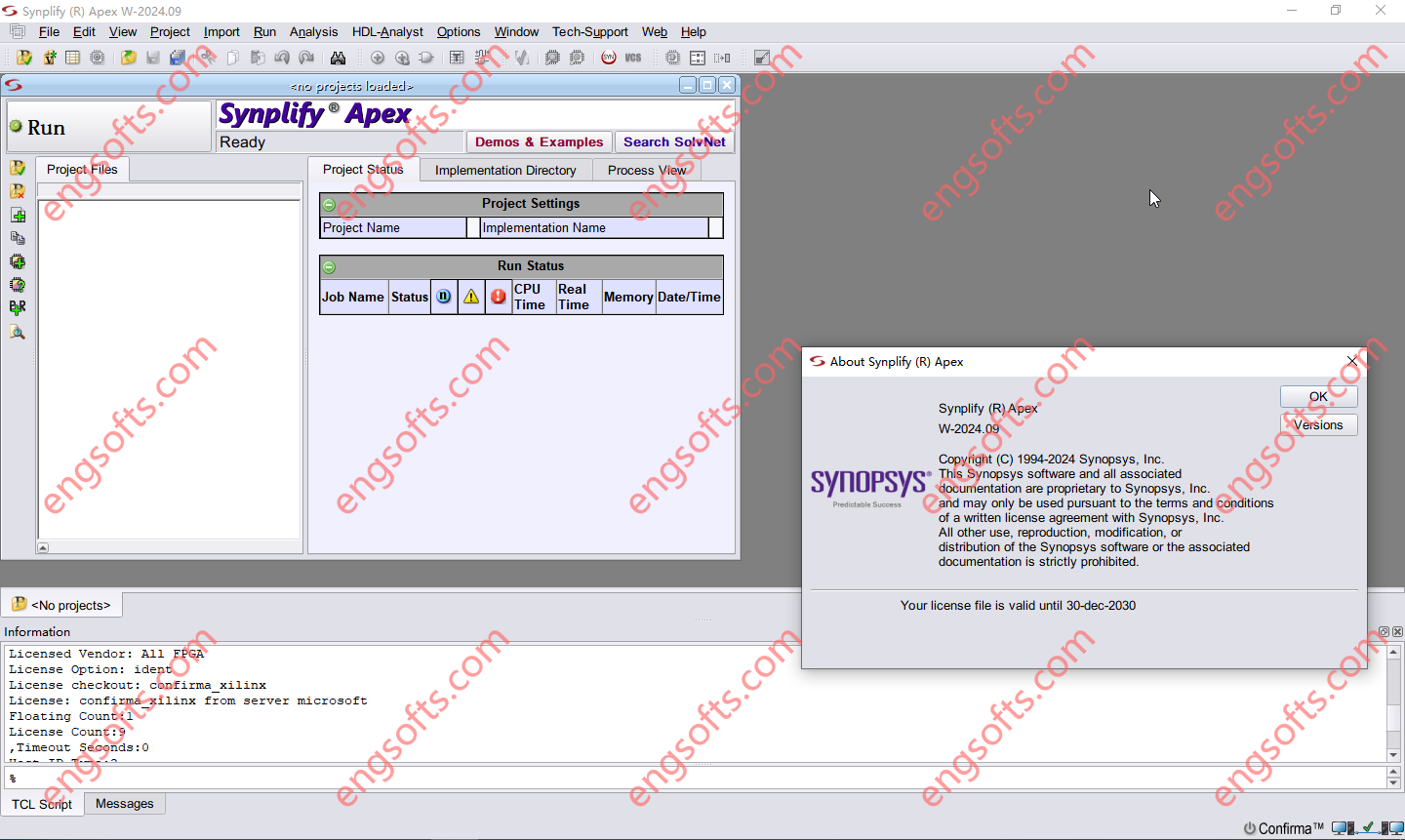

Synplify FPGA综合软件是业界公认的高性能、高性价比FPGA设计标准。Synplify软件支持最新的VHDL和Verilog语言结构,包括SystemVerilog和VHDL-2008/2019。此外,该软件还支持来自众多FPGA厂商的FPGA架构,例如Achronix、Intel、Lattice、Microsemi和AMD/Xilinx,所有架构均可通过单一的RTL和约束源进行综合。 可用版本: 2025.x ,2024.x ,2023.x ,… Synopsys Synplify FPGA 2024.09 Win/Linux64 Tested Picture 此外,Synplify 综合工具提供高性能、更快的运行速度、面积优化以降低成本和功耗,以及增量式和团队设计功能,从而加快 FPGA 设计开发速度。 它包含 TMR 和 HAMMING-3 for FSM 等功能,可自动创建高可靠性设计,例如用于医疗、汽车、工业自动化、通信、军事和航空航天等领域的设计。 Synplify 功能 高级 Verilog、SystemVerilog 和 VHDL 支持 最佳结果质量 (QoR),实现时序性能和面积/成本降低 支持高可靠性和安全关键型设计,包括 DO-254、ISO 26262 和 IEC 61508 标准 加速运行时间,运行时间最高可达 3 倍,每个许可证最多支持 8 个处理器 分布式综合,支持单机或多机应用 静态时序分析和报告,用于衡量设计性能,并进行反向注释,以关联布局布线后的性能。 集成 Identify RTL 调试器,可快速查找功能错误 故障注入和调试支持,用于衡量安全性和高可靠性特性的有效性 HDL Analyst 交互式图形分析和调试工具用于设计诊断、问题隔离以及功能和性能分析 通过 HDL Analyst 和分层调试流程进行高级设计调试和诊断 FSM Compiler 和 FSM Explorer 用于从 RTL 中自动提取和优化有限状态机 与 VCS® 和 Verdi 集成 支持脚本和 Tcl/Find,用于流程自动化以及可自定义的综合、调试和报告 More Information in English: Synopsys Synplify FPGA 2025.03 SP1 Win/Linux64

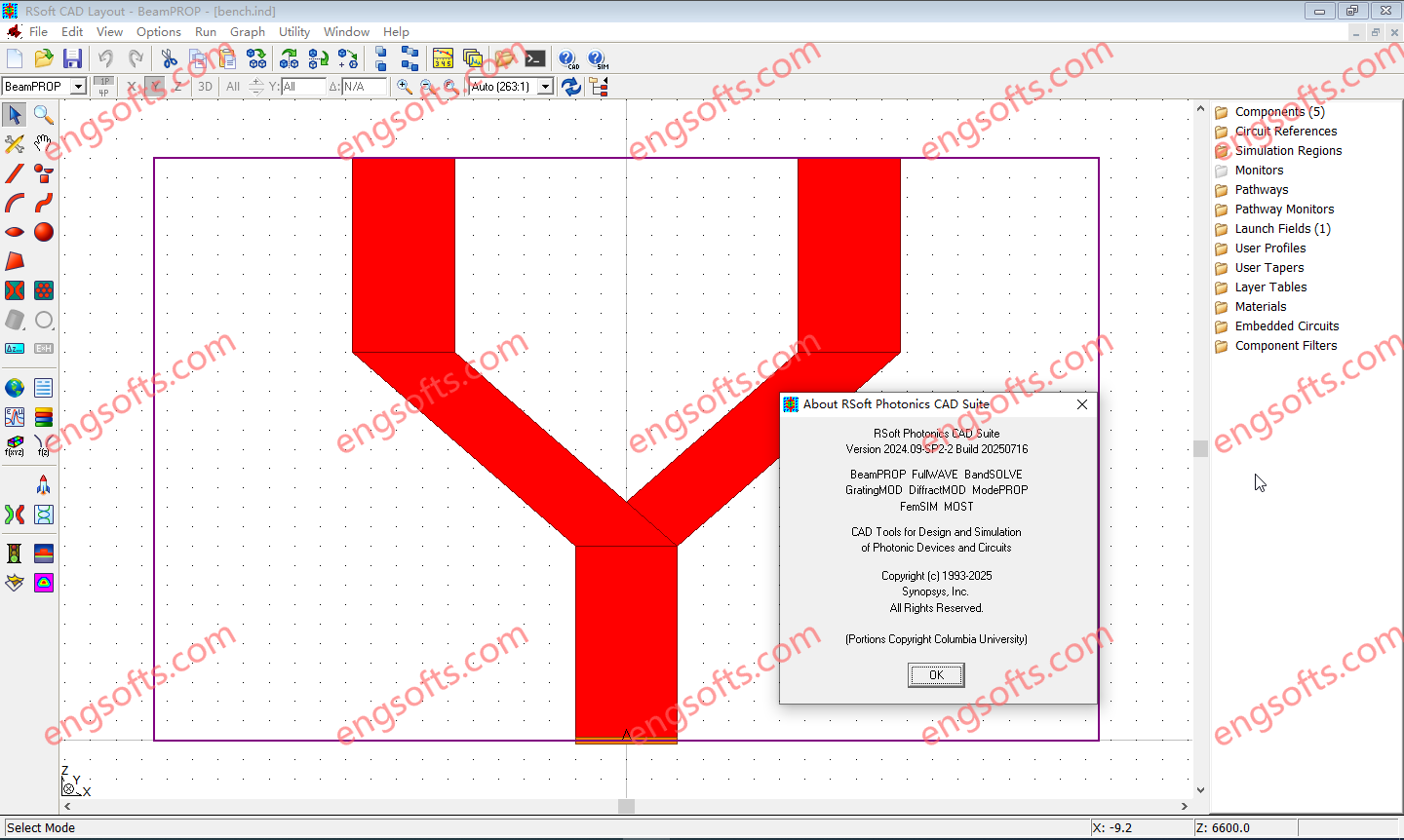

Synopsys 正在通过无缝、统一的设计平台加速光子 IC 技术的应用,帮助 IC 设计师和光子工程师在各种硅光子和光纤应用中进行创新并取得成功。借助 Synopsys 解决方案,设计团队可以使用业界领先的电子和光子设计软件,从而提高生产效率、精度并加快产品上市速度。 Synopsys 光子解决方案包括:光子集成电路(Linux64 下的 Synopsys OptoCompiler)、光子系统(Synopsys OptSim)和光子器件(RSoft 光子器件工具)。 RSoft 光子器件工具包含业界最全面的被动和主动光子及光电器件(包括激光器和垂直腔面发射激光器)仿真器和优化器产品组合。 RSoft 光子器件工具包含 FullWAVE FDTD、BeamPROP BPM、DiffractMOD RCWA、FemSIM FEM、BandSOLVE、GratingMOD、RSoft CAD、LaserMOD、MetaOptic Designer 以及各种实用程序和选项。 Synopsys RSoft Photonic Device Tools 2024.09 Tested Picture Synopsys OptSim 允许用户在信号传播层面设计和模拟当前和下一代光通信系统。 Synopsys OptSim 2024.09 Tested Picture 我们与 Synopsys 的光学和半导体设计工具集成,可实现简化的多域协同仿真: Synopsys CODE V 和 LightTools 产品,用于对纳米纹理光学结构进行严格建模和衍射分析 Synopsys Sentaurus TCAD 产品,用于对复杂光电器件进行仿真 这些先进的工具增强并加速了用户的建模能力,并利用广泛的行业规范提供真实的现场设计场景。我们的用户包括光学元件和设备制造商、系统集成商、服务提供商,以及政府实验室和学术机构。无论您是希望最大限度地提高性能、最大限度地降低成本、缩短产品上市时间、快速原型制作,还是分析光通信系统的多种“假设”场景,这些工具都将成为您不可或缺的合作伙伴,并助您取得成功。 Synopsys OptoCompiler 是业界首个统一的电子和光子设计平台,它将成熟且专用的光子技术与 Synopsys 久经考验的电子设计工具相结合,使工程师能够快速准确地生成和验证复杂的 PIC 设计。 Synopsys OptoCompiler 在单一平台上提供原理图驱动的布局和高级光子布局综合功能,弥合了光子专家和 IC 设计师之间的鸿沟,使光子设计与数字设计一样高效。 RSoft 光子器件工具 2024.09 版本新增功能 More Information in English: Synopsys RSoft Photonic Solutions 2024.09 Win/Linux64

ImSym – Imaging System Simulator, a groundbreaking virtual prototyping platform for imaging systems, encompassing lenses, sensors, and image signal processors (ISPs). By integrating components of the imaging chain into a comprehensive end-to-end simulation platform, ImSym enables tailored optimizations of any imaging system, facilitates team collaboration, and dramatically reduces the risks of issues in later development stages. With accuracy powered by industry-proven CODE V® and LightTools® optical design software and a quantitative end-to-end simulation flow, ImSym reduces the need for physical prototypes and delivers simulations that can directly translate into production-ready designs. Synopsys ImSym 2024.09 Tested Picture Enhance Your Optical System Development with ImSym Visualize images with precise, quantitative data Streamline your development process Deliver your next great imaging product to...

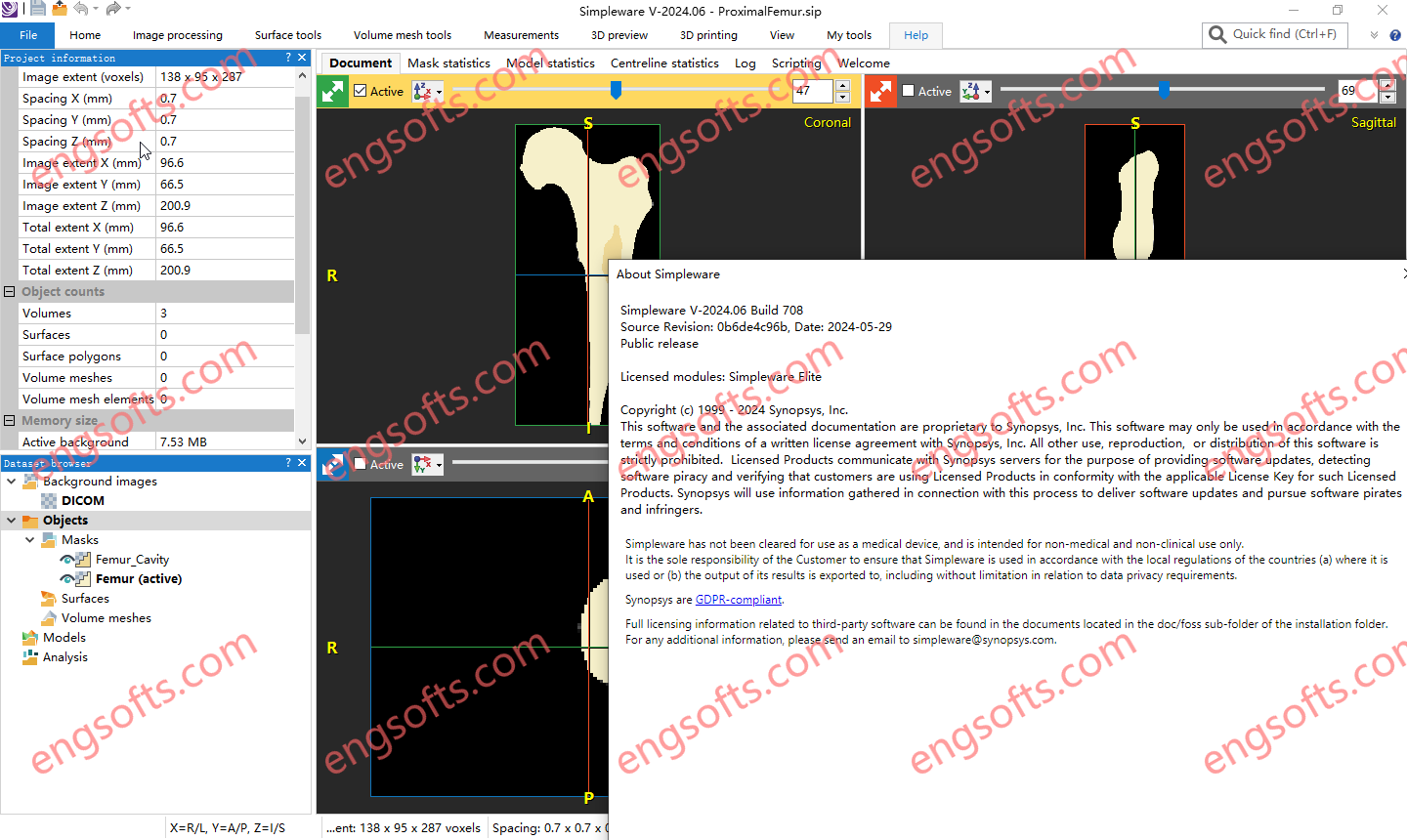

Simpleware X-2025.06 continues to push the boundaries of user-generated automation and efficiency in design. This update expands our compatibility with third-party AI tools, now including nnU-Net models and full MONAI bundle support. Easily import your own library of CAD/STL design files to quickly check designs against anatomical structures. Enhance productivity with improvements to our off-the-shelf AI-enabled Auto Segmentation tools and boost efficiency with the improved folder structure in the Dataset Browser. Available versions: 2024.x , 2023.x , 2022.x ,… Synopsys Simpleware 2024.06 Tested Picture What’s New in Version X-2025.06 ‘External AI Models’: nnU-Net and Full MONAI Inference Routine Support Added Import and run externally trained AI segmentation models using nnU-Net. Effortlessly import your model – contact us to get started!...

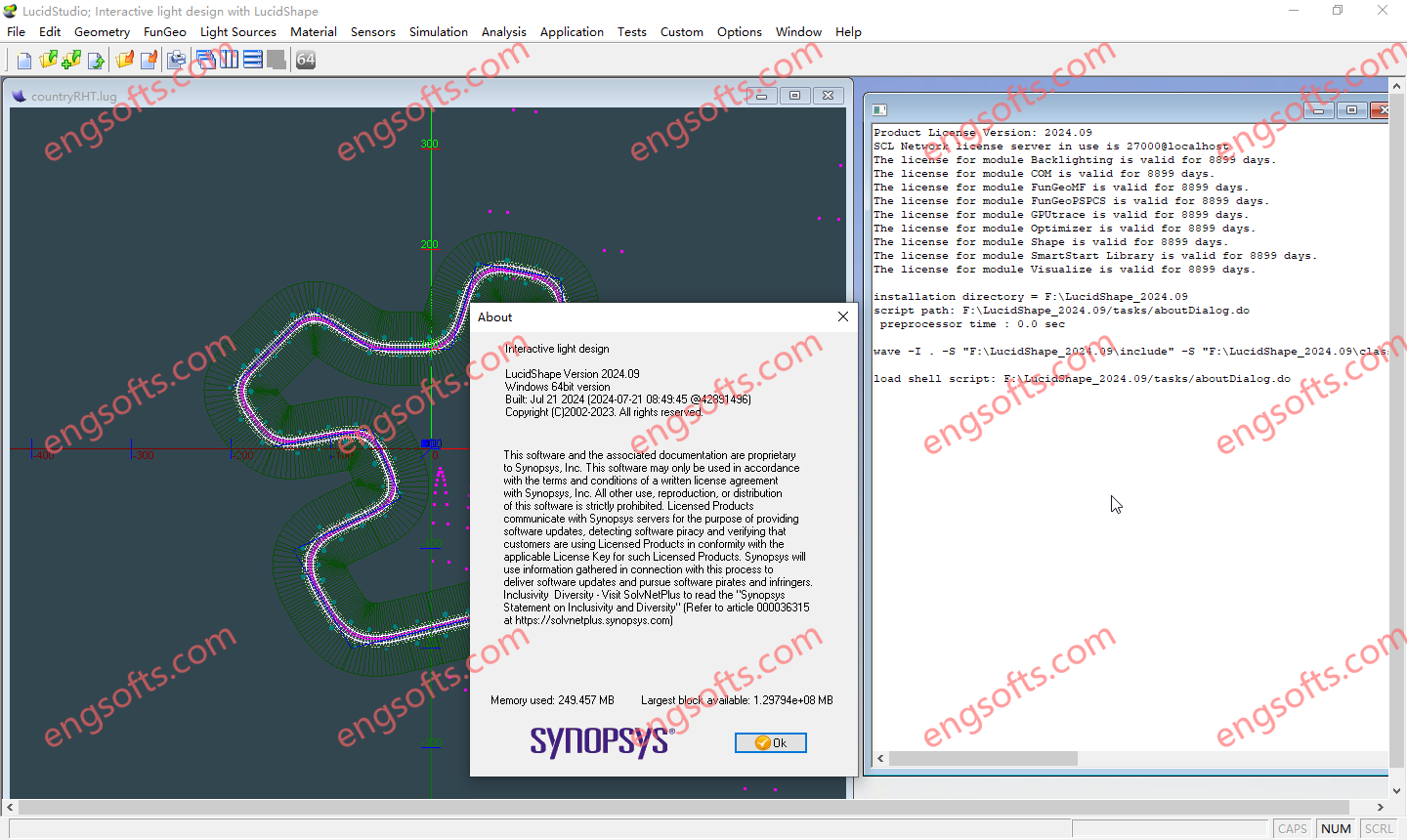

LucidShape is an intelligent 3D CAD system for optical engineers. Bring your exterior lighting products to market ahead of your competitors. Available versions: 2024.x , 2023.x ,… Synopsys LucidShape 2024.09 Tested Picture The LucidShape 2024.09 release includes many new features to advance automotive lighting design: Creation of Micro Lens Masks: Micro-Lens-Arrays are used in projection systems for icon projection for both, interior and exterior automotive lighting applications. For an optical engineer, the illumination design task is to find a suitable mask geometry to achieve the desired illumination distribution. To alleviate this burden on the user, we have automated the mask computation process. New ways to generate small facets using the MacroFocal tools: Design trends are creating lenses with thousands and...