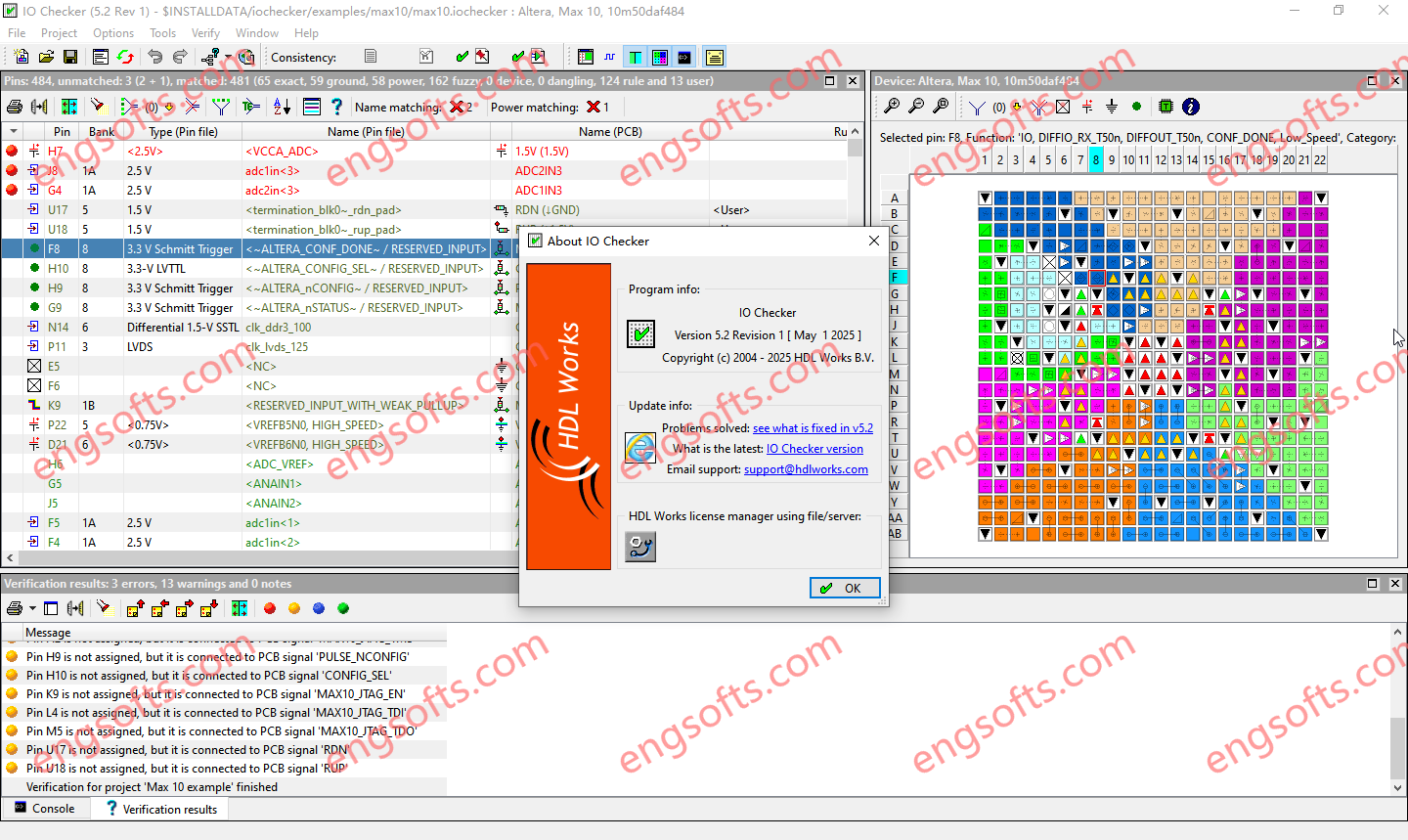

HDL Works IO Checker 5.2 Rev4 Win/Linux

IO Checker 使用基于正则表达式的规则来匹配 FPGA 和 PCB 设计环境中的信号名称。即使单个信号可能存在差异,该工具也能验证匹配组。这些规则可以自动生成,也可以由设计人员进行微调。自动化方法通常可以匹配 80% 到 90% 的器件引脚。 可用版本: 5.2.x , 5.1.x ,… HDL Works IO Checker 5.2 Rev1 Win/Linux IO Checker 的灵活性使其可用于任何设计流程,无需任何设计方法论。规则生成器结合排序后的问题视图,使工程师能够在半小时内验证一个拥有 1000 多个引脚的器件。 一旦定义了项目及其规则,保持 FPGA 和 PCB 数据的一致性就变得非常简单。所有过期的文件都会一次性处理,并且所有更改都会被报告。 功能与优势 使用正则表达式比较 FPGA 和 PCB 引脚名称 创建 &更新 FPGA 约束文件 自动生成规则 电源引脚电压检查 用户可自行确认已验证的差异 一键验证和一致性检查 报告引脚列表和网络列表中的增量更改 专注于十几个差异,而不是上千行代码 适用于任何设计流程 HTML 报告 What is new in the 5.2 release More Information in English: HDL Works IO Checker 5.2