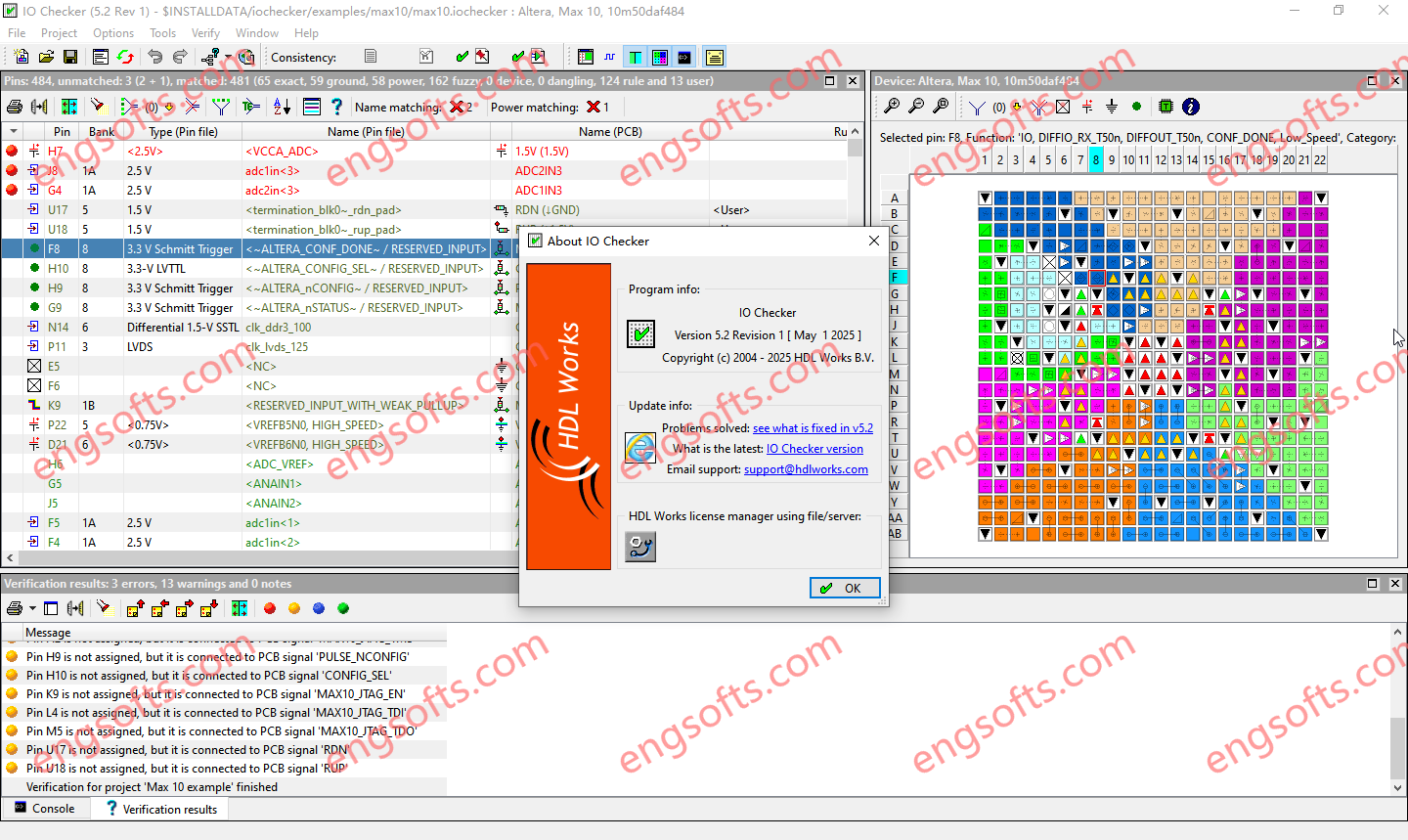

IO Checker 使用基于正则表达式的规则来匹配 FPGA 和 PCB 设计环境中的信号名称。即使单个信号可能存在差异,该工具也能验证匹配组。这些规则可以自动生成,也可以由设计人员进行微调。自动化方法通常可以匹配 80% 到 90% 的器件引脚。 可用版本: 5.2.x , 5.1.x ,… HDL Works IO Checker 5.2 Rev1 Win/Linux IO Checker 的灵活性使其可用于任何设计流程,无需任何设计方法论。规则生成器结合排序后的问题视图,使工程师能够在半小时内验证一个拥有 1000 多个引脚的器件。 一旦定义了项目及其规则,保持 FPGA 和 PCB 数据的一致性就变得非常简单。所有过期的文件都会一次性处理,并且所有更改都会被报告。 功能与优势 使用正则表达式比较 FPGA 和 PCB 引脚名称 创建 &更新 FPGA 约束文件 自动生成规则 电源引脚电压检查 用户可自行确认已验证的差异 一键验证和一致性检查 报告引脚列表和网络列表中的增量更改 专注于十几个差异,而不是上千行代码 适用于任何设计流程 HTML 报告 What is new in the 5.2 release More Information in English: HDL Works IO Checker 5.2

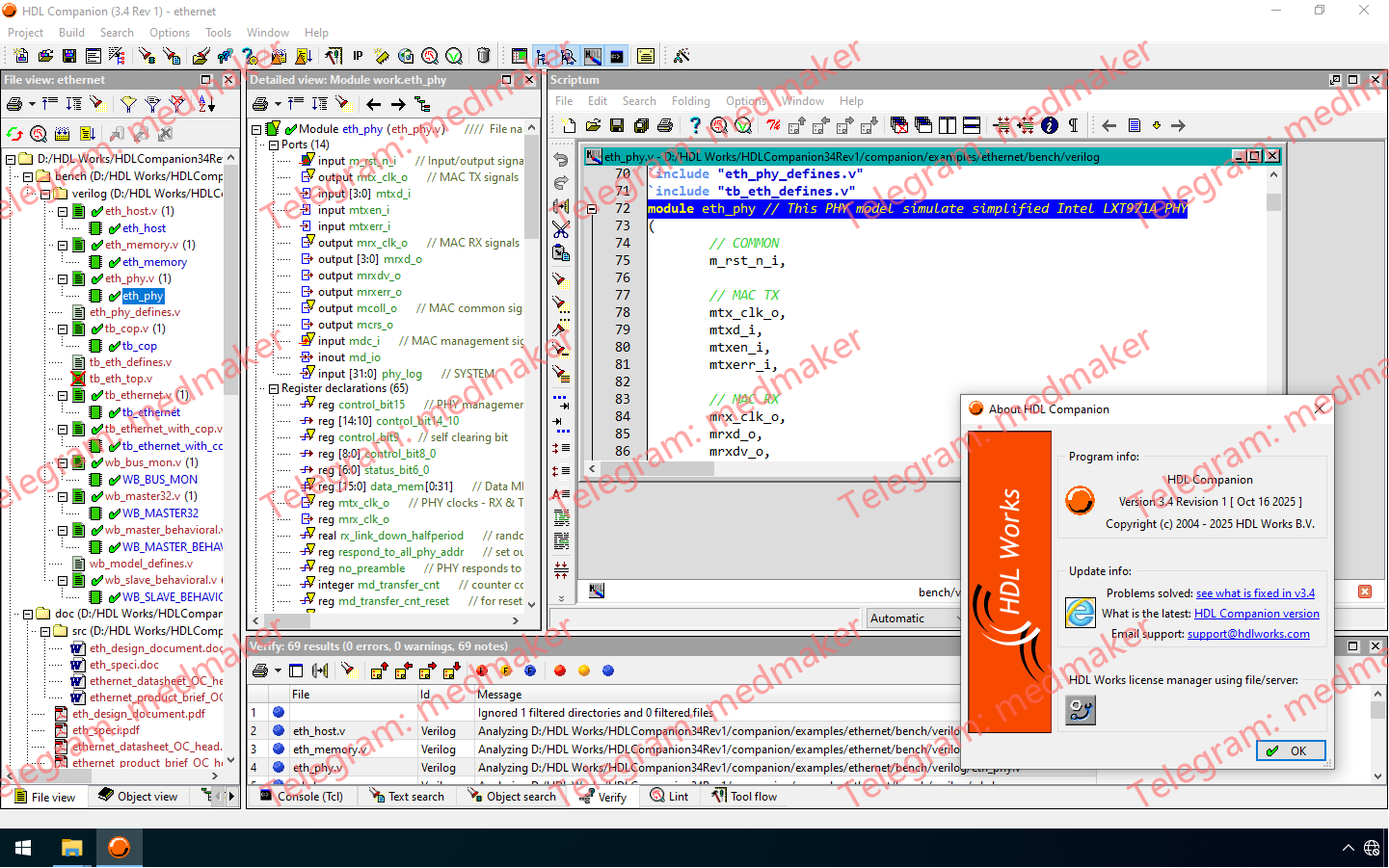

HDL Companion 是 HDL 设计师的瑞士军刀。它能帮助您快速掌握并维护任何 HDL 设计的概览,包括第三方 IP、遗留代码和其他 HDL 源文件。只需将完整的设计目录和设计文件拖入 HDL Companion,即可在几秒钟内生成完整的设计概览,揭示设计的各个方面。其图形用户界面 (GUI) 提供了多种导航方式,方便您浏览设计并查找所需细节。 可用版本: 3.4.x , 3.3.x ,… HDL Works HDL Companion 3.4 Rev1 Win/Linux Tested Picture 内置的模糊解析器可以接受任何 SystemVerilog、VHDL 或混合 HDL 设计代码;即使代码不完整或包含错误。语法正确的 HDL 代码也可以进行代码检查,以发现编译器未报告的问题。 HDL Companion 采用独特的布局,包含三个主窗口和一个控制台窗口,它们共同提供从高层结构到源代码细节的完整设计概览。其出色的导航功能(包括信号跟踪)使您可以轻松查找对象并查看其详细信息。 控制台窗口显示所有语法错误和警告,您可以使用从控制台窗口到 Scriptum 窗口的热链接轻松地在 HDL 源代码中找到它们。控制台窗口还可以用作 Tcl 解释器,可以在其中执行任何 Tcl 脚本或 shell 命令。 What is new in 3.4 More Information in English: HDL Works HDL Companion 3.4

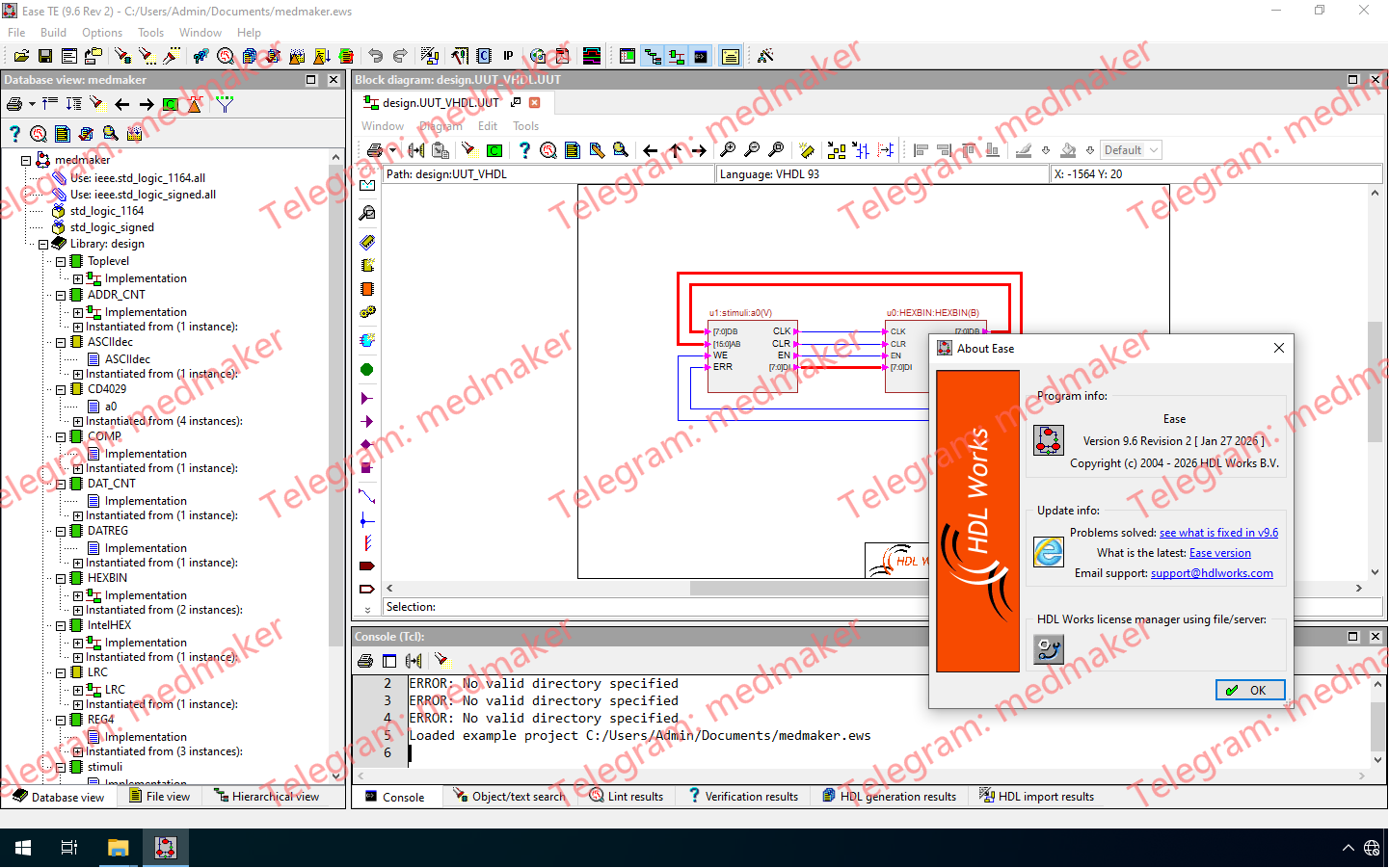

EASE 兼具图形化和文本化两种 HDL 输入方式,让您可以自由选择。您无需精通 Verilog 或 VHDL。创建新设计时,只需使用图形和文本混合方式输入即可。EASE 会自动为您生成所选语言(VHDL 或 Verilog)的优化 HDL 代码。行业标准的版本控制环境可处理设计和配置管理,支持多个用户同时在同一个 EASE 项目中工作。 可用版本: 9.6.x , 9.5.x ,… HDL Works EASE 9.6 Rev2 Win/Linux Tested Picture 功能与优势 图形化设计环境,可自动生成分层 VHDL 或 Verilog 代码 符合以下标准: – VHDL:IEEE-1076 87、93 等2008 – Verilog:IEEE-1364 95、2001、2005 – SystemVerilog:IEEE-2005、2009、2012、2017 虚拟记录可降低图表复杂性并提高灵活性 真正的多用户设计环境和相关的版本控制,由功能强大的设计环境浏览器管理 一键导入旧版 Verilog 或 VHDL 设计并提取图形层次结构 与业界最流行的仿真器和综合工具无缝集成 平台无关的数据库 集成 HDL 语言编辑器 实时错误报告 What is new in the 9.6 release More Information in English: HDL Works EASE 9.6

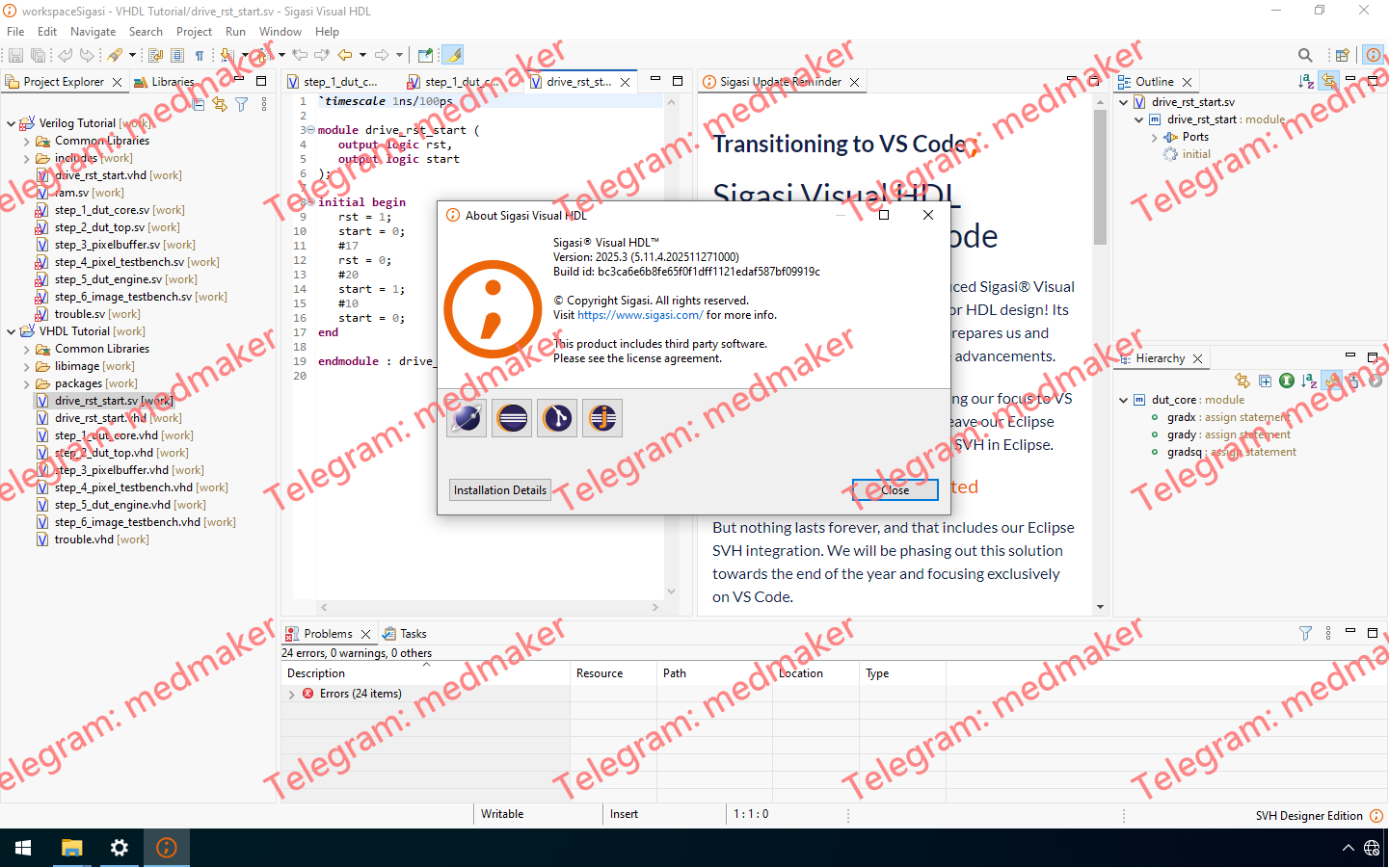

Sigasi Visual HDL (SVH) 2025.3 版本新增了 Sigasi 视图,并改进了许可证管理、状态机可视化和case 语句代码检查功能,同时还为命令行界面 (CLI) 提供了多文件格式化功能,以及编译配置导出和工具驱动的 Sigasi 项目功能。 可用版本: 2025.x , 2024.x , … Sigasi Visual HDL Enterprise Edition 2025.3 Tested Picture 我们正在扩展代码提示(Code Lenses)的功能。它们允许您打开状态机图、将未映射的文件添加到项目中、导出文档以及导出编译顺序。此外,现在可以单独启用和禁用代码提示。 我们还引入了代码提示的一种变体——内嵌提示(Inlay Hints)。它们与代码提示的功能相同——提供额外的上下文操作或信息——但它们显示在代码行内,而不是代码上方的一行。 自上而下探索您的设计或测试平台从未如此简单。全新的顶级选择器(Top Level Pickers)使您可以轻松列出并选择正确的顶级设计单元或根 UVM 组件。 对于 VHDL,我们添加了一条新的代码检查规则来检测冗余的复位信号,以完善我们现有的复位分析功能。 新的语义标记(Semantic Tokens)使您的代码高亮显示更加精细。这些标记完全可自定义,让您可以打造真正属于自己的主题。 此外,此版本还包含 Sigasi Visual HDL 2025.3 的50 多项错误修复和其他改进。 More for English: Sigasi Visual HDL Enterprise Edition 2025.3