The coreConsultant tool guides core integrators through the automated installation, configuration, and synthesis of single reusable synthesizable components.

The coreAssembler tool allows core integrators to assemble multiple components into a subsystem. The tool provides reliable, error-free subsystem netlist generation, design configuration and high-quality synthesis of the subsystem. It also provides auto-connection, egister map generation, testbench generation, and simple test builds for DesignWare® Library components.

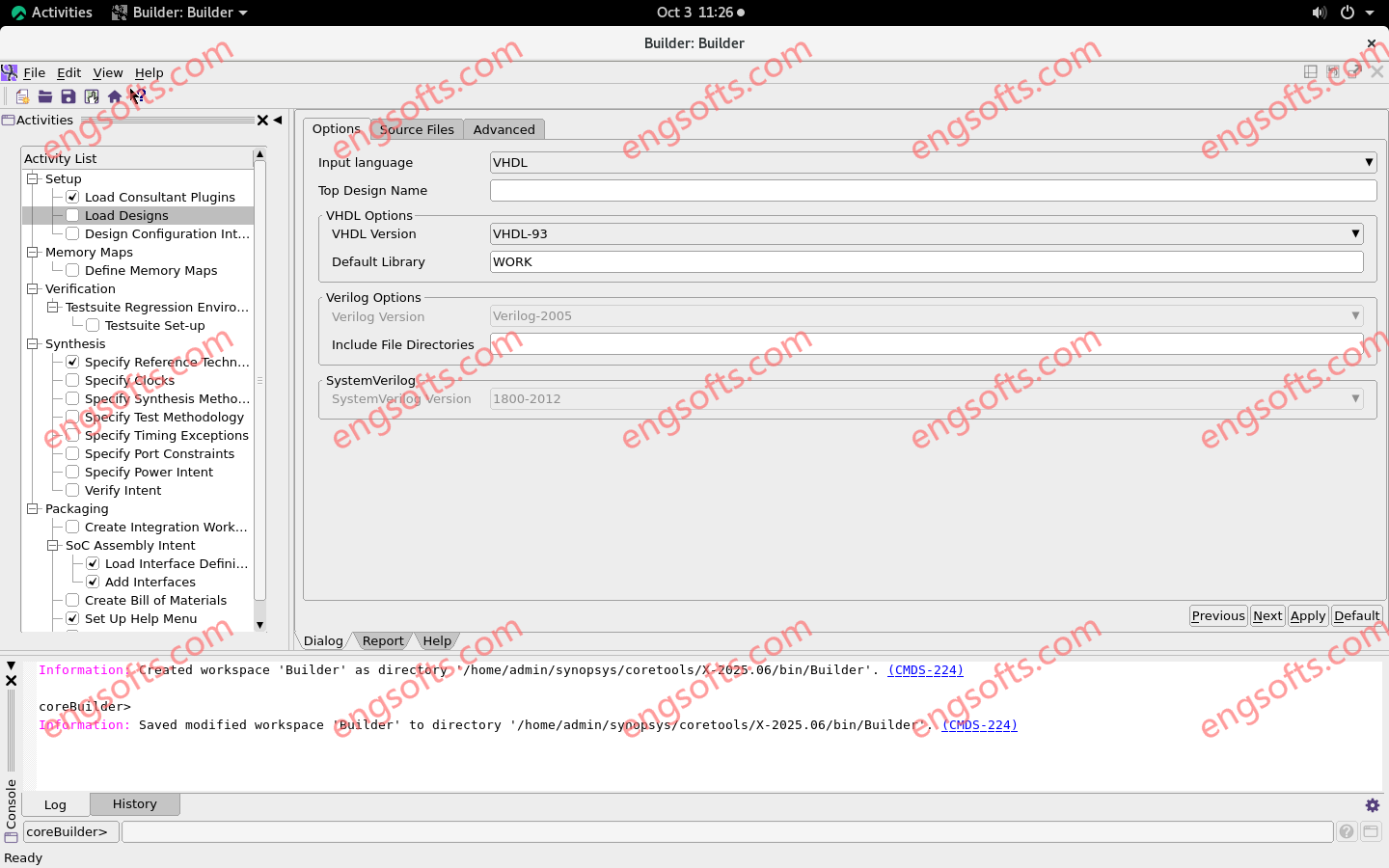

The coreBuilder tool guides the core developer through packaging a core or design for reuse with coreConsultant or coreAssembler. The coreBuilder tool captures a developer’s detailed knowledge of design characteristics and packaging requirements in a technology-independent package, enabling core integrators to easily configure and synthesize the core across a wide range of target technologies.

Available versions: 2025.x ,2024.x ,2023.x ,…

Synopsys coreTools 2025.06 Linux64 Tested Picture

What New in 2025.06

Implementation flow

- Added support for Multi-block ConstraintsVerification run in parallel using Timing Constraint Manager in coreAssembler.

- Enhanced coreAssembler to support Multi-Block and Hierarchical synthesis using RTL Architect. For more information, please consult the coreAssembler user guide.

- Updated coreAssembler to support Multi Block Constraints Verification using Timing Constraint Manager. For more information, please refer to the coreAssembler user guide.

General

- Updates to the synthesis constraint writer. Move CDC min/max delay constraints to be with the other CDC constraints instead of clock definitions. When using -use_clk_expr, application of CDC constraints is now dependent on the enable_-cdc_constraints variable defined in the variables section. Also with -use_clk_-expr, generated CDC constraints will refer to the clock variables where applicable.