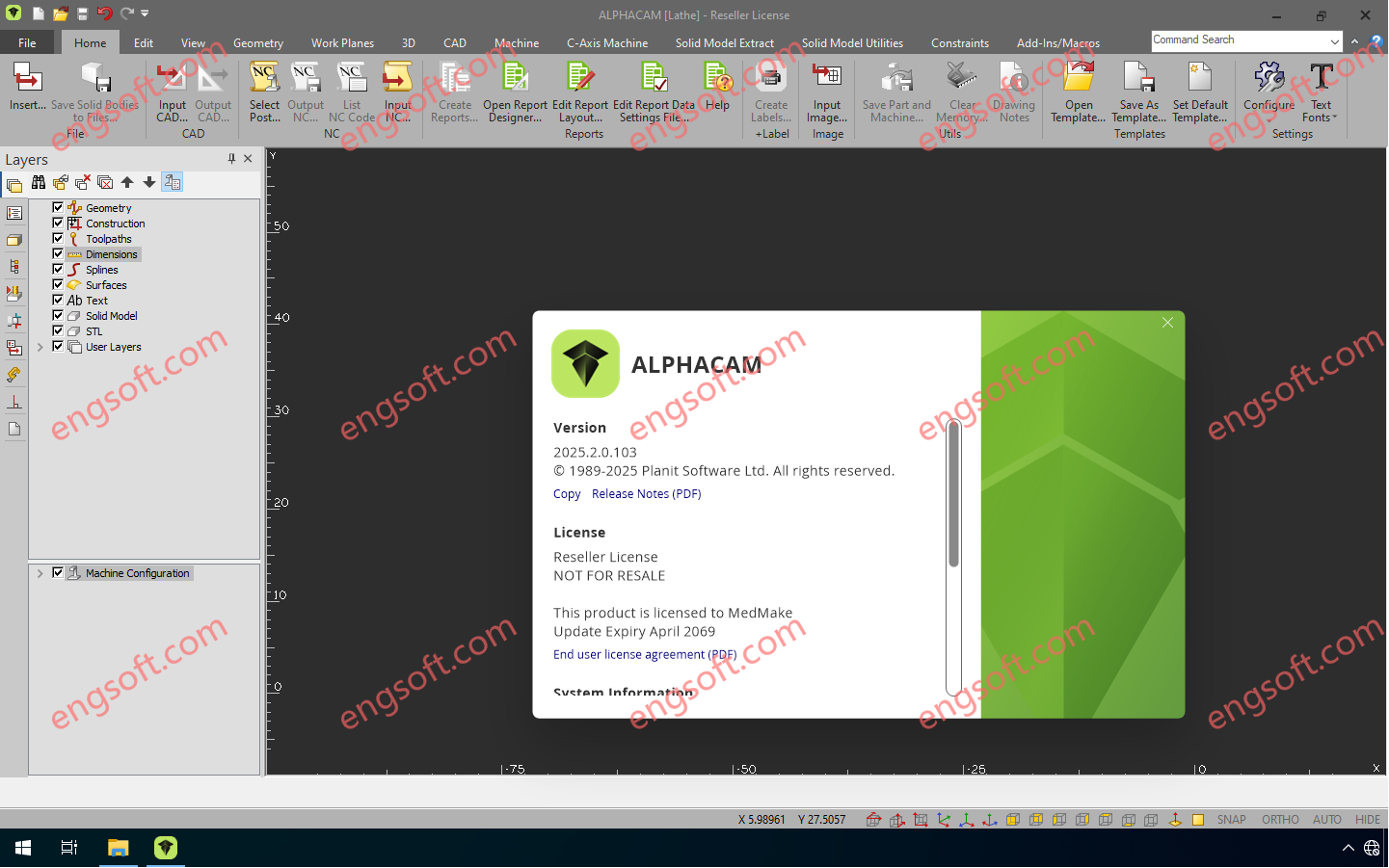

ALPHACAM is intelligent and intuitive CAD CAM software for woodworking, metal and stone cutting Available versions: 2025.x ,2024.x ,2023.x ,… Hexagon ALPHACAM 2025.2 Tested Picture ALPHACAM 2025.1: Enhanced Capabilities and Streamlined Workflows This latest release brings significant advancements focused on improving the user experience, enhancing clarity, and expanding manufacturing possibilities. Key highlights and new capabilities: GUI – Improved Solid Model Rendering Solid models are now loaded with better tolerance by default. They appear smoother with more defined edges. Benefits: Less need to constantly Refresh (CTRL + R) to regenerate the model at higher tolerances. Provides a better workflow and user experience when working with solids. GUI – Improved Display Options Includes a new Saw Display Option that provides a visual representation of the saw to scale. It indicates...

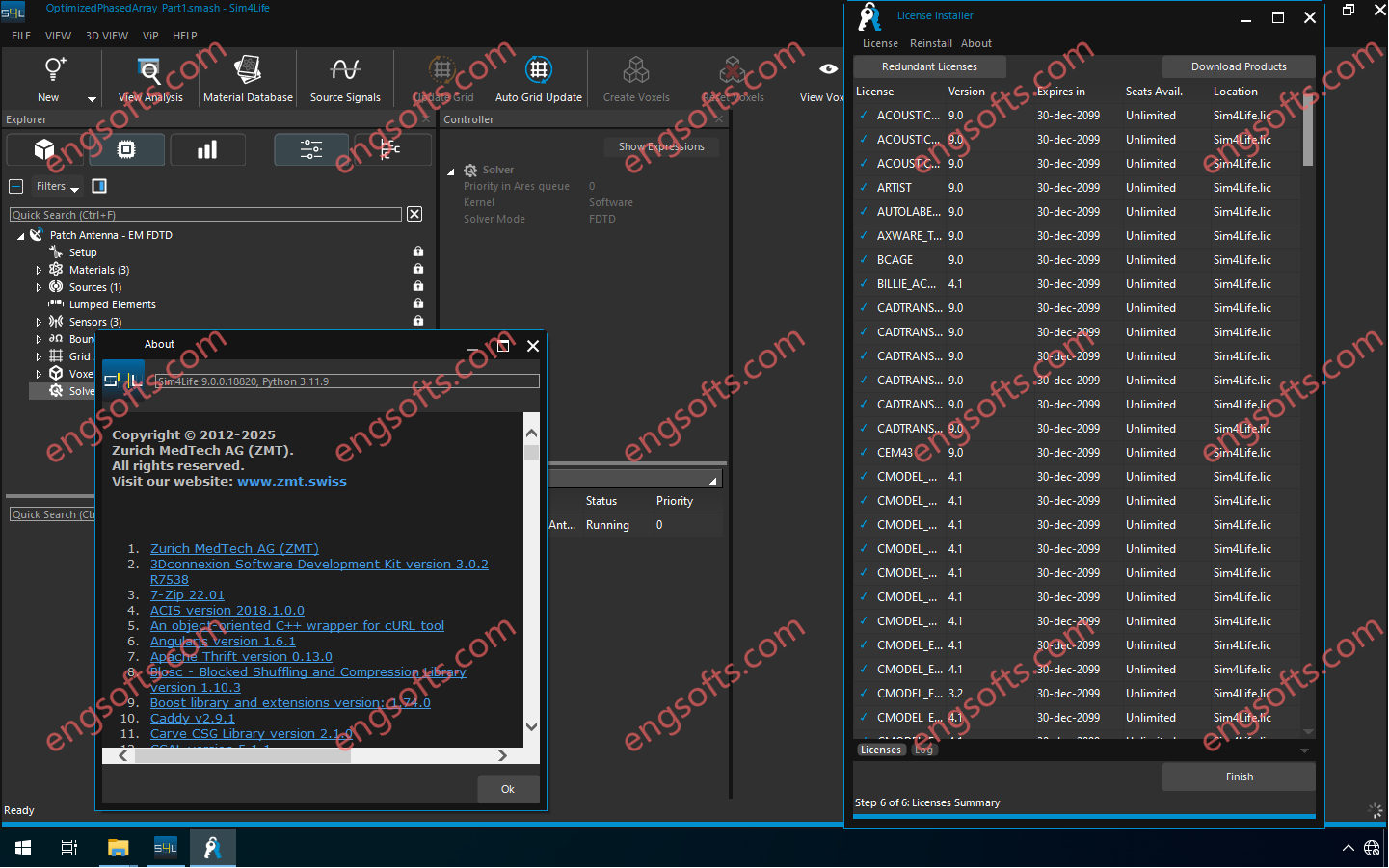

Sim4Life V9.0 的设计重点在于增强云端性能和扩展性。9.0 版本新增了优化工具、人工智能 (AI) 驱动的分割功能以及插件支持,旨在助力您在整个建模链中实现强大的自动化工作流程。Sim4Life V9.0 提供网页版和桌面版,为您的仿真工作流程带来更强大的功能、更高的灵活性和更完善的集成。 可用版本: 9.x , 8.x , 7.x ,… ZMT Sim4Life 2025 v9.0 Tested Picture V9.0 版本重大改进 统一生态系统 Sim4Life.web V9.0 现已与 o²S²PARC 平台完全集成,用户可访问由美国国立卫生研究院 (NIH) SPARC 项目开发的综合计算生态系统,该项目旨在推进生物电子医学的发展。o²S²PARC 云平台连接了健康和生命科学研究领域的专业仿真工具、数据分析流程和计算模型,从而支持复杂的跨学科工作流程,涵盖电磁建模、神经刺激分析和治疗结果预测等领域。 o²S²PARC 生态系统的变革性力量已通过多种应用得到验证,例如:基于新型卷积神经网络 (CNN) 的图像分割流程,用于个体化脊髓刺激建模 [1];通过全面的计算机模拟个性化流程实现精准的非侵入式脑刺激 [2];以及活动依赖性脊髓神经调控,用于恢复脊髓损伤导致的完全瘫痪后的运动功能 [3]。这些突破性研究表明,集成的 o²S²PARC 环境能够支持研究人员开展使用孤立且功能有限的仿真工具无法进行的研究。 第三方插件集成 全新的开放插件框架允许用户集成他们自己的或第三方仿真器和求解器,例如 FEniCS 和 SionnaRT,从而扩展支持的物理应用范围,并实现自定义工作流程,所有这些都可以在统一的界面中完成。这些插件式模拟器可以充分利用 Sim4Life 强大的建模、预处理、云计算和后处理功能。 丰富的自动化工作流程 全新的流水线和工作流程环境使用户能够构建、自动化和共享高级多阶段仿真流水线。无论是优化设备、确保合规性,还是开展基础研究,用户现在都可以以自动化的方式将应用程序连接到 Sim4Life 生态系统中的各个平台,从而进行可复现的协作研究。 云可扩展性——现在也支持桌面端 通过原生云集成,用户可以直接从 Sim4Life 桌面或 Web 界面提交和管理仿真,按需利用可扩展的中央处理器 (CPU) 和图形处理器 (GPU) 资源,并访问几乎无限的高性能计算基础设施。透明的作业跟踪、实时成本监控和一键发布功能,让您无论身在何处都能轻松管理大型项目。 高级解剖建模和人工智能工具 Sim4Life V9.0 将解剖真实性提升到了一个新的高度:虚拟人群 (ViP) 和虚拟动物园 (ViZoo) 库得到了全新升级的人工智能分割工具和头部相关建模工具(例如,自动 10-10 系统电极放置、人工智能驱动的脑和头部图谱配准等)的补充,并可从 MRI/CT 图像中自动分割躯干,从而简化模型创建过程。扩展的组织属性数据库现已包含更新的热学和含水量数据,这证明了我们持续致力于确保 Sim4Life 模拟中使用的组织材料属性保持可靠和最新。 代理模型、优化和不确定性量化预览 Sim4Life V9.0 创新的元建模框架利用了最先进的智能算法,例如来自 Dakota 项目(美国新墨西哥州阿尔伯克基市桑迪亚国家实验室)的算法,用于代理模型建模、优化和不确定性量化,并将其应用于集成仿真流程。高效的实验设计工具和先进的不确定性传播功能能够更深入地了解模型敏感性,这对于稳健的设备设计和监管申报至关重要。敬请期待:更多能够利用元建模框架的复杂工具和应用程序将在后续版本中迅速扩展! 植入物安全 IMAnalyticsSuite V1.8 引入了强大的新工具,旨在支持植入物安全评估的最新趋势。在此版本中,B1场分析功能得到增强,新增了灵活的切片和可视化功能,包括最大强度投影 (MIP) 以及可自定义的跨任意平面的B1+和B1−场视图。新增功能允许用户基于掩蔽区域计算均匀性指标(例如变异系数),并评估等中心周围特定层内的平均B1+或B1−场。因此,用户现在可以将功率沉积分析限制在满足特定B1+均匀性阈值的曝光场景中,并进行流式传输。符合不断变化的安全准则并减少高估 More Information in English: ZMT Sim4Life 2025 v9.0

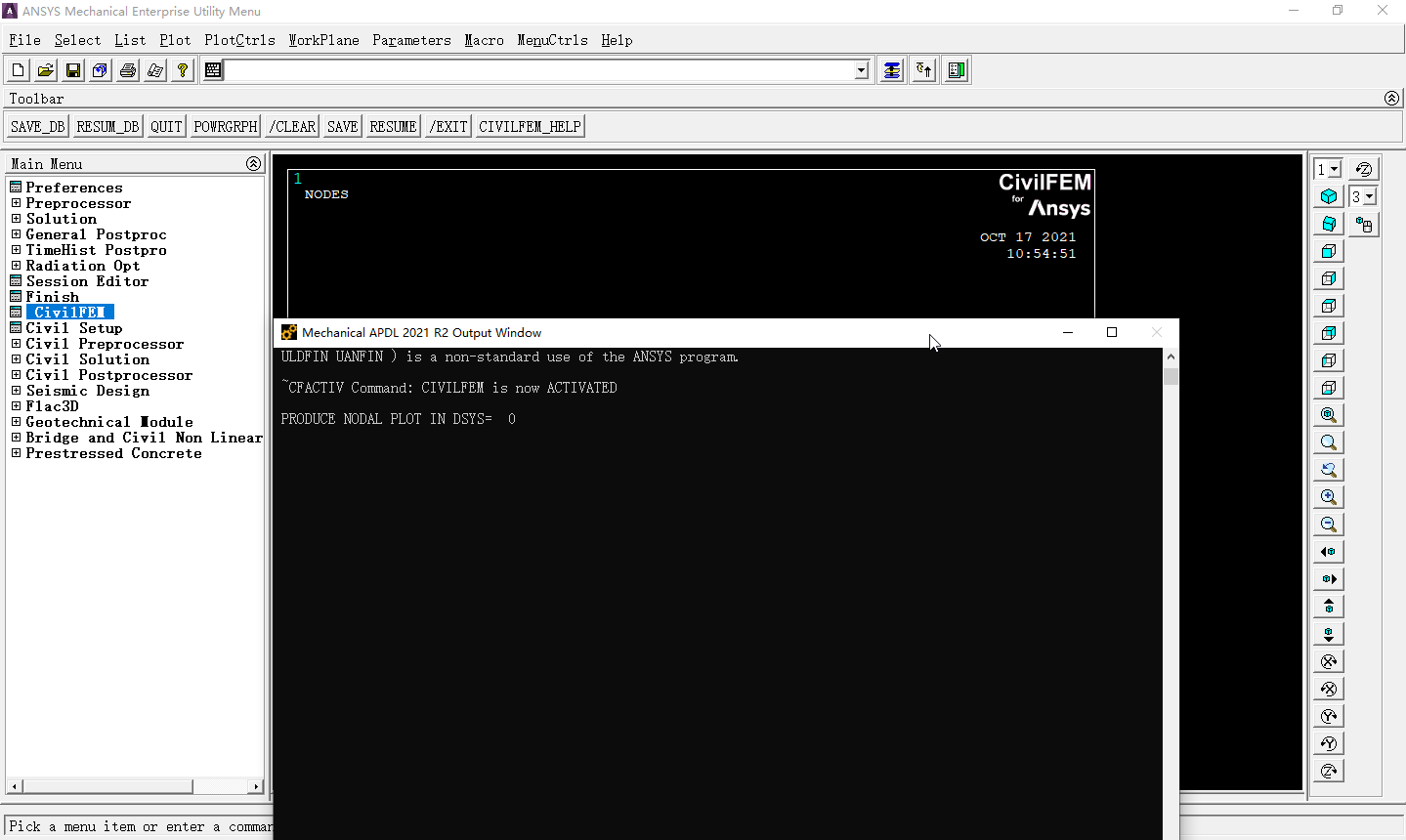

CivilFEM 支持 ANSYS 支持的所有类型的高级分析(动态、静态、线性和非线性),并可作为一款独立的软件运行。CivilFEM 采用模块化设计,由名为 CivilFEM INTRO 的通用产品和针对特定土木工程需求的专用模块组成,例如桥梁和土木非线性模块、高级预应力混凝土模块以及岩土工程模块,这些专用模块可以可选地添加到 CivilFEM INTRO 中。 可用版本: 2025.x ,2024.x ,2023.x ,… CivilFEM 2021 for ANSYS 19.x-2021 Tested Picture CivilFEM 多学科版包含了所有为 CivilFEM 开发的专业模块(入门模块、岩土模块、桥梁和土木非线性模块以及高级预应力钢筋混凝土模块),为用户提供满足其所有土木工程需求的完整解决方案。 最新版本的 CivilFEM 支持多个 ANSYS 版本。“CivilFEM 2025 for ANSYS”可与 ANSYS 2025 以及更早版本的 ANSYS(2020、2021、2022、2023、2024 和 2025)兼容运行。如果您希望 CivilFEM 支持其他 ANSYS 版本,请联系 Ingeciber。 More Information in English: CivilFEM 2025 for ANSYS 2020-2025

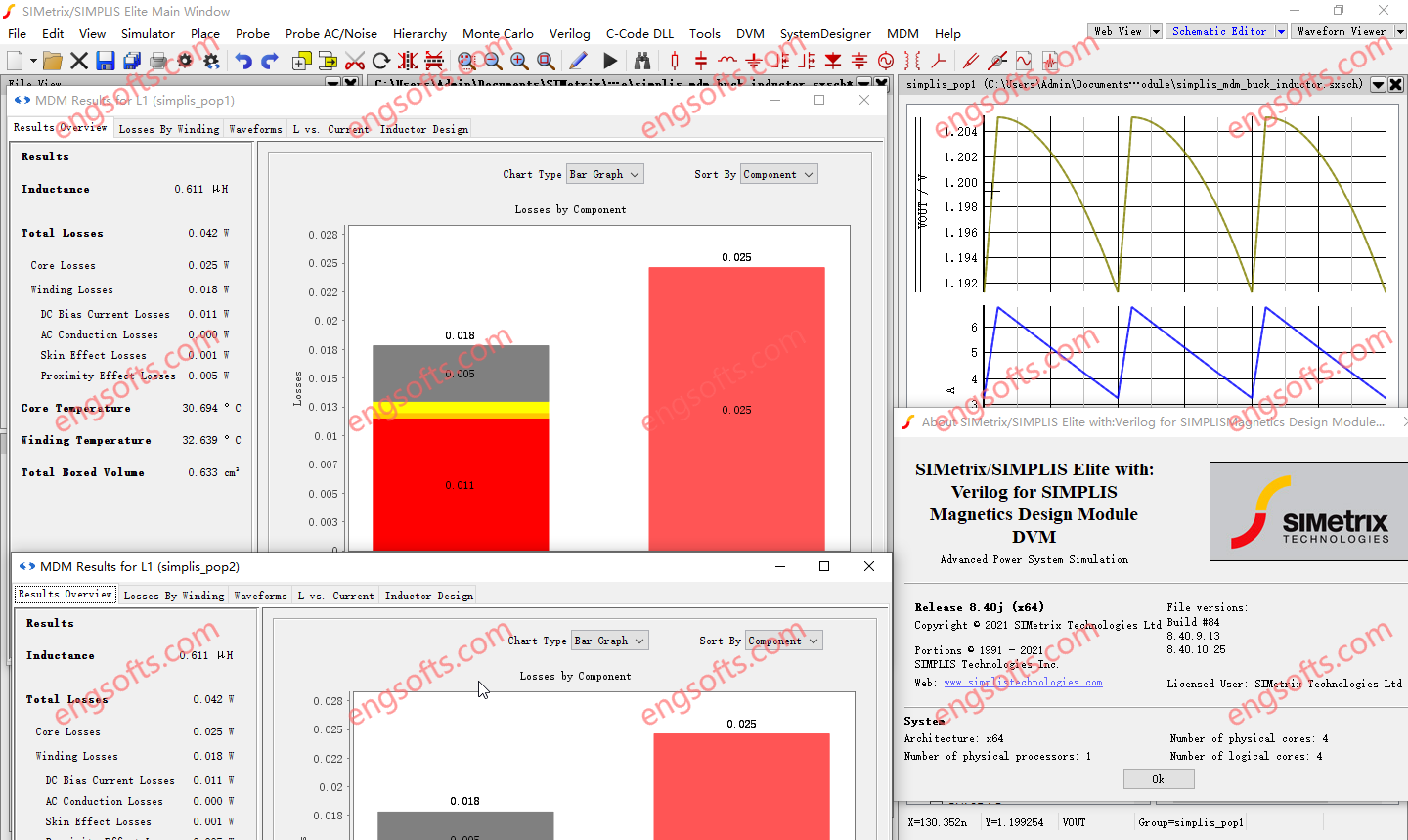

SIMetrix/SIMPLIS 是一款先进的仿真工具,专为高效设计电力电子电路而优化。SIMetrix/SIMPLIS 将精度和收敛性完美结合在一个独特而强大的设计环境中,使电源设计的仿真速度提升 10-50 倍。 可用版本: 9.x , 8.x ,… SIMetrix-SIMPLIS Elite with MDM 8.40 Tested Picture 波形查看器功能 固定探针的独立 X 轴 现在可以强制固定探针生成的曲线图具有独立的 X 轴,从而实现独立缩放。此前,只能在绘制曲线后手动设置 X 轴。 原理图编辑器功能 LTspice® 兼容性 原理图编辑器现在可以直接打开 LTspice® 原理图;只需像往常一样打开文件即可。如果所有使用的模型都受 SIMetrix 仿真器支持,则只需进行少量更改即可运行原理图仿真。 设计验证模块功能 测试计划编辑器 现在可以使用内置的测试计划编辑器创建和编辑测试计划。内置的测试计划编辑器不仅无需第三方电子表格或文本编辑器软件,还提供各种单元输入方面的帮助。这包括下拉选择列表和参数输入辅助。 除了单元格输入辅助外,测试计划编辑器还提供实时错误检查。将鼠标悬停在彩色单元格上即可获取更多信息。 测试计划向导 动态创建 DVM 测试计划,仅包含所需的目标和输入。 提供三个向导: 直流-直流 1 输入 1 输出 直流-直流 1 输入 2 输出 交流-直流 1 输入 1 输出 SIMPLIS 仿真器的新功能 变压器绕组损耗细分 使用 MDM 模拟变压器损耗时,“MDM 结果窗口”中的“变压器设计”选项卡现在提供每个绕组的详细损耗文本细分。用户现在可以查看每种类型(直流偏置、交流传导、趋肤效应和邻近效应)的绕组损耗在每个绕组中的具体数值。 MDM 数据库新增磁芯材料 MagDB 数据库新增 87 种软功率磁性材料。用户可以在 MagDB 窗口中查看这些材料的属性,也可以在 MDM 主窗口的“磁芯”选项卡中选择使用。 用户自定义磁芯损耗分析方程 在向 MDM 数据库添加新的磁芯材料或修改现有材料时,用户现在可以自定义磁芯损耗计算方程。具体操作方法是:打开 MagDB,从列表中选择一种磁芯材料,然后单击“分析方程”按钮,即可打开“磁芯损耗分析方程编辑器”。 该方程用于模拟正弦磁通激励引起的铁芯损耗,输出损耗单位为 W/m³,其输入参数包括频率(单位:Hz)、峰值磁通密度(单位:T)、温度(单位:°C)和直流偏置(单位:A/m)。用户可以使用 JavaScript 编写任意表达式,利用部分或全部输入参数来计算材料的体积铁芯损耗。一些铁芯材料制造商在其数据手册中提供了此类方程。 PFC POP 触发原理图 要启动 SIMPLIS 交流分析,必须先成功完成 SIMPLIS POP 分析。对于具有交流输入的 PFC 电路原理图,目前 POP 分析只能在非常特定的条件下才能成功,即开关频率为交流线路频率的整数倍——而许多 PFC 电路并非如此。 新型 PFC POP 触发器原理图设备可对模拟控制 PFC 整流电路的原理图进行 SIMPLIS POP 和交流分析,包括开关频率可变的电路以及开关频率并非交流线路频率整数倍的电路。 PFC POP 触发器可轻松切换交流和直流输入,并可与数字万用表 (DVM) 或电源配合使用,快速比较 PFC 在交流和直流输入下的波特图。 新增的测试功能可使 PFC POP 触发器与数字万用表 (DVM)...

Nauticus Hull is our software package for strength assessment of hull structures. It offers all the tools you need for efficient hull design and verification according to DNV Rules and IACS Common Structural Rules for bulk carriers and oil tankers (CSR BC & OT). Available versions: 20.x ,… DNV Nauticus Hull v20.30 Tested Picture Nauticus Hull v20.36 package including Rule check. Applications in group: GeniE 64 V8.12-03 NauticusHull 64 20.36.2508 Sesam Converters 64 V2.3-04 Sestra 64 V10.20-00 Submod 64 V3.3-01 NauticusHull 64 20.36.2508 Ship structural analysis and design software Complete module-based structural analysis package Efficient environment for strength assessment, design and verification Supports the latest updates of CSR BC & OT for prescriptive and Finite Element Method calculations Integrated with Sesam GeniE for...

KFX/EXSIM is specifically developed for safety-related applications, addressing scenarios such as gas dispersion, fires, explosions, and other industrial challenges. Its features include the porosity technique, Lagrangian model for droplet releases, the ability to handle multiple simultaneous releases in a single model, and seamless integration with Finite Element software for structural response analysis. Extensive usage and testing in numerous industry studies, both by DNV and external customers, have established KFX as a robust and stable simulator. Furthermore, the software has been developed in close collaboration with industry partners to best understand and address industrial needs efficiently and accurately. Notably, ongoing advancements include an advanced liquid CO2 release model that accounts for complex thermodynamics, two-phase releases, dry-ice formation and deposition, as well...

DNV Sesam Package 2025 Software suite for hydrodynamic and structural analysis of offshore wind, offshore oil and gas, and maritime structures. Available versions: 2025.x ,2024.x ,2023.x ,2022.x ,… Sesam is a software suite for hydrodynamic and structural analysis of ships and offshore structures. It is based on the displacement formulation of the finite element method. An overview of Sesam is shown below. The four groups of programs: preprocessors, hydrodynamic analysis programs, structural analysis programs and postprocessors, are bound together by a set of Sesam Interface Files and Formats, the green “H” in the figure. All major inter-program communication goes via this well-defined set of files. The exception is for Sesam Core that streams data from Sestra directly. Sesam customers can...

Synplify FPGA综合软件是业界公认的高性能、高性价比FPGA设计标准。Synplify软件支持最新的VHDL和Verilog语言结构,包括SystemVerilog和VHDL-2008/2019。此外,该软件还支持来自众多FPGA厂商的FPGA架构,例如Achronix、Intel、Lattice、Microsemi和AMD/Xilinx,所有架构均可通过单一的RTL和约束源进行综合。 可用版本: 2025.x ,2024.x ,2023.x ,… Synopsys Synplify FPGA 2024.09 Win/Linux64 Tested Picture 此外,Synplify 综合工具提供高性能、更快的运行速度、面积优化以降低成本和功耗,以及增量式和团队设计功能,从而加快 FPGA 设计开发速度。 它包含 TMR 和 HAMMING-3 for FSM 等功能,可自动创建高可靠性设计,例如用于医疗、汽车、工业自动化、通信、军事和航空航天等领域的设计。 Synplify 功能 高级 Verilog、SystemVerilog 和 VHDL 支持 最佳结果质量 (QoR),实现时序性能和面积/成本降低 支持高可靠性和安全关键型设计,包括 DO-254、ISO 26262 和 IEC 61508 标准 加速运行时间,运行时间最高可达 3 倍,每个许可证最多支持 8 个处理器 分布式综合,支持单机或多机应用 静态时序分析和报告,用于衡量设计性能,并进行反向注释,以关联布局布线后的性能。 集成 Identify RTL 调试器,可快速查找功能错误 故障注入和调试支持,用于衡量安全性和高可靠性特性的有效性 HDL Analyst 交互式图形分析和调试工具用于设计诊断、问题隔离以及功能和性能分析 通过 HDL Analyst 和分层调试流程进行高级设计调试和诊断 FSM Compiler 和 FSM Explorer 用于从 RTL 中自动提取和优化有限状态机 与 VCS® 和 Verdi 集成 支持脚本和 Tcl/Find,用于流程自动化以及可自定义的综合、调试和报告 More Information in English: Synopsys Synplify FPGA 2025.03 SP1 Win/Linux64

Synopsys 正在通过无缝、统一的设计平台加速光子 IC 技术的应用,帮助 IC 设计师和光子工程师在各种硅光子和光纤应用中进行创新并取得成功。借助 Synopsys 解决方案,设计团队可以使用业界领先的电子和光子设计软件,从而提高生产效率、精度并加快产品上市速度。 Synopsys 光子解决方案包括:光子集成电路(Linux64 下的 Synopsys OptoCompiler)、光子系统(Synopsys OptSim)和光子器件(RSoft 光子器件工具)。 RSoft 光子器件工具包含业界最全面的被动和主动光子及光电器件(包括激光器和垂直腔面发射激光器)仿真器和优化器产品组合。 RSoft 光子器件工具包含 FullWAVE FDTD、BeamPROP BPM、DiffractMOD RCWA、FemSIM FEM、BandSOLVE、GratingMOD、RSoft CAD、LaserMOD、MetaOptic Designer 以及各种实用程序和选项。 Synopsys RSoft Photonic Device Tools 2024.09 Tested Picture Synopsys OptSim 允许用户在信号传播层面设计和模拟当前和下一代光通信系统。 Synopsys OptSim 2024.09 Tested Picture 我们与 Synopsys 的光学和半导体设计工具集成,可实现简化的多域协同仿真: Synopsys CODE V 和 LightTools 产品,用于对纳米纹理光学结构进行严格建模和衍射分析 Synopsys Sentaurus TCAD 产品,用于对复杂光电器件进行仿真 这些先进的工具增强并加速了用户的建模能力,并利用广泛的行业规范提供真实的现场设计场景。我们的用户包括光学元件和设备制造商、系统集成商、服务提供商,以及政府实验室和学术机构。无论您是希望最大限度地提高性能、最大限度地降低成本、缩短产品上市时间、快速原型制作,还是分析光通信系统的多种“假设”场景,这些工具都将成为您不可或缺的合作伙伴,并助您取得成功。 Synopsys OptoCompiler 是业界首个统一的电子和光子设计平台,它将成熟且专用的光子技术与 Synopsys 久经考验的电子设计工具相结合,使工程师能够快速准确地生成和验证复杂的 PIC 设计。 Synopsys OptoCompiler 在单一平台上提供原理图驱动的布局和高级光子布局综合功能,弥合了光子专家和 IC 设计师之间的鸿沟,使光子设计与数字设计一样高效。 RSoft 光子器件工具 2024.09 版本新增功能 More Information in English: Synopsys RSoft Photonic Solutions 2024.09 Win/Linux64

ImSym – Imaging System Simulator, a groundbreaking virtual prototyping platform for imaging systems, encompassing lenses, sensors, and image signal processors (ISPs). By integrating components of the imaging chain into a comprehensive end-to-end simulation platform, ImSym enables tailored optimizations of any imaging system, facilitates team collaboration, and dramatically reduces the risks of issues in later development stages. With accuracy powered by industry-proven CODE V® and LightTools® optical design software and a quantitative end-to-end simulation flow, ImSym reduces the need for physical prototypes and delivers simulations that can directly translate into production-ready designs. Synopsys ImSym 2024.09 Tested Picture Enhance Your Optical System Development with ImSym Visualize images with precise, quantitative data Streamline your development process Deliver your next great imaging product to...