EDA 第8页

Electrical & Power Engineering softwares.

Arteris IP created the new technologies in FlexNoC 4 AI based on its learning from some of the world’s leading AI and DNN SoC design teams. Arteris IP customers developing AI chips include autonomous driving pioneer Mobileye, who recently licensed Arteris IP FlexNoC and Ncore interconnect IP for its next-generation EyeQ systems, Movidius, Cambricon, Intellifusion, Enflame, Iluvatar CoreX, Canaan Creative, and four other companies that have not been publicly announced. New capabilities in FlexNoC 4 and the new AI Package include: Automated topology generation for mesh, ring and torus networks – FlexNoC 4 AI enables SoC architects to not only generate AI topologies automatically but also edit generated topologies to optimize each individual network router, if desired. Multicast – FlexNoC 4 AI intelligent multicast optimizes the usage of on-chip and...

Synopsys RTL Architect product represents the industry’s first physically-aware RTL analysis, exploration, and optimization system with signoff technology integration. Synopsys RTL Architect uses a fast, multi-dimensional implementation prediction engine that enables RTL designers to predict the power, performance, area, and congestion impact of their RTL changes. Built on a unified data model, Synopsys RTL Architect directly leverages Synopsys world-class implementation and golden signoff solutions, including Synopsys PrimePower RTL, to deliver results that are accurate early in the design cycle. Synopsys RTL Architect enables designers to significantly reduce RTL development time and to achieve “Simply Better RTL.” Key Benefits Increase Productivity Reduce project schedule with faster runtimes and fewer frontend – backend iterations Predict PPA Fast, implementation prediction engine ensures the...

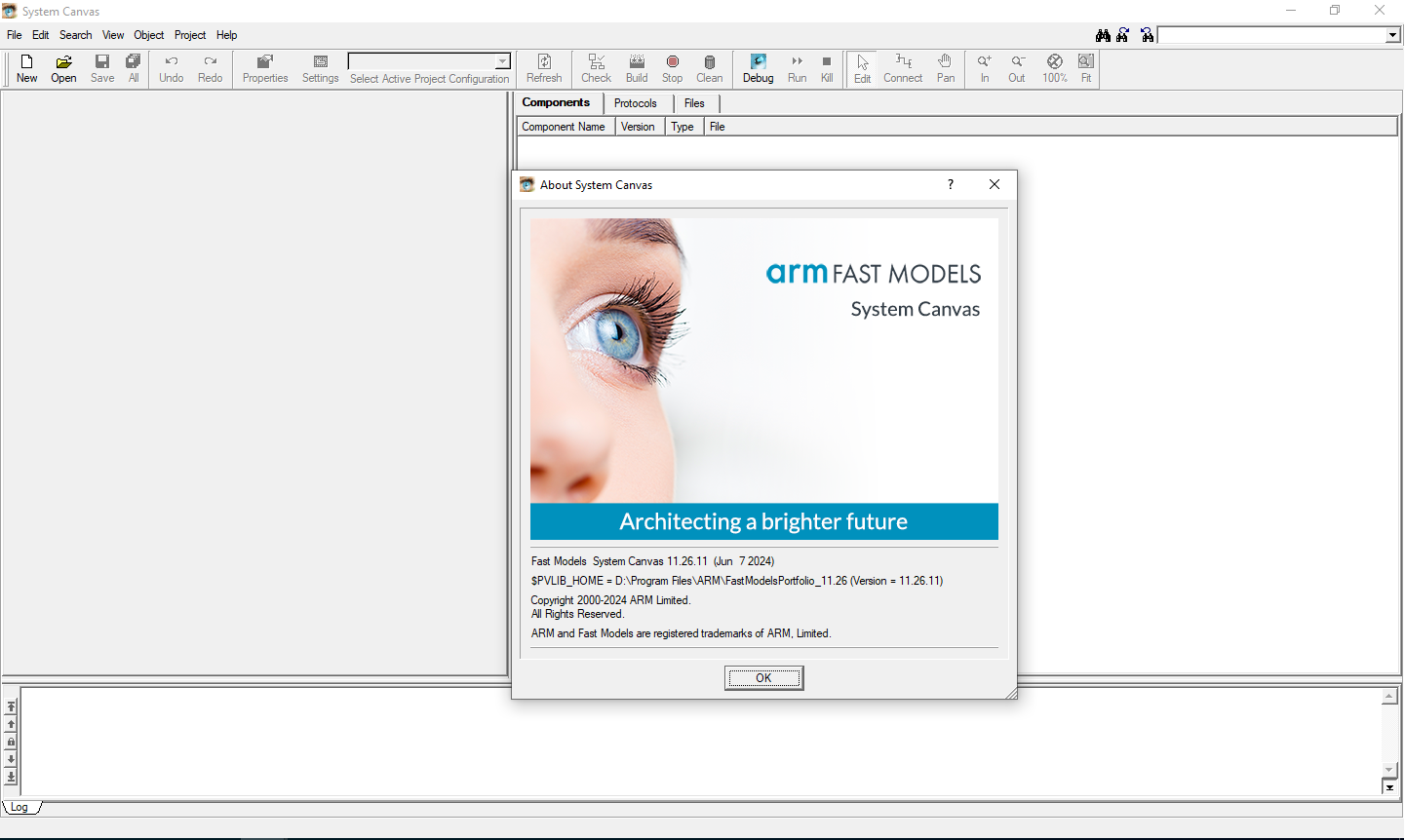

Arm Fast Models are 100% functionally accurate, flexible programmer’s view models of Arm IP. They enable you to develop and test software such as drivers, firmware, OS, and applications without physical hardware. They deliver full control over the simulation, enabling profiling, software and hardware debug, and trace analysis. ARM Fast Models 2024 v11.26 Tested Picture Fast Models are available for all the Cortex-A, Cortex-R, and Cortex-M series CPUs from Arm, alongside many peripherals such as UART modules, memory management units, direct memory controllers, and more. These virtual models are available in two forms: preconfigured fixed systems (with pre-defined cores, memory, and peripherals) called Fixed Virtual Platforms (FVPs); or with a toolset to configure custom Fast Model systems more representative of...

Raphae FX is the gold standard, 2D and 3D resistance, capacitance and inductance extraction tool for optimizing on-chip parasitic for multi-level interconnect structures in small cells. As a reference field solver, Raphael FX provides the most accurate parasitic models in the industry. Trusted by major foundries, interconnect parasitics generated by Raphael FX are included as part of their design reference guides. Synopsys Raphael FX 2024.03 Linux64 Tested Picture Benefits Analyze complex on-chip interconnect structures and the influence of process variation Create a parasitic database for both foundries and designers to study the effect of design rule change Generate accurate capacitance rules for layout parameter extraction tools Interface with Sentaurus Structure Editor to create and analyze arbitrary and complex 3D shapes...

Catapult has the broadest portfolio of hardware design solutions for C++ and SystemC-based High-Level Synthesis (HLS). Catapult’s physically-aware, multi-VT mode, with Low-Power estimation and optimization, plus a range of leading Verification solutions make Catapult HLS more than just “C to RTL”. Catapult High-Level Synthesis Solutions Catapult High-Level Synthesis solutions deliver C++ and SystemC language support, FPGA and ASIC independence, ASIC power estimation and optimization plus the latest in Physically aware multi-VT area and performance optimization to elevate your designs. C++/SystemC Synthesis A comprehensive HLS flow taking C++ or SystemC as the design input and optimally targeting ASIC, eFPGA or FPGA implementations tuned for frequency and target technology. Low-Power Solutions When it comes to early design space exploration, power estimation, and...

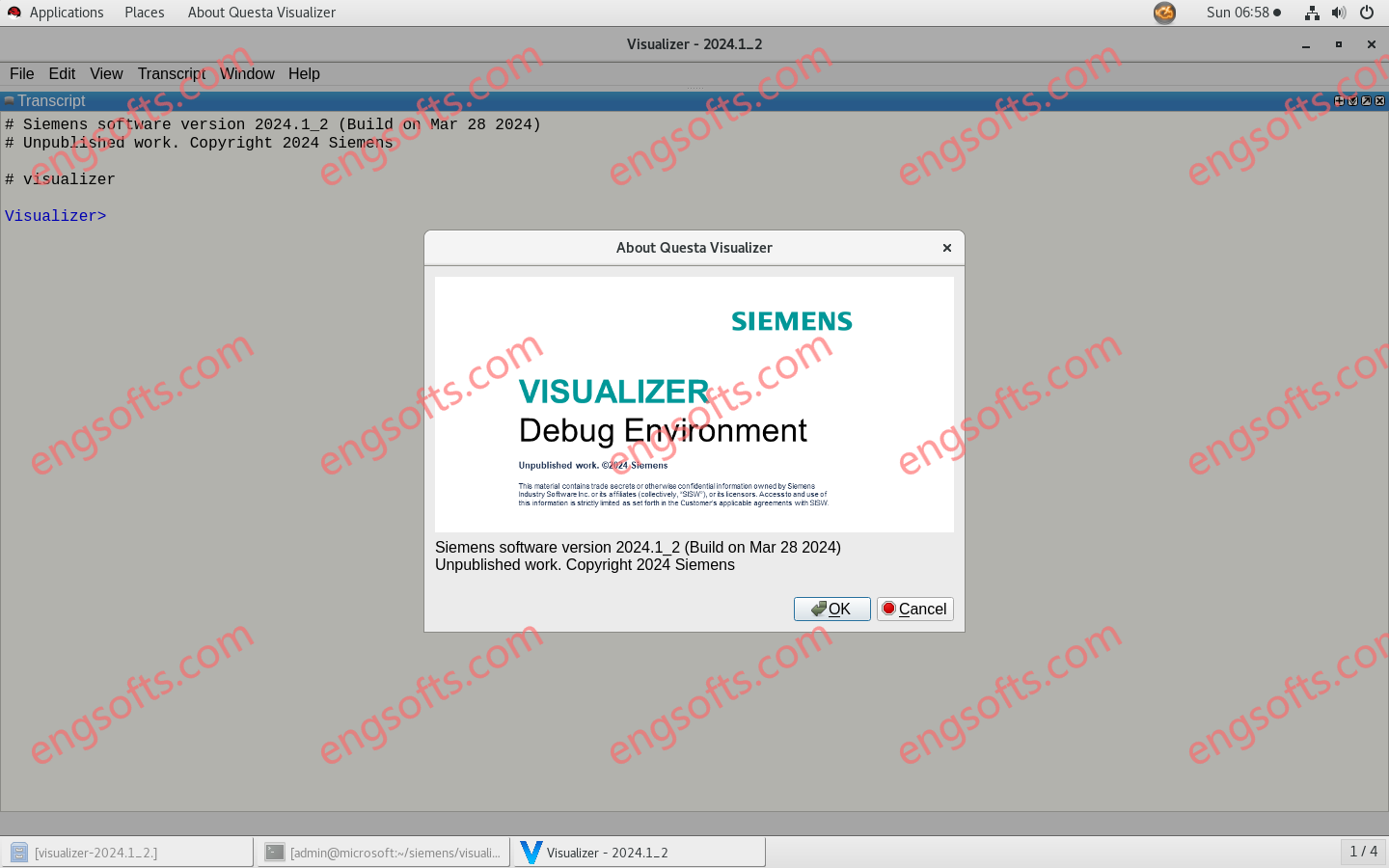

Questa Visualizer Debug Environment is SystemVerilog class-based and UVM-aware to speed up overall debug time, even on today’s most complex SoCs and FPGAs. Siemens Questa Visualizer Debug Environment 2024.1_2 Linux Tested Picture The changing landscape of debug For years the process of ASIC and FPGA design and verification debug consisted primarily of comprehending the structure and source code of the design with waveforms showing activity over time, based on testbench stimulus. Today, functional verification is exponentially complex with the emergence of new layers of design requirements (beyond basic functionality) that did not exist years ago; for example, clocking requirements, security requirements, safety requirements, and requirements associated with hardware-software interactions. Given these complex interactions, effective debug often demands experts that are...

Mician µWave Wizard 2023 Version 10.0 is a full wave 3D EM-design automation suite is aimed at improving your RF component design and simulation workflows. Take a look at its key features: Revamped Customizable User Interface: Discover the efficiency of µWave Wizard™’s redesigned UI, featuring dockable windows for a individual workspace layout. Arrange schematic editors, plot windows, and more to best suit your workflow. New Schematic Editor: Experience a smoother and more efficient design workflow with µWave Wizard™’s enhanced routing capabilities. This latest update features 3D representations of library elements for a realistic look and accurate depiction of modeler elements, ensuring precise modeling in your designs. Improved Project Loading: Version 10.0 loads projects faster than ever allowing projects to be edited right after launch without having to wait for all circuits...

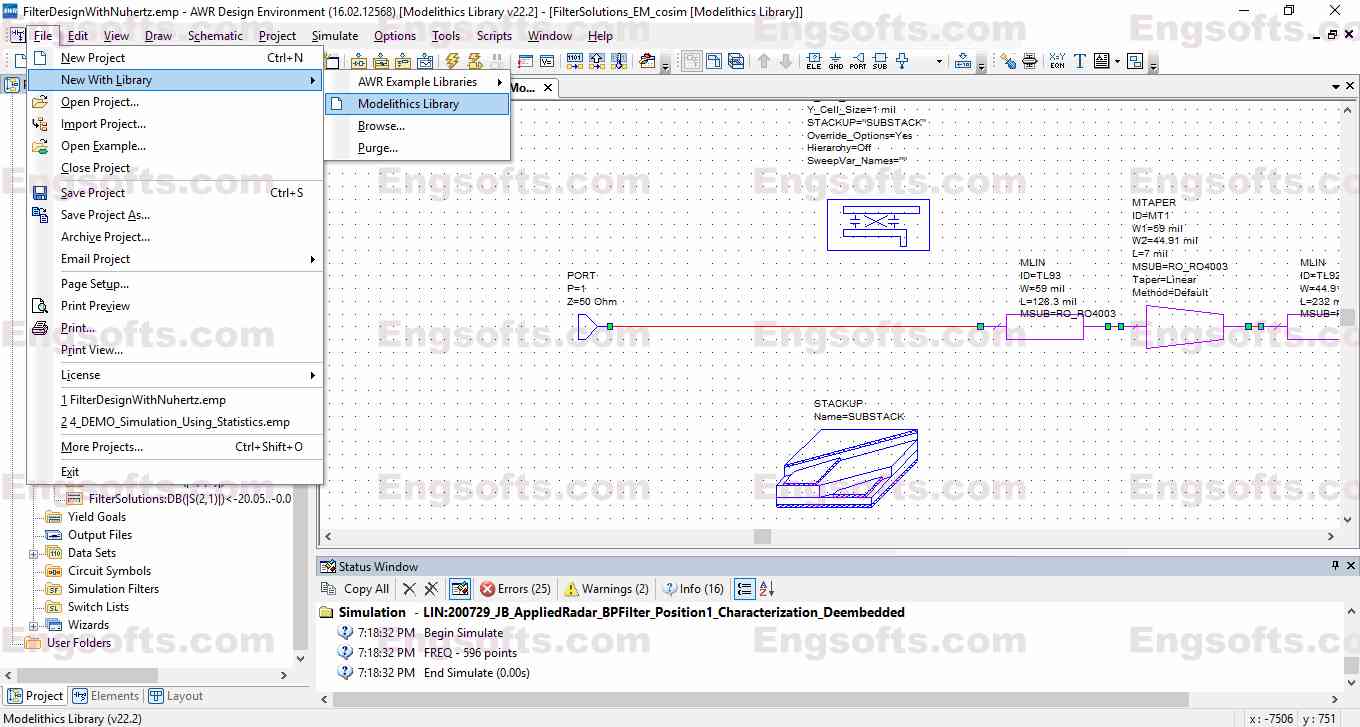

Modelithics announced the release of the latest version, v22.2, of the Modelithics COMPLETE Library for use with the Cadence AWR Design Environment Platform. This version adds nearly 50 new models for various components to the Modelithics COMPLETE Library. With these additions, the Modelithics COMPLETE Library now includes over 825 models that represent over 25,000 passive and active RF/microwave components. This collection of simulation models comprises surface-mount RLC components, diodes, transistors, amplifiers, attenuators, filters, couplers and other system components. Version 22.2 adds new scalable Microwave Global Models™ to the Modelithics COMPLETE Library, including five models for Amotech capacitors, three models for Coilcraft inductors, three models for Kemet capacitors, three models for Kyocera-AVX capacitors, three models for Smiths Interconnect resistors and one for...

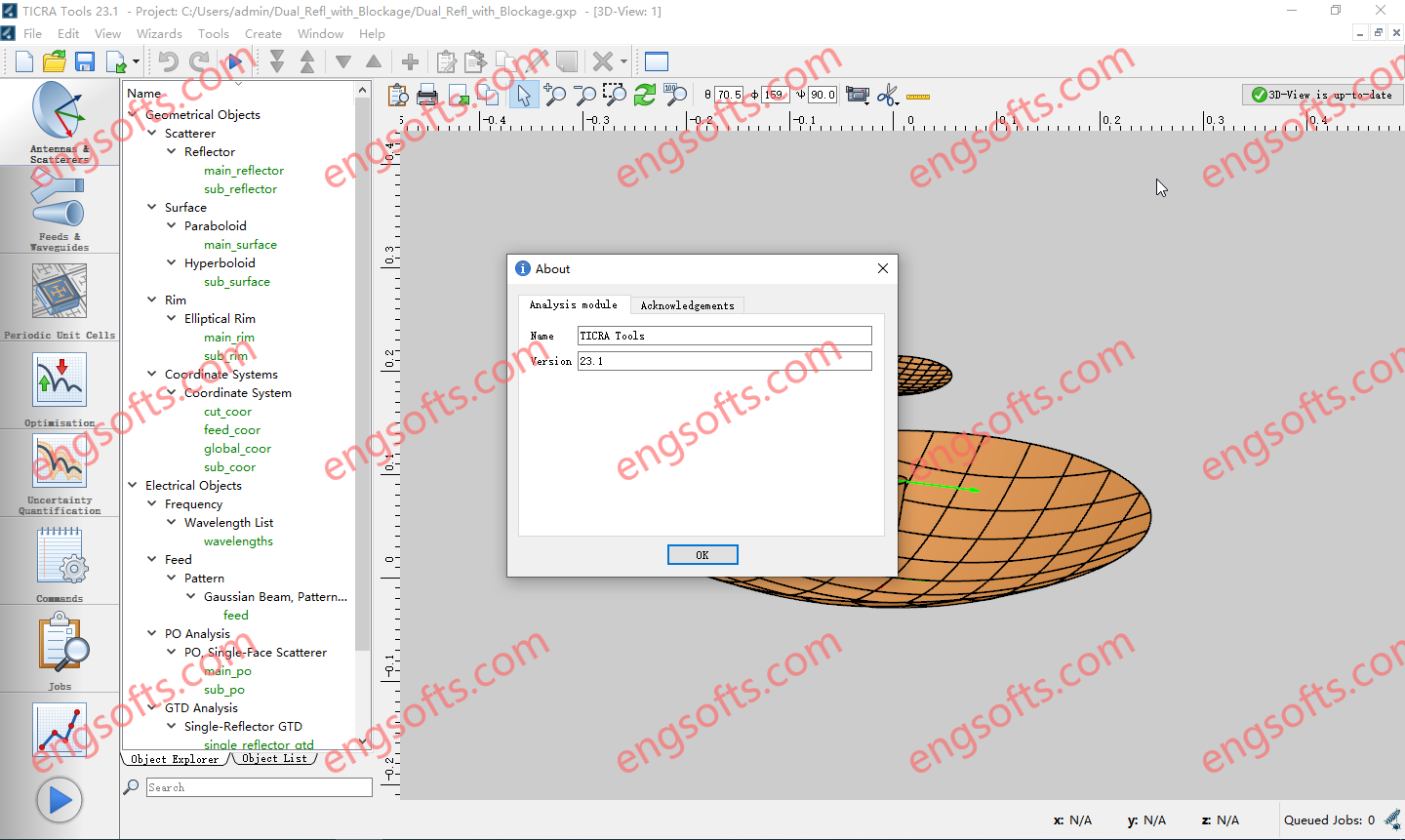

The TICRA Tools framework offers a range of products with a proven track record you can trust to accomplish your daily analysis and design optimisation tasks. The applications range from reflector antennas in GRASP over general antenna and scattering analysis in ESTEAM to feed horns and waveguide components in CHAMP 3D, as well as surfaces composed of frequency and polarization-sensitive materials in QUPES. POS is the tool for advanced payload antennas, while UQ augments the usual antenna design process with uncertainties on design parameters to get expected antenna performance and confidence intervals. TICRA Tools 23.1 Tested Picture TICRA Tools 23.1, introducing valuable enhancements that empower users with improved and more efficient workflows. Among many improvements, selected highlights of this release...

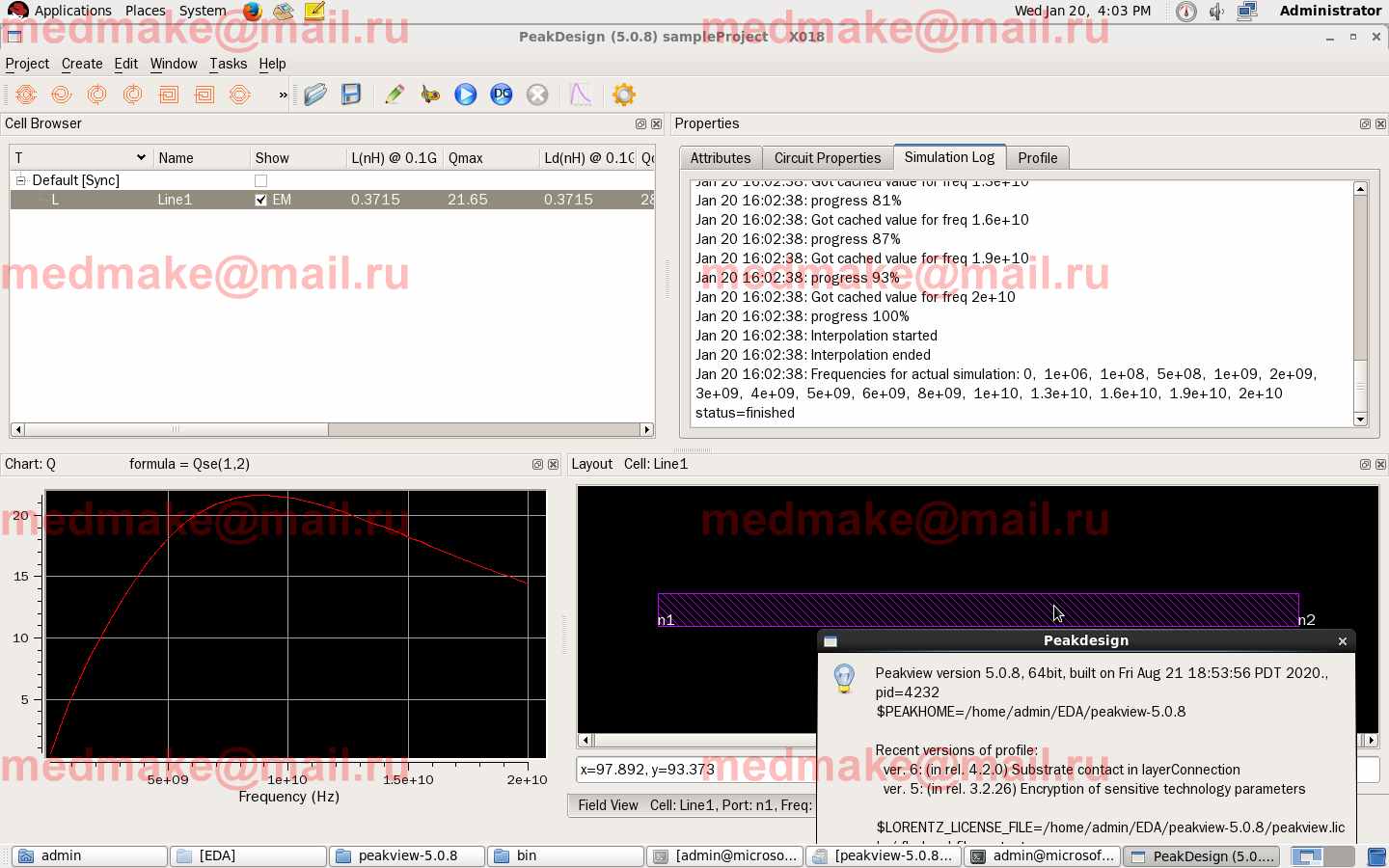

Lorentz Solution’s PeakView™ is an innovative electromagnetic design platform for high speed analog and RFIC design and analysis. PeakView™ products are assimilated into the Virtuoso® environment, Custom Compiler layout editor, and customary RC extraction flows, providing designers with a familiar IC design experience from prototyping to sign-off. Lorentz PeakView 5.08 Linux64 Tested Picture Benefits of PeakView™ Platform vs. Discrete Tools The PeakView™ EM platform is fully integrated into the Cadence® and Custom Compiler IC design environments. Designers can select components from the PeakView™ built-in PCircuit library, optimize device parameters and synthesize target values. PeakView’s iRCX and ITF parsers support process technology information provided by various foundries. PeakView EM Prototyping and HFD™ performs electromagnetic modeling of EM coupling and parasitic inductive...