EDA 第6页

Electrical & Power Engineering softwares.

Ansys RedHawk-SC Electrothermal features multiphysics power integrity, signal integrity, thermal integrity, and mechanical stress simulation and analysis for 2.5D/3D multi-die systems. The Ansys RedHawk-SC Electrothermal is a Multiphysics simulation platform. It delivers a complete solution for analyzing multi-die chip packages and interconnects for power integrity, layout parasitic extraction, thermal profiling, thermo-mechanical stress, and signal integrity. Integrated within the cloud-native SeaScape platform enables high-capacity electrothermal analysis for early-design exploration, post-layout design verification, and silicon signoff of stacked-die system. It is foundry certified for integrated fanout and silicon interposer technologies.

The Maxwell CSIRO interface is not part of the standard Maxwell functionality. Users are required to purchase a licence that enables them to interface the modules with Maxwell. All users who purchase the CSIRO interface are given access via their existing website login for convenience. Furthermore, EMIT actively maintains the suite of CSIRO applications, correcting errors and adding additional functionality in response to user feedback and requests. Maxwell allows the user to define, display and edit model parameters through drag and drop mouse operation. Layered earth, thin-sheet, prism and mesh models can be built in Maxwell’s 3-D visualisation environment. Requires Maxwell version 5 or later Ground system configurations tested include drill-hole, fixed, coincident and in-loop systems and MT Airborne modules...

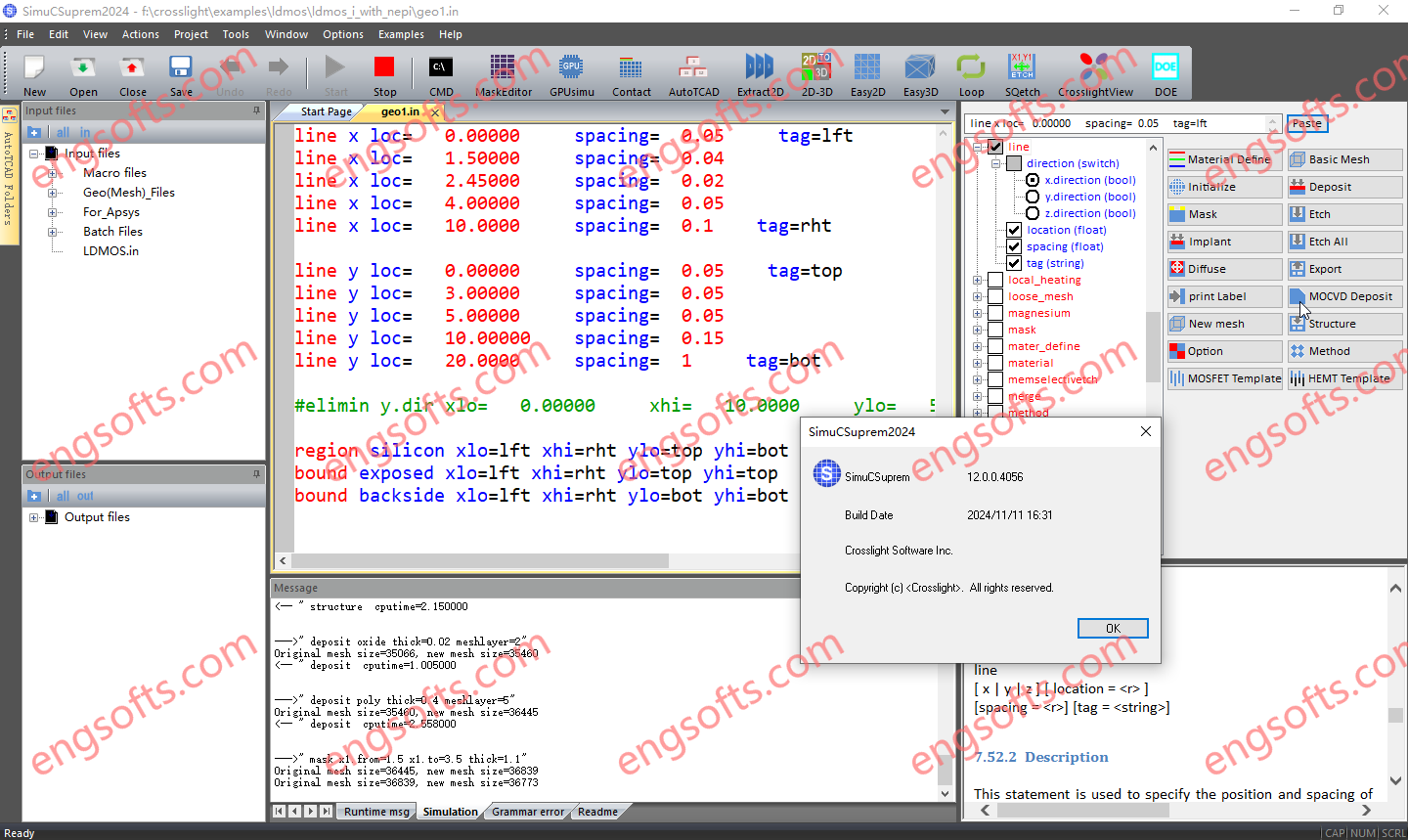

CSUPREM (Crosslight-SUPREM) is a process simulation software package based on the SUPREM.IV.GS code developed at the Integrated Circuits Laboratory of Stanford University. SUPREM.IV.GS (2D) has long been recognized as the industry standard in process simulation for integrated circuit (IC) design for over a decade. Crosslight greatly enhances the capability of the original code from Stanford and extends it from 2D to 3D. Please refer to our full and mini CSUPREM product brochures for more details… Available versions: 2024.x , 2022.x ,… Crosslight CSuprem 2024 Tested Picture A brief introduction to Crosslight TCAD is also available in the following presentation and pamphlet. Features Reliable and flexible next-generation 2D/3D process simulator 2D, Quasi-3D, Hybrid-3D and Full 3D process simulation 2D and Full 3D device simulation when combined with APSYS GPU-accelerated solver Full...

Siemens.com IC-Custom 2024.3 is an enterprise-ready, custom IC design flow for innovative designs supporting both FinFET and planar analog, analog mixed-signal. With over 30 years of experience and thousands of design tape outs, this platform is well suited for “More than Moore” designs. Custom IC Design 2024 Release Highlights

Xtensa Xplorer serves as a cockpit for basic design management, invocation of Tensilica processor configuration tools (Xtensa processor generator, TIE Compiler) and software development tools. Xtensa Xplorer is particularly useful for the development of TIE (Tensilica Instruction Extension) instructions – designer-defined instruction extensions to the Xtensa processor – that maximize performance for a particular application. Different Xtensa processor and TIE configurations can be saved, profiled against the target C/C++ software, and compared. Xtensa Xplorer even includes automated graphing tools that create spreadsheet-style comparison charts of performance. Available versions: 10.1.11 , 9.0.18 , 8.0.8 , 7.0.9 ,… Xtensa Xplorer dramatically accelerates the processor optimization cycle by providing an automated, visual means of profiling and comparing different processor configurations. Since it only...

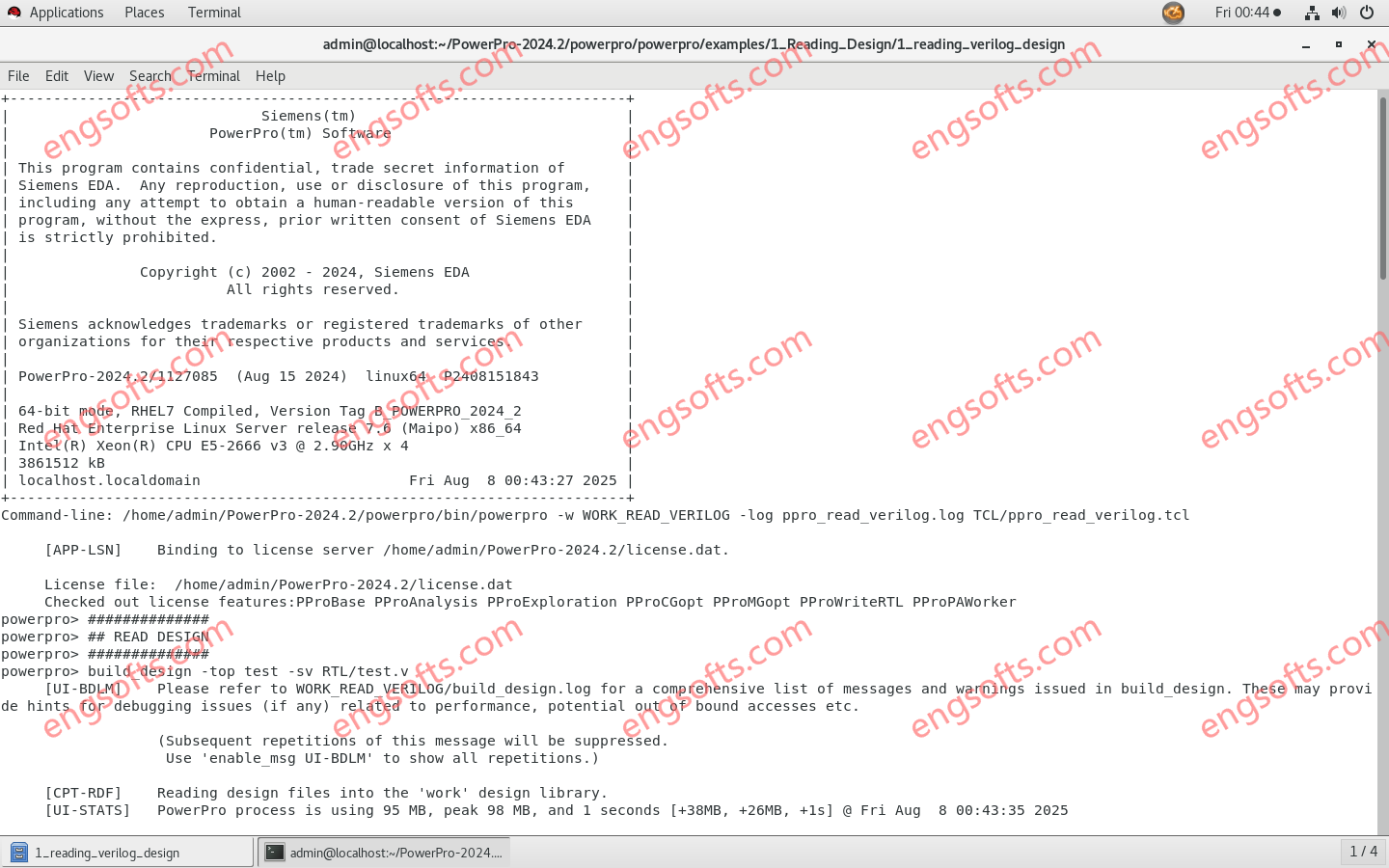

PowerPro offers the most comprehensive set of features to RTL designers to “design-for-low-power”. It offers power estimation for both RTL and Gate-level designs, early power checks to quickly find power issues during RTL development and clock and memory gating to optimize the design for power. Available versions: 2024.2 , 2022.1 , … Siemens PowerPro 2024.2 Linux Tested Picture PowerPro Power Analysis & Optimization Platform PowerPro offers the most comprehensive set of features to RTL designers to “design-for-low-power”. It offers power analysis for both RTL and gate-level designs, early power checks to quickly find power issues during RTL development and clock and memory gating to optimize the design for power. RTL Power Estimation PowerPro RTL Power Estimation delivers highly accurate estimations...

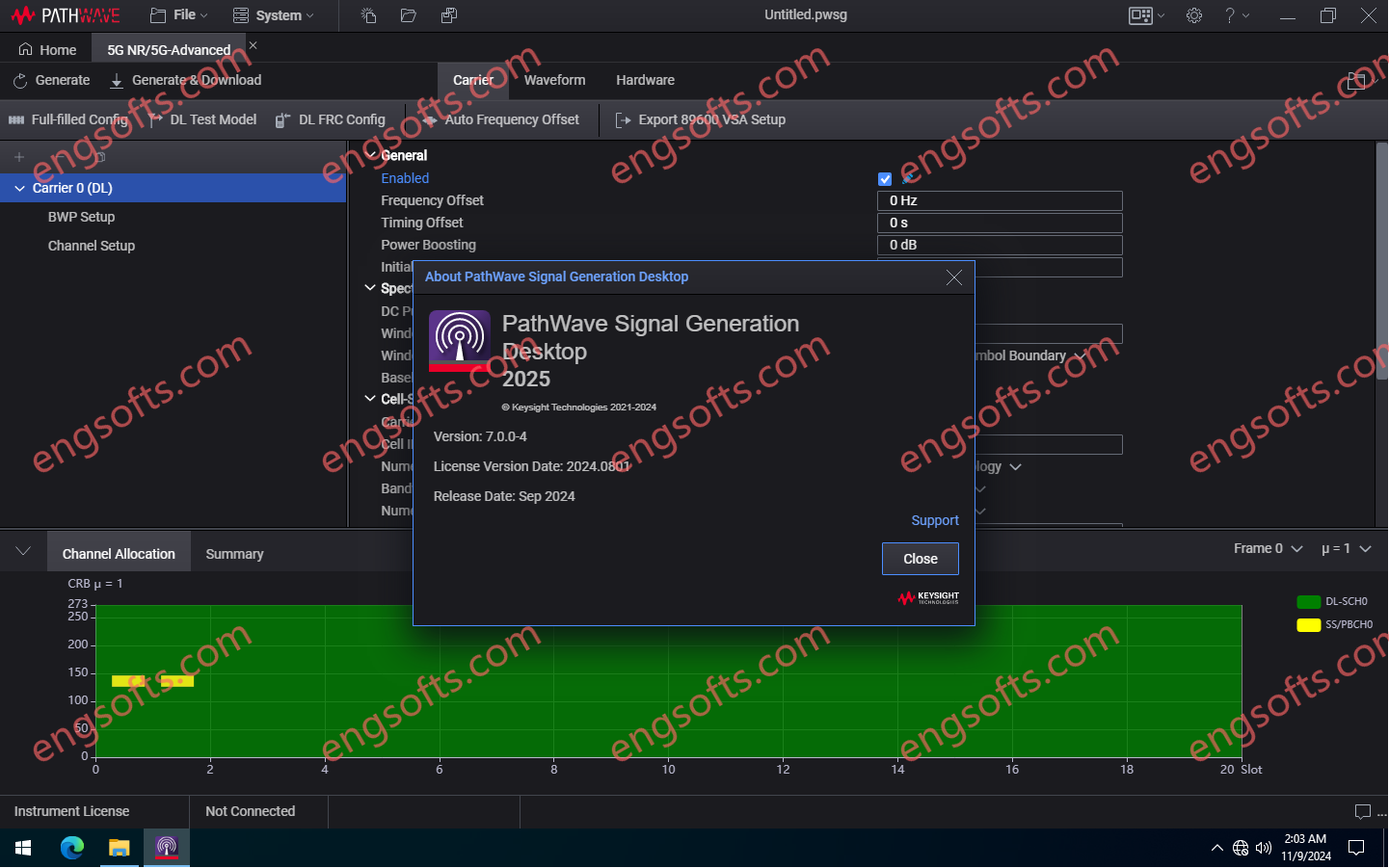

PathWave Signal Generation is a signal creation for a wide range of general purpose or standards-based signals. Comprehensive PC-based software for flexible signal creation. Cellular, wireless connectivity, aerospace/defense, broadcasting and general purpose applications. Supports a wide variety of signal generation hardware. PathWave Signal Generation Desktop 2025 v7.0.0 Tested Picture Create Performance-Optimized Reference Signals Create calibrated signals, validated by Keysight, that conform to industry standards to help enhance the characterization and verification of your devices with or without impairments. Validate Component, Transmitter and Receiver Testing Easily create and playback customized waveforms for component testing with virtually distortion-free test signals. Generate fully channel-coded signals including real-time mode to evaluate the throughput of your receiver. Impairments can be also added to evaluate receiver...

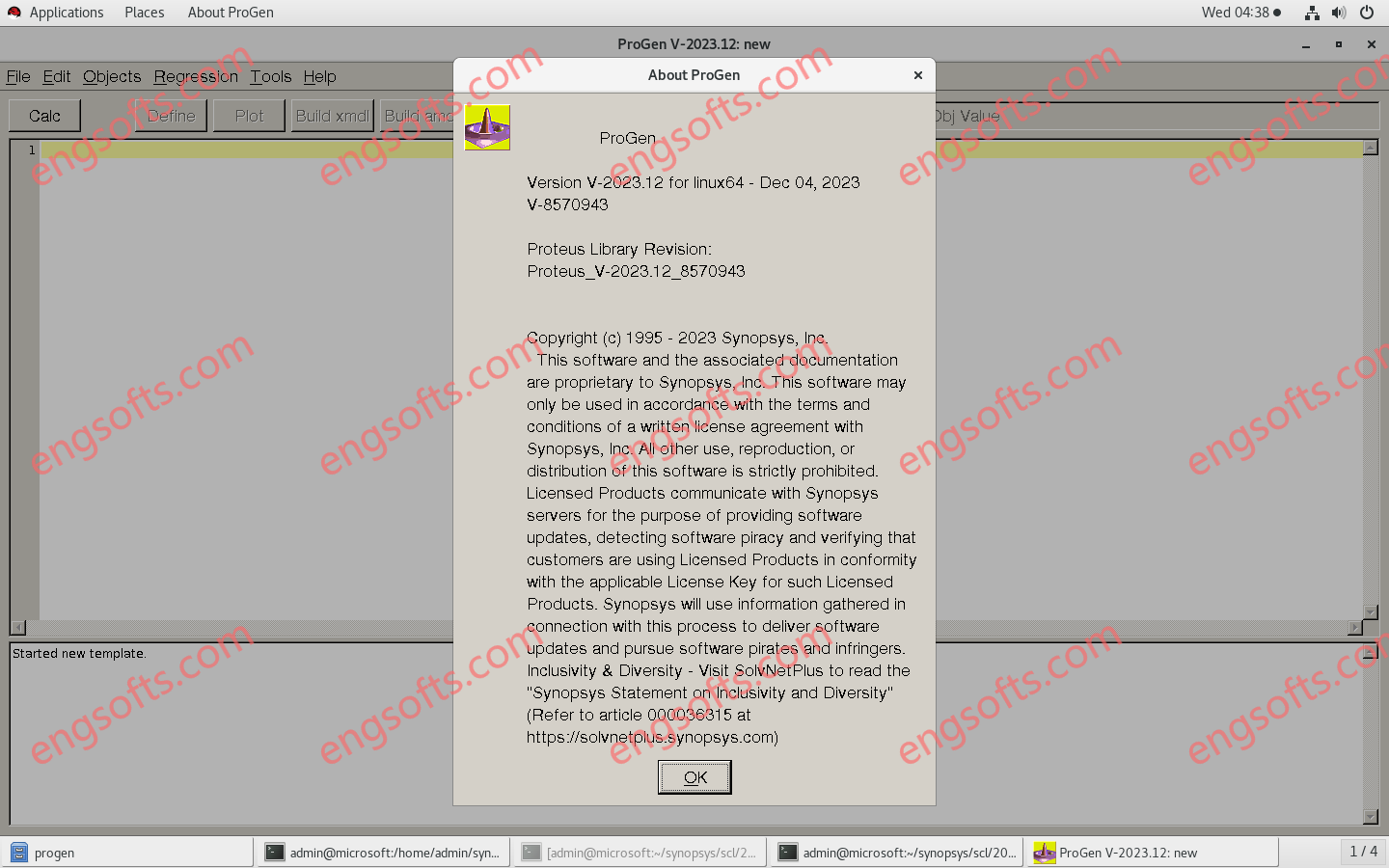

Proteus ProGen models are empirical compact models reflecting the performance of a lithography process. Model parameters are determined by fitting experimental data. The Proteus Modeling Platform (PMP) provides a single environment for calibrating those parameters with a high degree of automation and tuning them for optimum performance in downstream applications. Synopsys ProGen 2023.12 Linux64 Tested Picture ProGen, Proteus’ highly customizable solution calibrates a single model that is utilized by both the space- and frequency-domain engines.

Synopsys Proteus™ full-chip mask synthesis smart manufacturing solutions enabling technologies down to 3nm and below. With the Synopsys Proteus family you can achieve exceptional precision, efficiency and speed in proximity correction, model building for correction, and analyzing proximity effects on corrected and uncorrected IC layout patterns, revolutionizing your chip fabrication process. The Synopsys Proteus full-chip mask synthesis family are the products of choice for leading edge IDMs and foundries and have been production proven for two decades with support for the latest EUV lithography processes. Synopsys Proteus 2023.12 Linux64 Tested Picture Key Benefits Largest Lithography Entitlement Industries first and most deployed inverse lithography solution with native curvilinear design and mask support. Fast Turn Around Time AI driven solutions with advanced...

Proteus WorkBench (PWB) is a powerful cockpit tool for the development and optimization of Proteus-based mask synthesis solutions. It is based on a powerful hierarchical GDSII/OASIS layout visualization and editing engine, providing a comprehensive environment for lithography simulation, compact model building, optical proximity correction (OPC) recipe tuning, litho rule checks, and mask synthesis flow development. Synopsys Proteus WorkBench 2023.12 Linux64 Tested Picture PWB offers an easy to use platform with access to a wide-ranging set of tools, enabling fast calibration of accurate models, supporting the optimization of highly efficient Proteus recipes for deployment in OPC and verification. As state-of-the-art lithography exposure tools are operated at their physical resolution limit, new mask and process technologies are being deployed to further shrink...