EDA 第5页

Electrical & Power Engineering softwares.

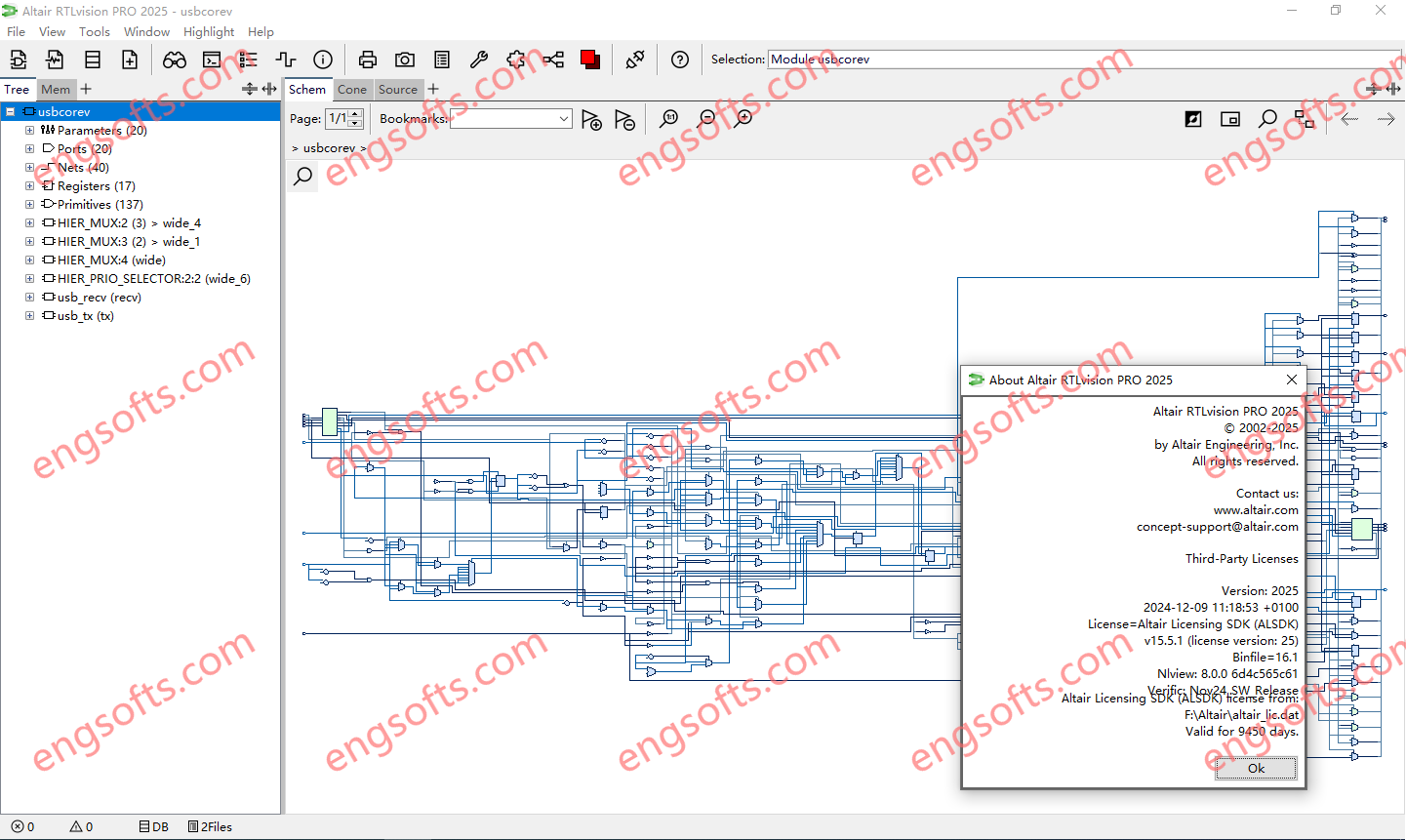

RTLvision® PRO simplifies the visualization of large RTL designs, including third party IP and reused blocks. Using Concept’s award winning visualization technology, the tool provides the unique and effective graphical rendering of RTL code structures, allowing engineers to quickly appreciate design functionality. Supporting SystemVerilog, VHDL and Verilog, RTLvision PRO comes complete with a range of debug views such as a powerful waveform display, an interactive cone of influence window, and other displays for a complete, 360° picture of the device. Available other versions: 2024.x , 2023.x , 7.1.x , 6.x , 5.x Altair RTLvision PRO 2025.0 Win Tested Picture Altair RTLvision PRO 2025.0 is a major release, the following features were fixed and/or added: Show the logic value at the...

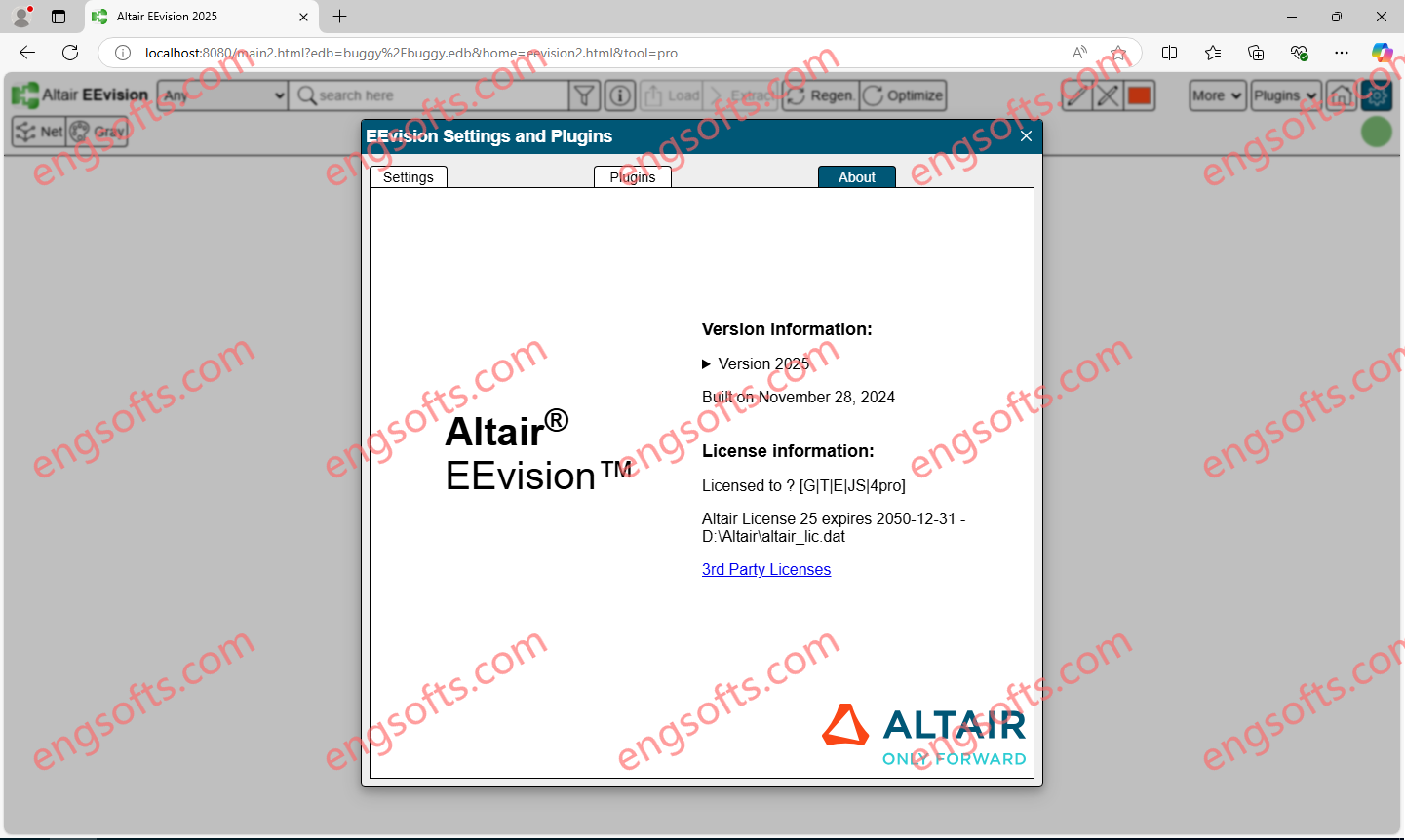

EEvision is an online visualization and debugging solution that easily renders schematics of circuits, wiring harnesses and component attributes specific to individual development and maintenance situations. Taking original CAD data or proprietary data as input, schematics are automatically rendered and explored on-the-fly, allowing complex systems to be easily and quickly understood. Google-style live search features allow for precise information to be extracted from huge data files and displayed in an easy-to-understand fashion. Available other versions: 2024.x , 2023.x , 7.1.x , 6.x , 5.x Altair EEvision 2025.0 Tested Picture Unlike development CAD systems and paper maintenance manuals, incremental schematics reduce the clutter of unnecessary detail, while highlighting key data to significantly accelerate development and debug. The views can be modified...

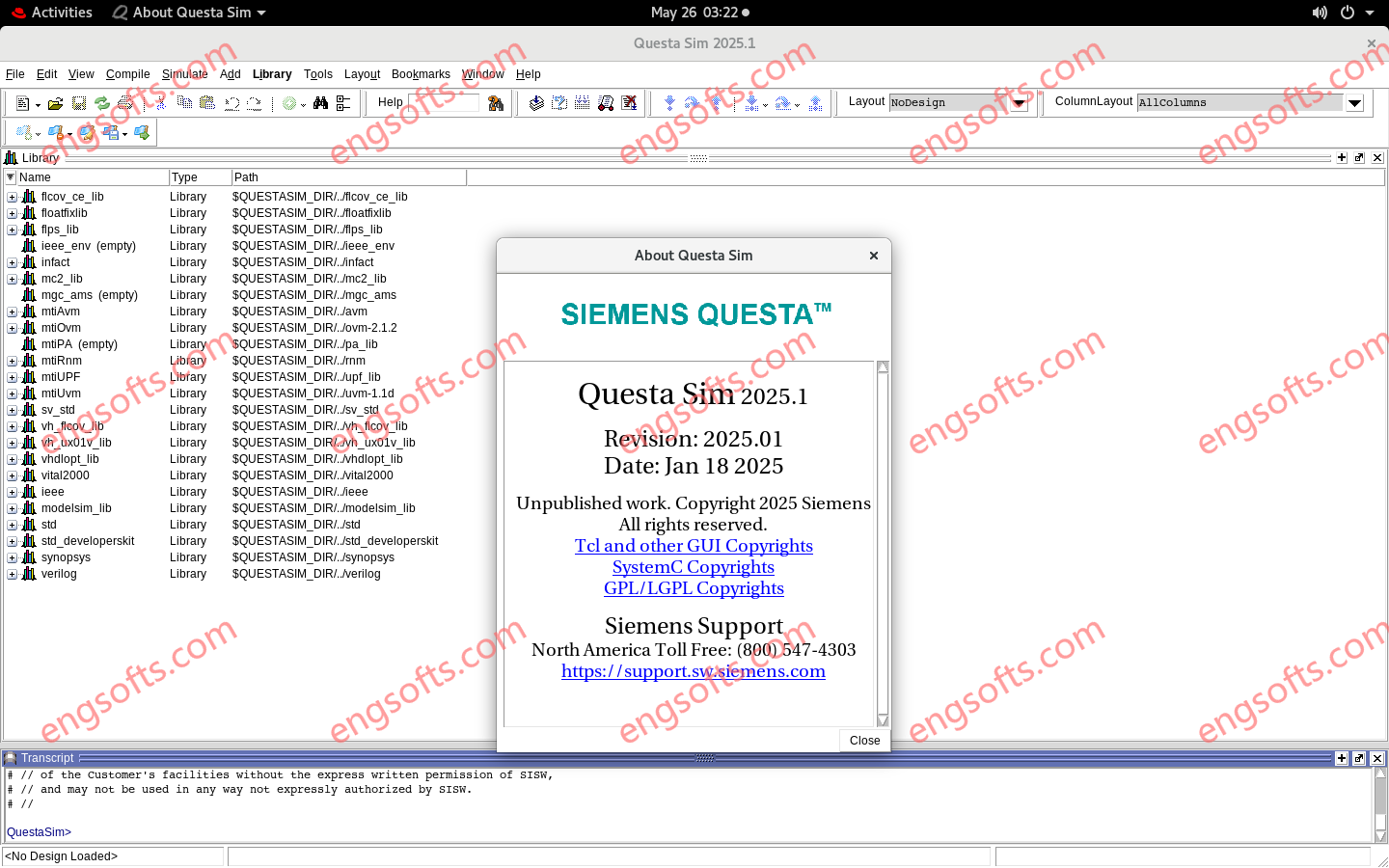

The Questa advanced simulator is the core simulation and debug engine of the Questa verification solution; the comprehensive advanced verification platform capable of reducing the risk of validating complex FPGA and SoC designs. Available other versions: 2024.1 ,10.7 Siemens Questa Advanced Simulator 2025.1 Linux Tested Picture The QuestaSim verification solution delivers on these requirements for complex SoC designs. QuestaSim achieves industry-leading performance and capacity through aggressive, global compile and simulation optimization algorithms for SystemVerilog, VHDL, and SystemC. Meanwhile, its Questa Visualizer debug environment provides high-performance, high-capacity debugging for dramatic regression throughput improvements when running large test suites. QuestaSim Benefits Industry-leading high performance multi-language simulator High-performance, high-capacity unified debug Reference simulator for LRM compatibility UVM, SystemVerilog, VHDL, SystemC, and mixed language...

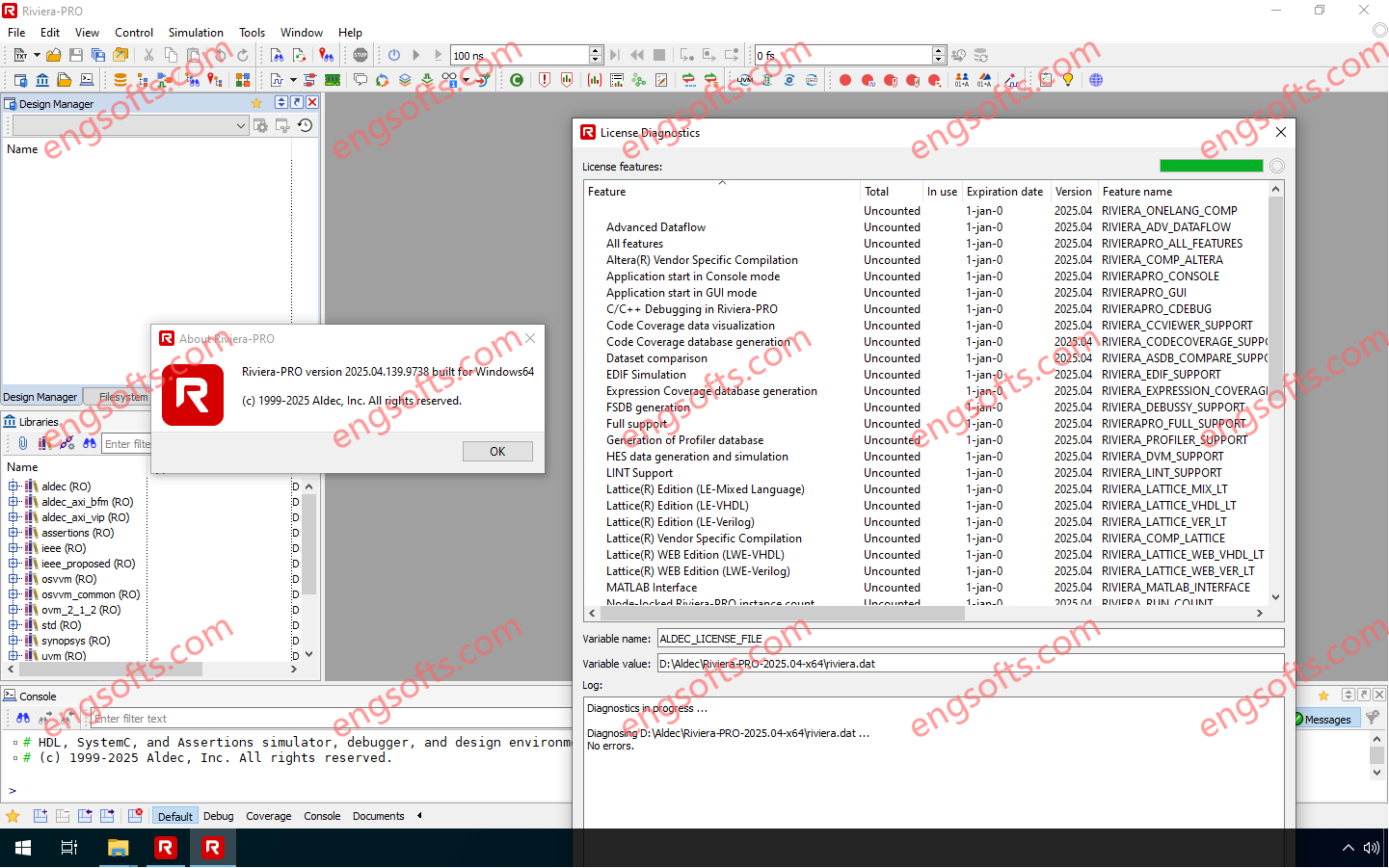

Riviera-PRO addresses verification needs of engineers crafting tomorrow’s cutting-edge FPGA and SoC devices. Riviera-PRO enables the ultimate testbench productivity, reusability, and automation by combining the high-performance simulation engine, advanced debugging capabilities at different levels of abstraction, and support for the latest Language and Verification Library Standards. Available versions: 2025.04 , 2024.04 , … Aldec Riviera-PRO 2025.04 Win/Linux64 Tested Picture Riviera-PRO 2024.04 New Release Key Highlights The SystemVerilog type operator can be used on the list of the actual parameters of classes and design units parameterized with type. The type operator can be used in the type specification of typedef. The modules parameterized with type can be bound to instances with the use of the bind statement. Assigning the value null to SystemVerilog covergroup defined in a class outside of the class constructor is...

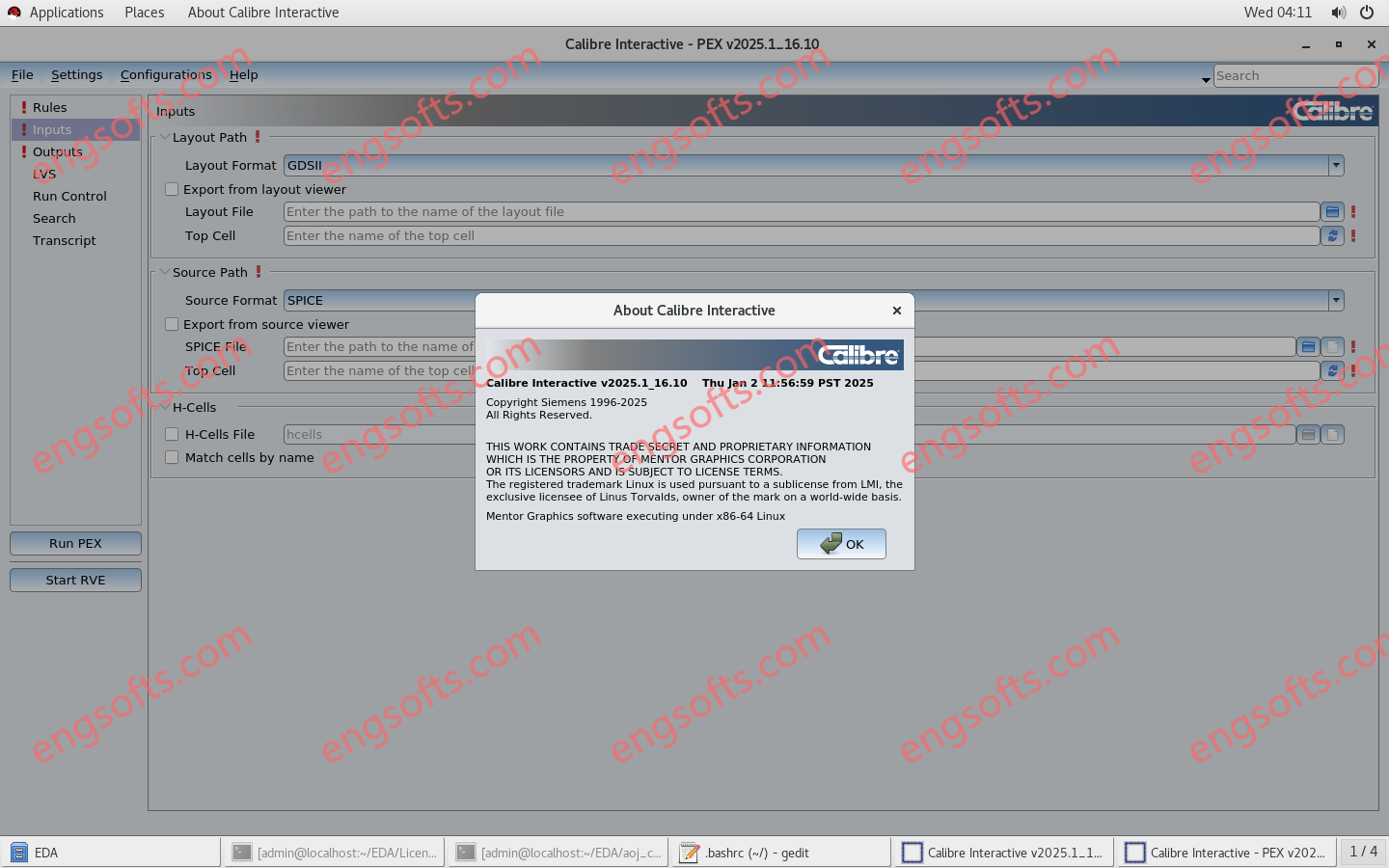

Calibre Design Solutions is the industry leader for IC verification, delivering a complete IC verification and DFM optimization EDA platform that speeds designs from creation to manufacturing, addressing all sign-off requirements. Siemens Calibre 2024.2 Linux Tested Picture Calibre Design Solutions Portfolio Calibre Design Solutions delivers the most accurate, most trusted, and best-performing IC sign-off verification and DFM optimization in the EDA industry. Calibre Physical Verification The Calibre nmDRC Platform provides foundries, IDMs, and fabless companies with comprehensive, innovative verification technology for all nodes and processes. Calibre Circuit Verification The industry-leading Calibre circuit verification toolsuite includes layout vs. schematic (LVS) checking, reliability verification, and parasitic extraction. Calibre Reliability Verification Calibre reliability verification performs checks against electrical and physical design rules and...

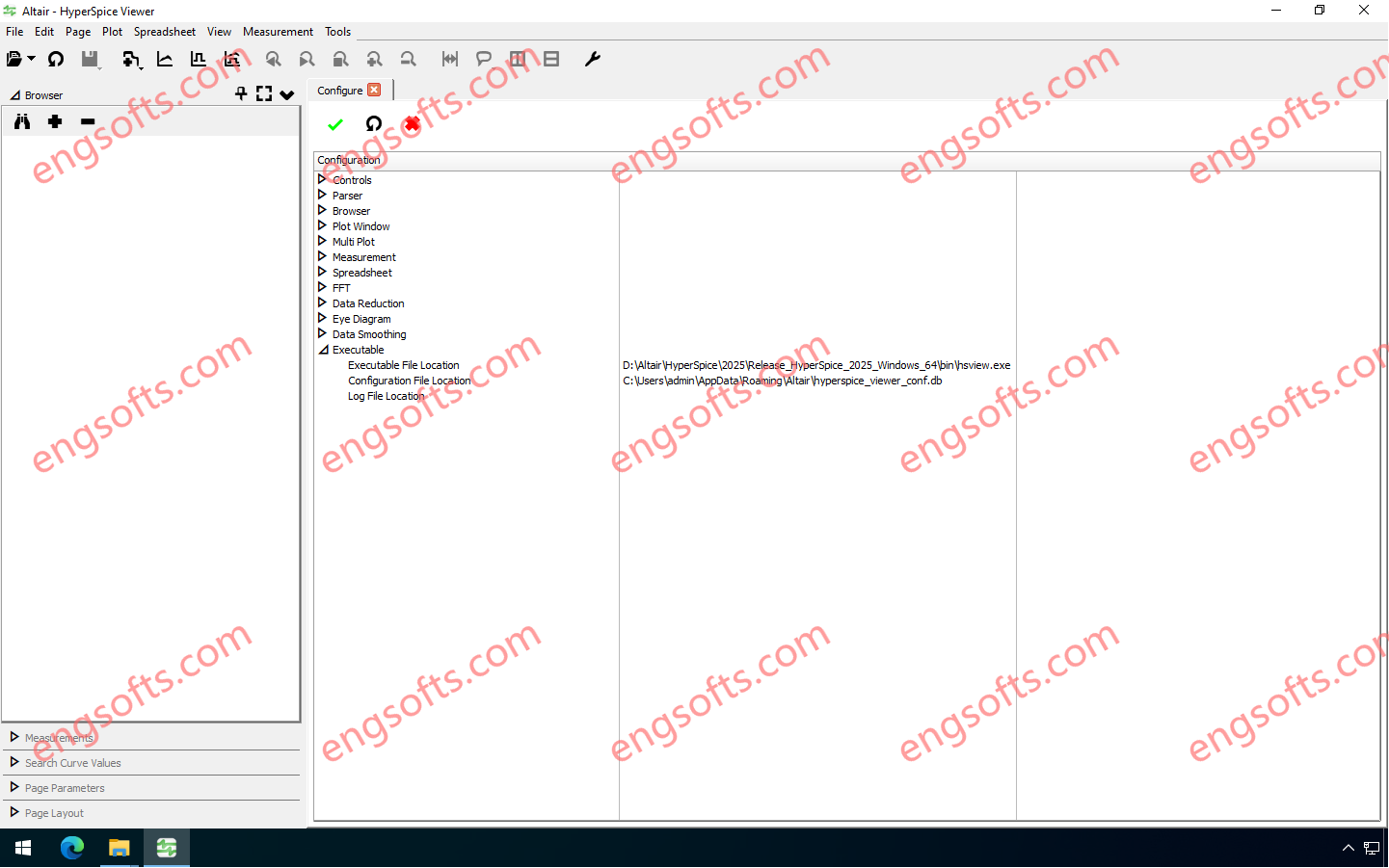

Altair HyperSpice 2025.0 is a command line solver and waveform viewer for simulating electrical circuits modelized in SPICE. With access to Spice libraries for rapid AC, DC, and Transient simulations, it runs as standalone software or is fully integrated into a flexible system-wide simulation solution, helping companies innovate faster. Available versions: 2025.x , 2024.x , 2023.x , 2022.x ,… Altair HyperSpice 2025.0 Tested Picture

Many thousands of layout parasitics dominate integrated circuit (IC) performance. ParagonX provides early, fast, and easy parasitic analysis with visual debugging and root-cause detection. ParagonX lets IC design engineers shift left to quickly explore and find the root causes of parasitic-induced design issues. It enhances existing EDA workflows with powerful analytics and visual feedback for identifying the root causes of layout parasitics’ impact on performance, precision, robustness, and reliability earlier in the design cycle.

A pre-LVS electromagnetic modeling solution that combines the gold standard Ansys HFSS electromagnetic simulation engine with the silicon-optimized Ansys RaptorX engine. Ansys RaptorH is an electromagnetic modeling software with capacity to model power grids, full custom blocks, spiral inductors, and clock trees. Its high-speed distributed processing delivers accurate, silicon-proven S-parameter and RLCk models. RaptorH can analyze partial and unfinished layouts during the design phase and makes it easy to use either the general purpose HFSS engine or the silicon-optimized RaptorX engine for silicon structures.

PowerArtist is the industry-leading RTL power analysis and reduction software with the most comprehensive features to enable power-efficient design early in the design flow. Ansys PowerArtist is the comprehensive RTL design-for-power platform of choice of leading low-power semiconductor companies for early power analysis and reduction. PowerArtist includes physically-aware RTL power accuracy, interactive power debug, analysis-driven power reduction, unique metrics for tracking power efficiency and vector coverage, rapid power profiling of real workloads, and seamless enablement of RTL-to-physical power grid integrity.

Ansys RedHawk-SC Electrothermal features multiphysics power integrity, signal integrity, thermal integrity, and mechanical stress simulation and analysis for 2.5D/3D multi-die systems. The Ansys RedHawk-SC Electrothermal is a Multiphysics simulation platform. It delivers a complete solution for analyzing multi-die chip packages and interconnects for power integrity, layout parasitic extraction, thermal profiling, thermo-mechanical stress, and signal integrity. Integrated within the cloud-native SeaScape platform enables high-capacity electrothermal analysis for early-design exploration, post-layout design verification, and silicon signoff of stacked-die system. It is foundry certified for integrated fanout and silicon interposer technologies.