EDA 第4页

Electrical & Power Engineering softwares.

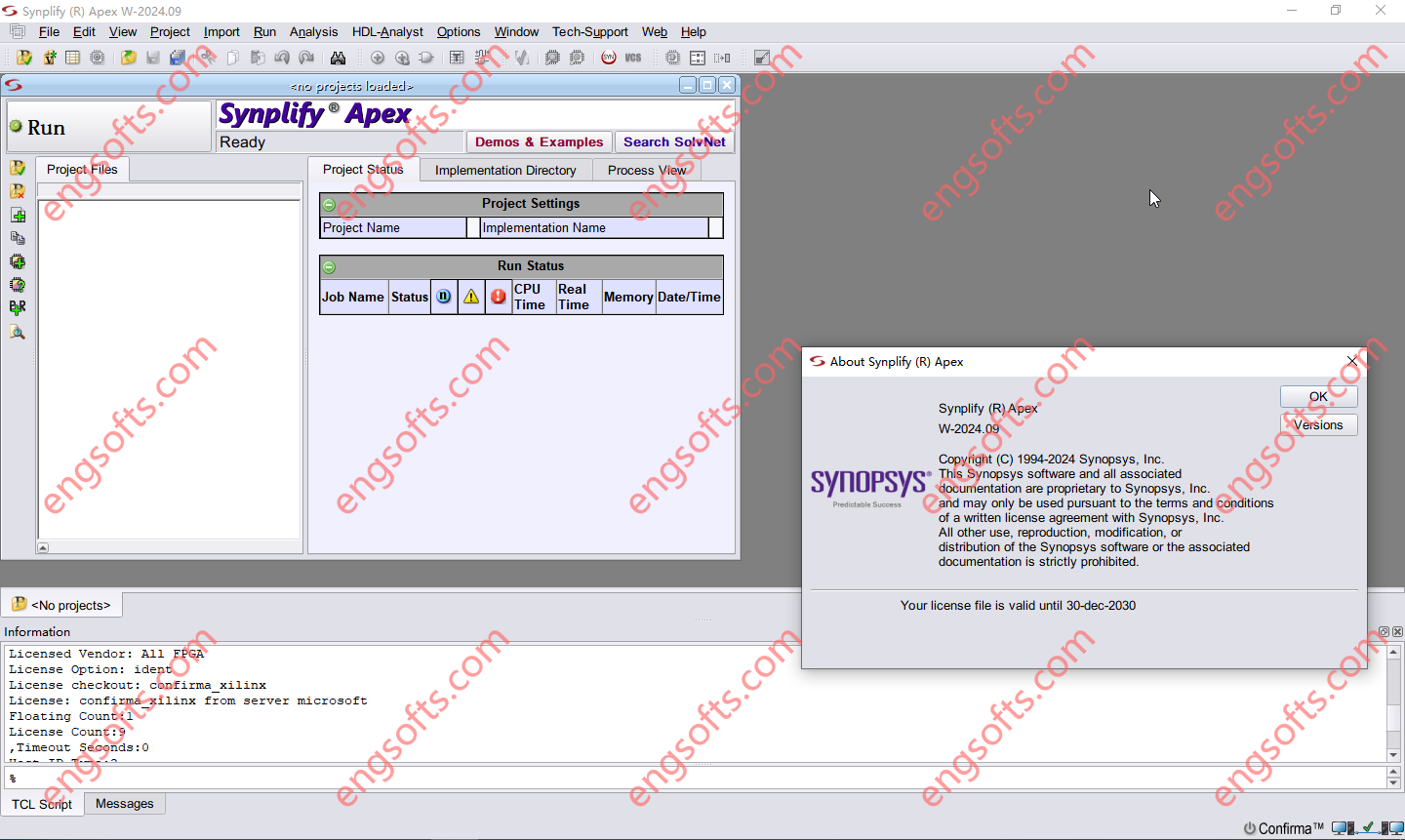

Synplify FPGA综合软件是业界公认的高性能、高性价比FPGA设计标准。Synplify软件支持最新的VHDL和Verilog语言结构,包括SystemVerilog和VHDL-2008/2019。此外,该软件还支持来自众多FPGA厂商的FPGA架构,例如Achronix、Intel、Lattice、Microsemi和AMD/Xilinx,所有架构均可通过单一的RTL和约束源进行综合。 可用版本: 2025.x ,2024.x ,2023.x ,… Synopsys Synplify FPGA 2024.09 Win/Linux64 Tested Picture 此外,Synplify 综合工具提供高性能、更快的运行速度、面积优化以降低成本和功耗,以及增量式和团队设计功能,从而加快 FPGA 设计开发速度。 它包含 TMR 和 HAMMING-3 for FSM 等功能,可自动创建高可靠性设计,例如用于医疗、汽车、工业自动化、通信、军事和航空航天等领域的设计。 Synplify 功能 高级 Verilog、SystemVerilog 和 VHDL 支持 最佳结果质量 (QoR),实现时序性能和面积/成本降低 支持高可靠性和安全关键型设计,包括 DO-254、ISO 26262 和 IEC 61508 标准 加速运行时间,运行时间最高可达 3 倍,每个许可证最多支持 8 个处理器 分布式综合,支持单机或多机应用 静态时序分析和报告,用于衡量设计性能,并进行反向注释,以关联布局布线后的性能。 集成 Identify RTL 调试器,可快速查找功能错误 故障注入和调试支持,用于衡量安全性和高可靠性特性的有效性 HDL Analyst 交互式图形分析和调试工具用于设计诊断、问题隔离以及功能和性能分析 通过 HDL Analyst 和分层调试流程进行高级设计调试和诊断 FSM Compiler 和 FSM Explorer 用于从 RTL 中自动提取和优化有限状态机 与 VCS® 和 Verdi 集成 支持脚本和 Tcl/Find,用于流程自动化以及可自定义的综合、调试和报告 More Information in English: Synopsys Synplify FPGA 2025.03 SP1 Win/Linux64

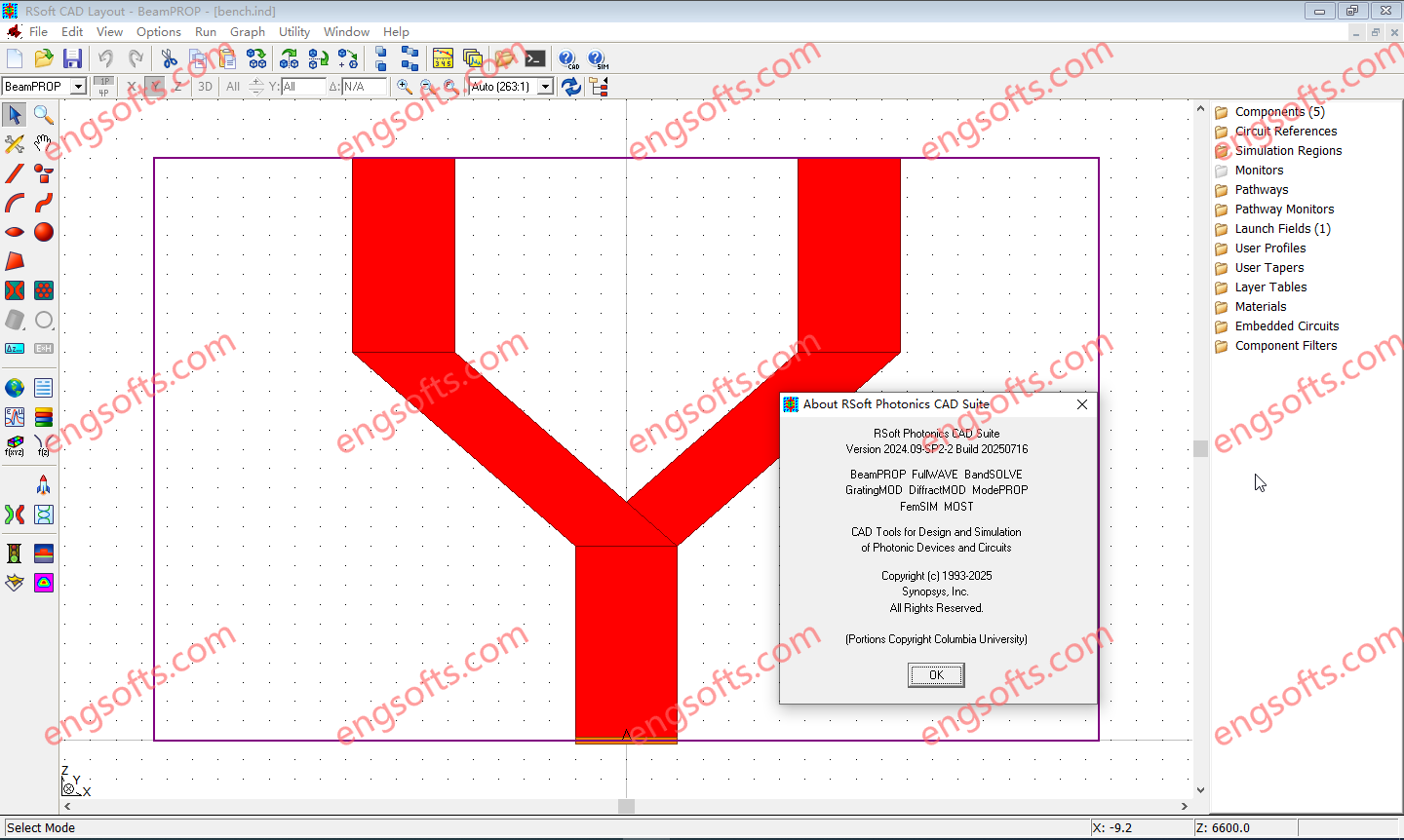

Synopsys 正在通过无缝、统一的设计平台加速光子 IC 技术的应用,帮助 IC 设计师和光子工程师在各种硅光子和光纤应用中进行创新并取得成功。借助 Synopsys 解决方案,设计团队可以使用业界领先的电子和光子设计软件,从而提高生产效率、精度并加快产品上市速度。 Synopsys 光子解决方案包括:光子集成电路(Linux64 下的 Synopsys OptoCompiler)、光子系统(Synopsys OptSim)和光子器件(RSoft 光子器件工具)。 RSoft 光子器件工具包含业界最全面的被动和主动光子及光电器件(包括激光器和垂直腔面发射激光器)仿真器和优化器产品组合。 RSoft 光子器件工具包含 FullWAVE FDTD、BeamPROP BPM、DiffractMOD RCWA、FemSIM FEM、BandSOLVE、GratingMOD、RSoft CAD、LaserMOD、MetaOptic Designer 以及各种实用程序和选项。 Synopsys RSoft Photonic Device Tools 2024.09 Tested Picture Synopsys OptSim 允许用户在信号传播层面设计和模拟当前和下一代光通信系统。 Synopsys OptSim 2024.09 Tested Picture 我们与 Synopsys 的光学和半导体设计工具集成,可实现简化的多域协同仿真: Synopsys CODE V 和 LightTools 产品,用于对纳米纹理光学结构进行严格建模和衍射分析 Synopsys Sentaurus TCAD 产品,用于对复杂光电器件进行仿真 这些先进的工具增强并加速了用户的建模能力,并利用广泛的行业规范提供真实的现场设计场景。我们的用户包括光学元件和设备制造商、系统集成商、服务提供商,以及政府实验室和学术机构。无论您是希望最大限度地提高性能、最大限度地降低成本、缩短产品上市时间、快速原型制作,还是分析光通信系统的多种“假设”场景,这些工具都将成为您不可或缺的合作伙伴,并助您取得成功。 Synopsys OptoCompiler 是业界首个统一的电子和光子设计平台,它将成熟且专用的光子技术与 Synopsys 久经考验的电子设计工具相结合,使工程师能够快速准确地生成和验证复杂的 PIC 设计。 Synopsys OptoCompiler 在单一平台上提供原理图驱动的布局和高级光子布局综合功能,弥合了光子专家和 IC 设计师之间的鸿沟,使光子设计与数字设计一样高效。 RSoft 光子器件工具 2024.09 版本新增功能 More Information in English: Synopsys RSoft Photonic Solutions 2024.09 Win/Linux64

ImSym – Imaging System Simulator, a groundbreaking virtual prototyping platform for imaging systems, encompassing lenses, sensors, and image signal processors (ISPs). By integrating components of the imaging chain into a comprehensive end-to-end simulation platform, ImSym enables tailored optimizations of any imaging system, facilitates team collaboration, and dramatically reduces the risks of issues in later development stages. With accuracy powered by industry-proven CODE V® and LightTools® optical design software and a quantitative end-to-end simulation flow, ImSym reduces the need for physical prototypes and delivers simulations that can directly translate into production-ready designs. Synopsys ImSym 2024.09 Tested Picture Enhance Your Optical System Development with ImSym Visualize images with precise, quantitative data Streamline your development process Deliver your next great imaging product to...

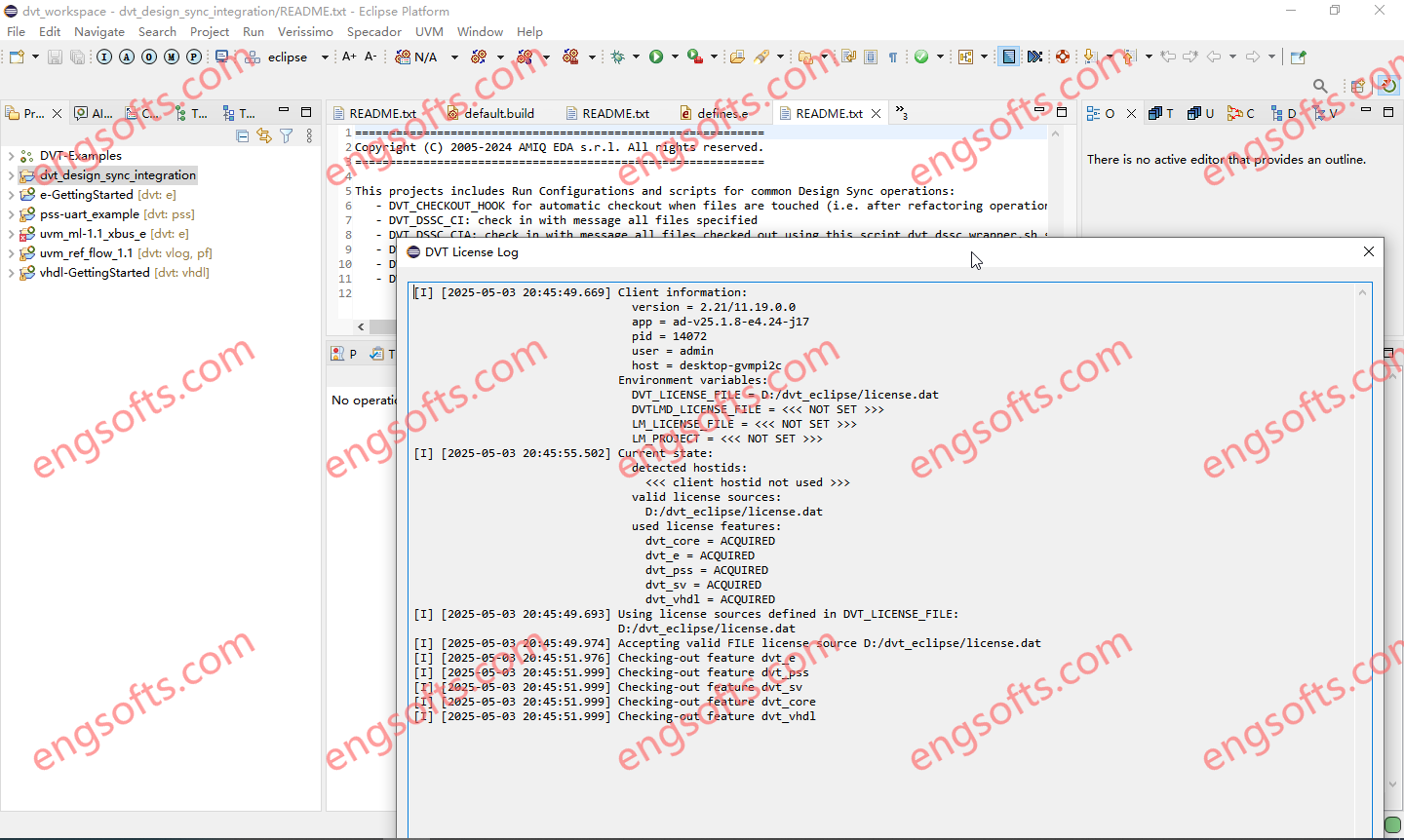

Design and Verification Tools (DVT) IDE is an integrated development environment for Verilog, SystemVerilog, Verilog AMS, VHDL, UPF, CPF, e Language, and PSS, helping design and verification engineers significantly improve their productivity. Available versions: 25.x ,24.x ,23.x ,… AMIQ DVT Eclipise IDE 2025 v25.1.8 Win/Linux Tested Picture Unlike plain text editors providing regular expression-based capabilities, DVT IDE compiles the code and signals errors as you type, speeds up code writing using auto-complete and quick-fix proposals, and allows you to find anything you are looking for instantly. DVT IDE enables engineers to overcome the limitations of plain text code editors and address today’s project complexity more efficiently. It enables faster and smarter code development and simplifies legacy code maintenance for novices...

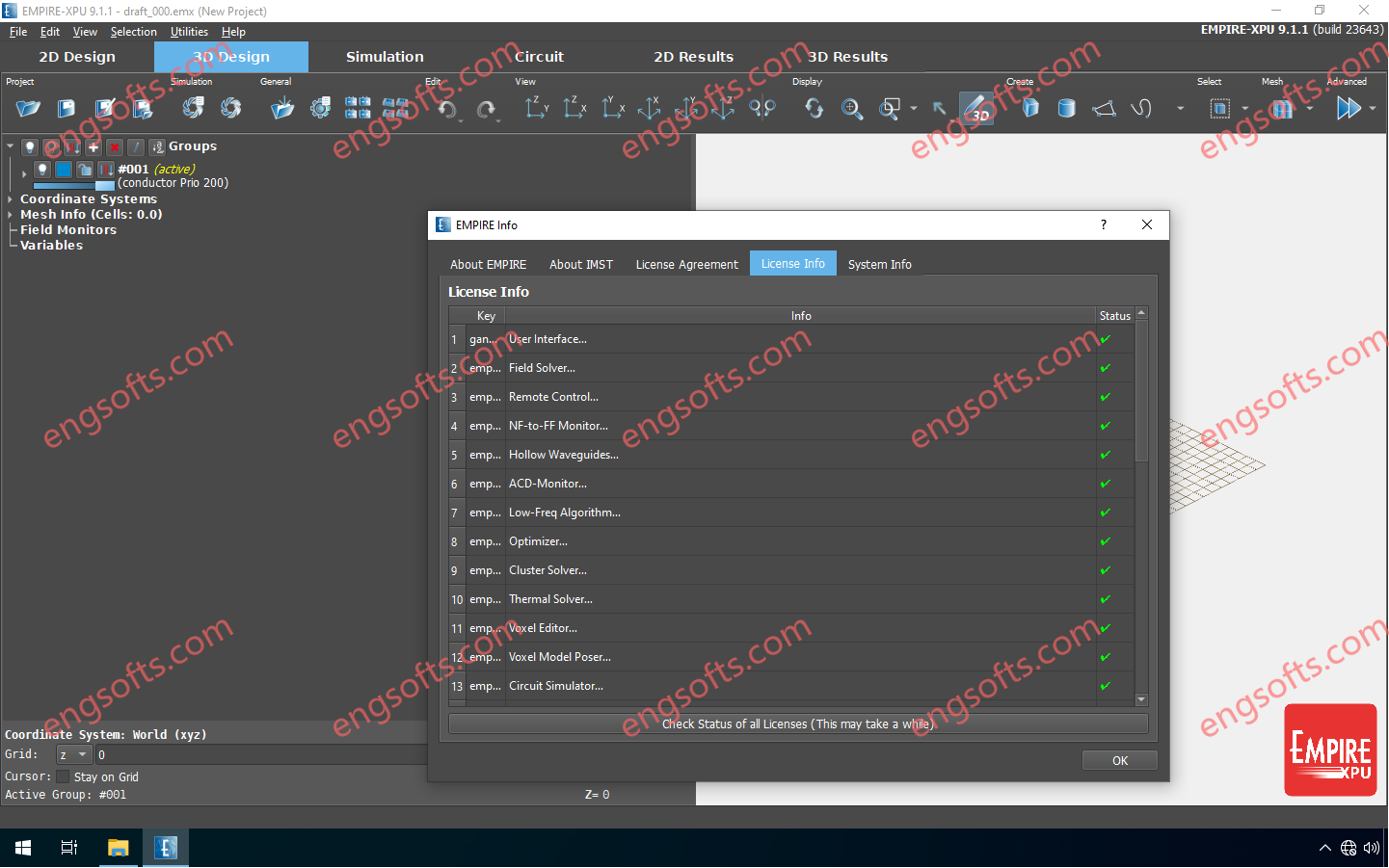

Empire XPU build antenna arrays, multi-layered circuits, EMC/EMI, work on radar analysis, thermal analysis, biomedical applications and many more. Available versions: 9.1.x , 9.0.x , 8.2.x , 8.0.x … EMPIRE XPU 9.1.1 Tested Picture The new major update 9.1.0 is now available. Many enhancements were integrated in the latest version. Please note the end of support (EOS) of version 8.2.x and previous releases. EM Twin Add-On Automatic Mesh Accuracy and Quality Check New KMF – Scripting interface Windows 11 support GUI: Limit jobs in Remote Server Use Display Port Numbers in Group List New Internal Variables for Frequency and Wavelength Inclusion of Logo in Design Modes More robust Save/Load of emx-projects Material Database Update Import and Export of View Setting...

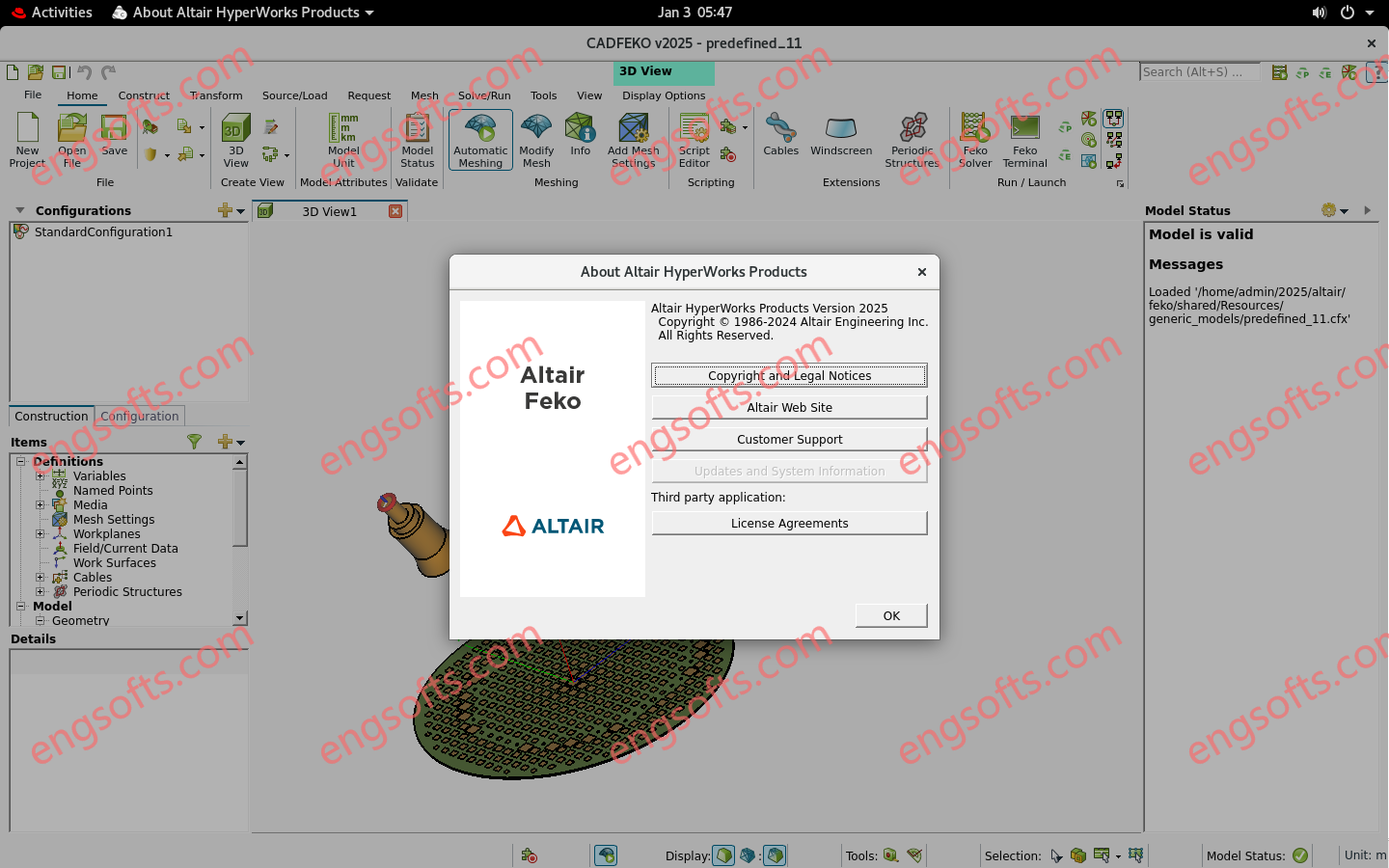

Altair Feko is the leading tool for antenna design, placement and coupling, virtual test drives and flights, radio frequency interference, radar and radio coverage and planning, and spectrum management. Feko uniquely combines installed antenna performance with wireless coverage analysis, and its hybridized and parallelized solvers handle complex and electrically large analysis problems. Available versions: 2025.x , 2024.x , 2023.x , 2022.x , 2021.x , 2020.x Altair FEKO 2025.0 Linux64 Tested Picture Additionally, Feko offers specialized wave propagation technologies and models through its Altair® WinProp™ and Altair® WRAP™ capabilities. WinProp is especially useful for detailed, urban, and indoor radio-coverage planning, network roll-out, and comparative design deployment needed for heterogeneous outdoor-indoor scenarios. WRAP supports network coverage, planning, colocation, and interference analysis and...

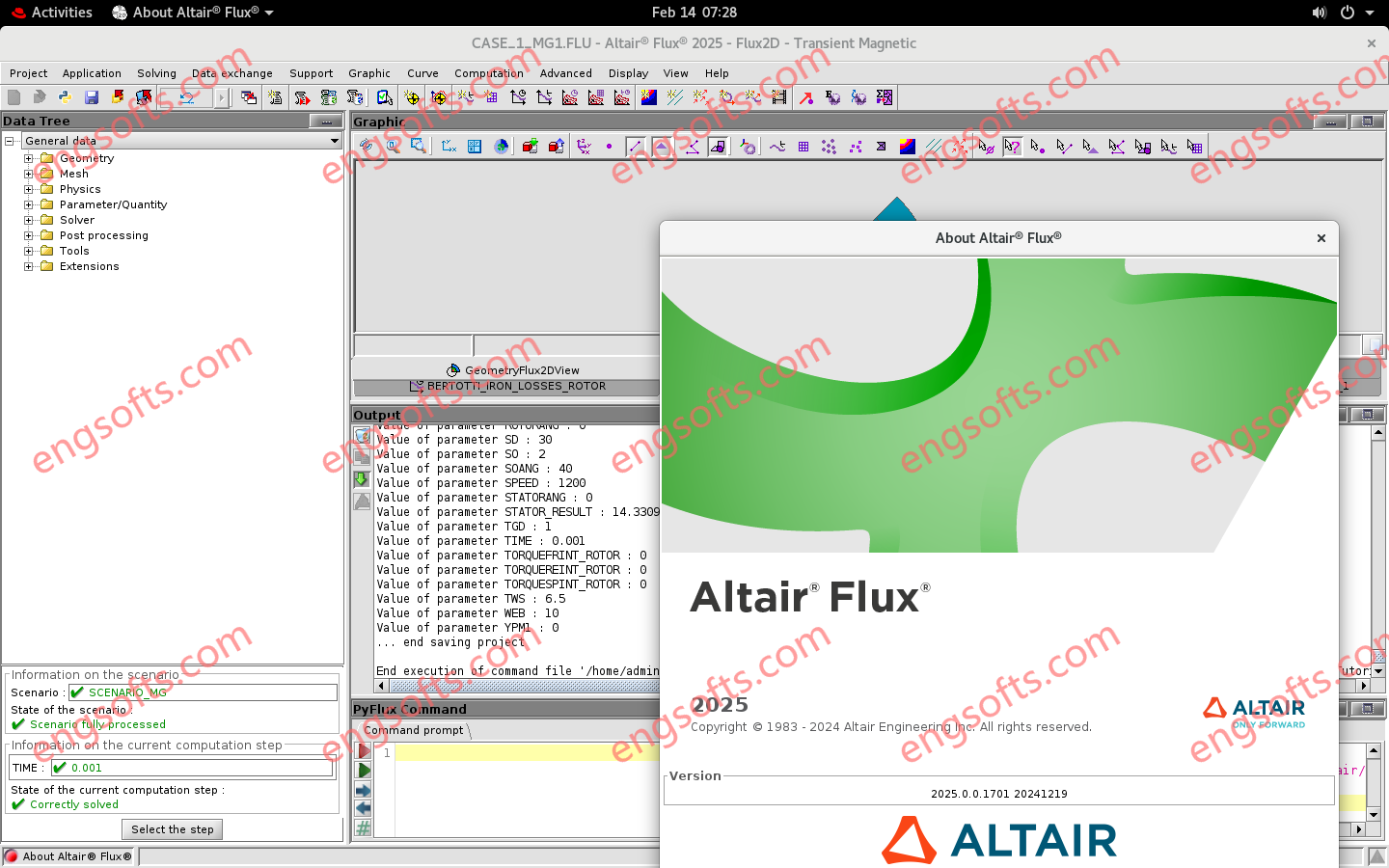

Altair Flux models even the most complex electromechanical systems with proven accuracy. It provides multiphysics capabilities – magneto static, steady-state, and transient conditions, along with electrical and thermal properties – to optimize machine performance, efficiency, dimensions, cost, and weight, and it is used to develop sensors and actuators, in addition to high-power electrical equipment including transformers, insulator, power bars, and circuit breakers. Available versions: 2025.x , 2024.x , 2023.x , 2022.x ,… Altair Flux 2025.0 Linux64 Tested Picture Flux is used widely across multiple industries such as transportation, electrical equipment, and consumer goods to develop more efficient electrical systems with higher levels of connectivity. Flux addresses the broadest set of electromagnetic, electric, and thermal simulations, and is closely linked to...

StarVision® PRO represents the state-of-the-art in debug solutions for advanced electronic SoCs. The incorporation of Concept’s leading visualization and detection technology enables rapid cause-effect analysis for efficient functional analysis. This advanced and unique mixed-mode debug platform seamlessly combines SPICE and transistor analysis from our market leading SpiceVision PRO tool with digital RTL and gates from our advanced RTLvision PRO tool. It is fully customizable and incorporates many advanced features not available in other debug solutions, to handle the most complex of SoC platforms. Available other versions: 2024.x , 2023.x , 7.1.x , 6.x , 5.x Altair StarVision PRO 2025.0 Win Tested Picture StarVision PRO 2025 is a major release, the following features were fixed and/or added: Show the logic value...

GateVision® PRO is the third generation of graphical, gate-level netlist analyzers and viewers from Concept Engineering. Completely rewritten to run on modern 64bit platforms to handle the largest designs and SoCs, GateVision PRO provides a range of powerful debug and comprehension capabilities. These include intuitive design navigation, netlist viewing, waveform viewing, logic cone extraction, interactive logic cone viewing for netlist debugging and design documentation. Available other versions: 2024.x , 2023.x , 7.1.x , 6.x , 5.x Altair GateVision PRO 2025 Win Tested Picture GateVision PRO 2025 is a major release, the following features were fixed and/or added: Show the logic value at the mouse position in the tooltip of the Wave window. Speed-up displaying the members of large vectors in the Wave window. Add...

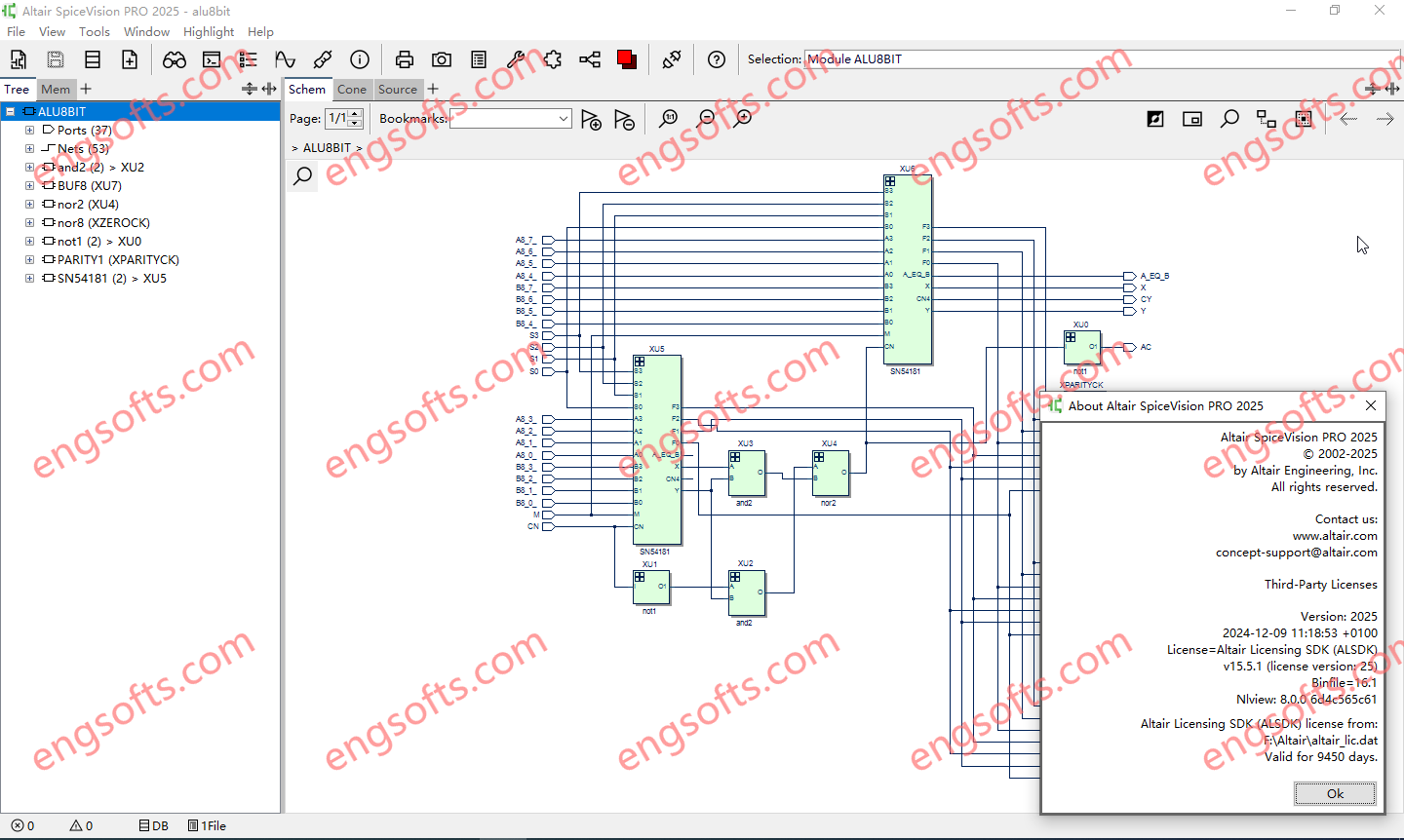

SpiceVision PRO takes SPICE netlists and models and generates clean, easy-to-read transistor-level schematics, circuit fragments, and design documentation to speed up circuit design, debug, and optimization at the transistor-level. Available other versions: 2024.x , 2023.x , 7.1.x , 6.x , 5.x Altair SpiceVision PRO 2025.0 Win Tested Picture SpiceVision PRO 2025, the following features were fixed and/or added: Add new GUI API commands gui tab showPlusMenu and gui tab hidePlusMenu to control the display of the “+” tab to add new windows. Add new GUI API commands gui tab showSplitControl and gui tab hideSplitControl to control the display of the buttons to split the window. Add new GUI API commands gui settings addDialog and gui settings removeDialog to add and remove a custom tab to the Preferences dialog. Add new GUI API command gui cone disableUpdate to disable the update of highlights and attributes...