ALINT-PRO 2025.12 为混合语言项目提供了一套全新的设计规则和指南。此次更新旨在帮助工程团队在单个项目中结合使用 VHDL 和 Verilog/SystemVerilog 时,提高代码的正确性、可维护性和 IP 互操作性。

可用版本: 2025.x , 2024.x ,…

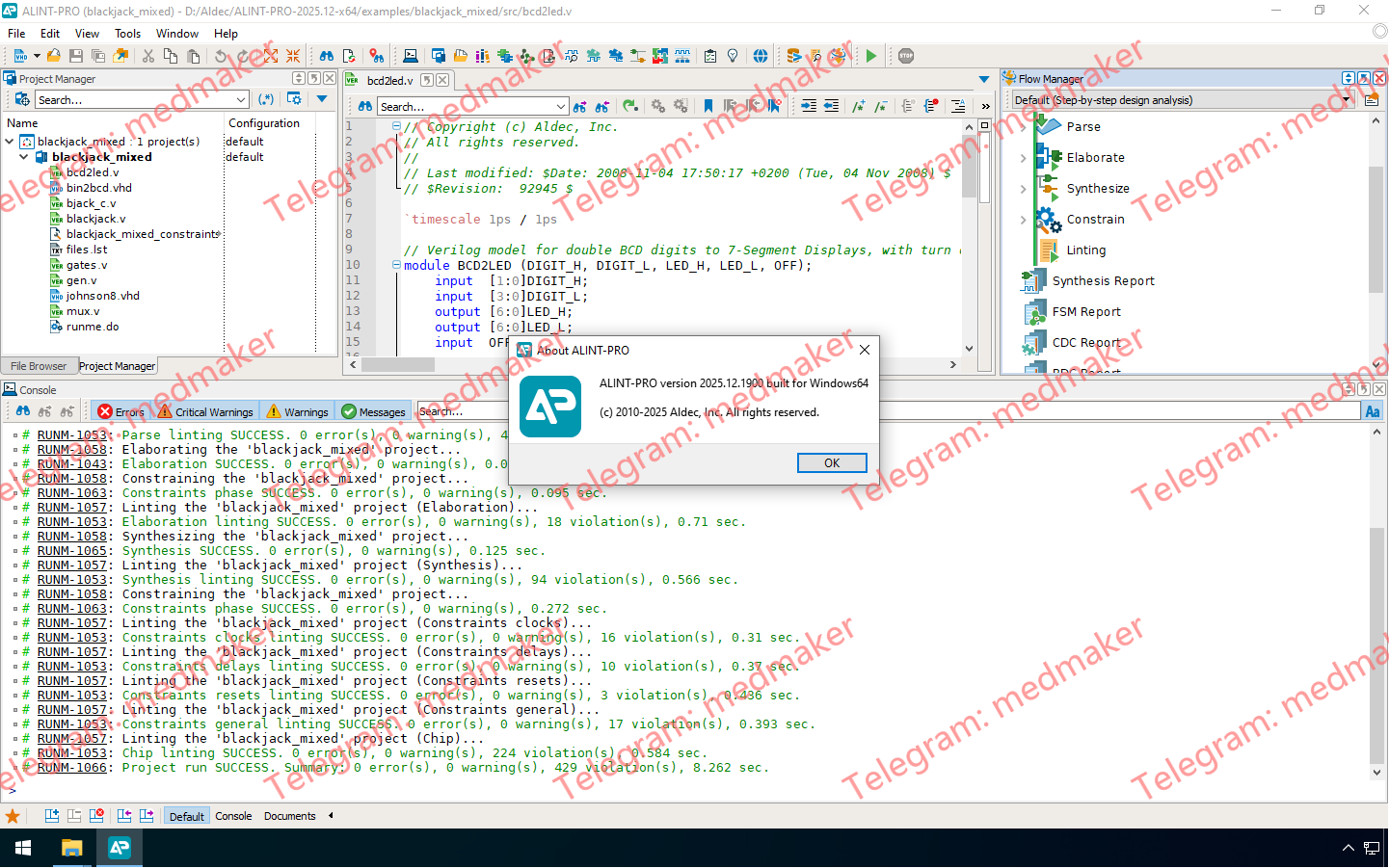

Aldec ALINT-PRO 2025.12 Tested Picture

随着混合语言开发在IP复用、第三方集成和长期产品维护方面日益普及,设计团队面临着映射歧义、参数传递不一致和配置误用等挑战。ALINT-PRO 2025.12 通过一套旨在预防仿真、综合和下游验证之前集成问题的最佳实践规则,有效降低了这些风险。

ALINT-PRO 2025.12 高级规则库中的全新混合语言设计规则

全新的 ALINT-PRO 2025.12 规则为跨语言边界的模块/实体实例化建立了一套一致的方法。规则如下:

在 VHDL 中实例化 Verilog 模块

- 在 VHDL 中实例化 Verilog 模块时,请使用基于组件的实例化方法。

- 不要在 VHDL 配置结构中配置 Verilog 模块。

- 不要在 RTL 描述中使用组件规范来定义 Verilog 模块。

- Verilog 单元名称与其 VHDL 实例名称之间区分大小写。

- 在 VHDL 中实例化 Verilog 单元时,请使用显式端口关联。

- 即使参数未更改,也要将所有参数传递给 VHDL 中的 Verilog 单元实例。

在 Verlog 中实例化 VHDL 单元

- 在 Verlog 中实例化 VHDL 单元时,请使用显式端口关联。

- 即使参数未更改,也要将所有参数传递给 Verilog 中的 VHDL 单元实例。

- 请勿在 Verilog 中使用 defparam 来覆盖 VHDL 实例化参数。

- 对在 Verilog 中实例化的 VHDL 单元使用允许的通用映射。

- 对在 Verilog 中实例化的 VHDL 单元使用允许的端口映射。

它们保持不变。

这些规则旨在减少跨语言解释差异,确保一致的细化行为,并明确设计意图,从而提高仿真、代码检查和综合流程中混合语言集成的成功率。

More Information in English: Aldec ALINT-PRO 2025.12 Tested Video