Active-HDL is a Windows based, integrated FPGA design creation and simulation solution for team-based environments. Active-HDL’s integrated design environment (IDE) includes a full HDL and graphical design tool suite and RTL/gate-level mixed-language simulator for rapid deployment and verification of FPGA designs. The design flow manager evokes 200+ EDA and FPGA tools, during design entry, simulation, synthesis and implementation flows and allows teams to remain within one common platform during the entire FPGA development process. Active-HDL supports industry leading FPGA devices from AMD, Intel, Lattice, Microchip, Quicklogic and more. Top Features and Benefits Project Management Unified Team-based Design Management maintains uniformity across local or remote teams Configurable FPGA/EDA Flow Manager interfaces with 200+ vendors tools allows teams to remain on one...

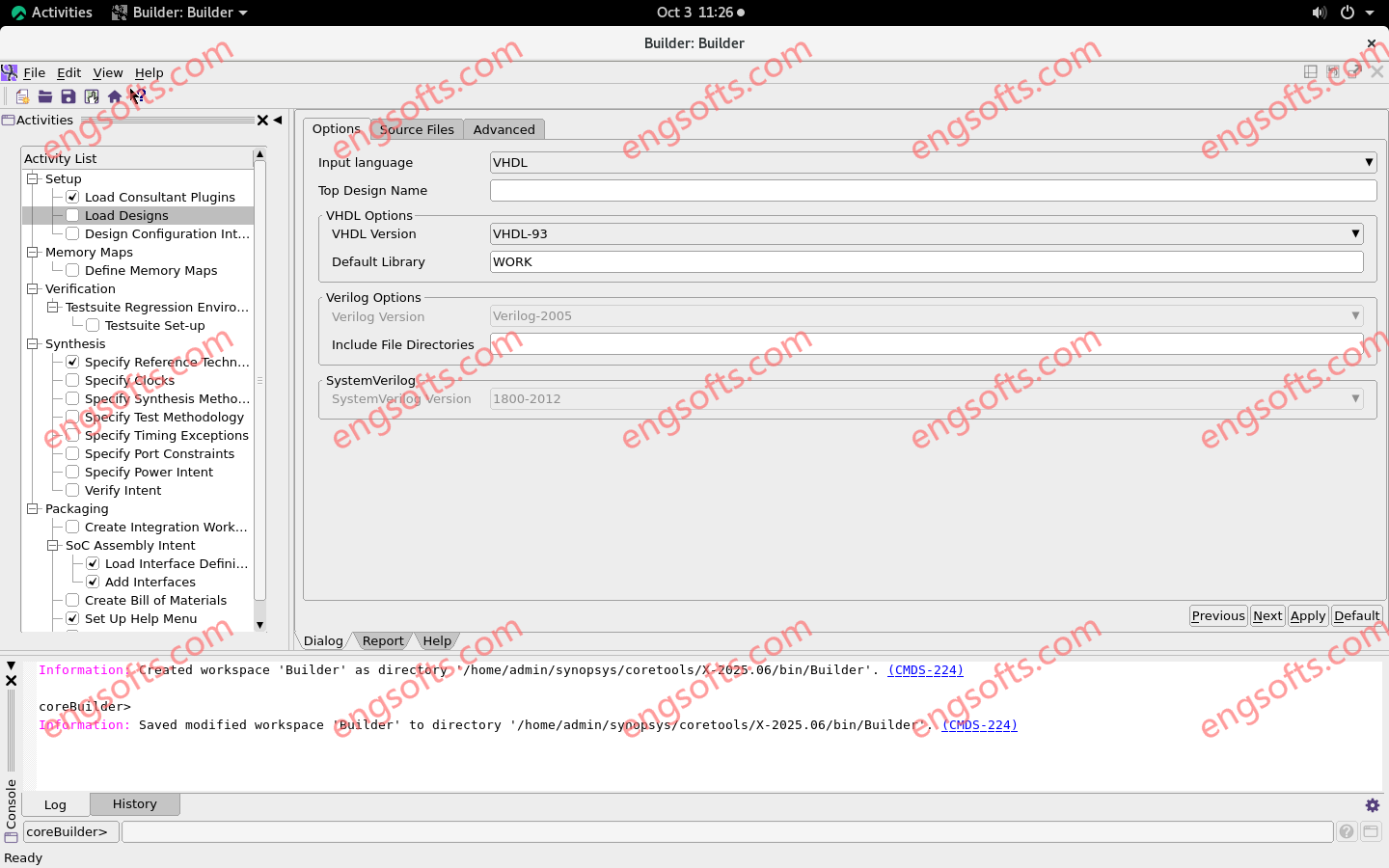

The coreConsultant tool guides core integrators through the automated installation, configuration, and synthesis of single reusable synthesizable components. The coreAssembler tool allows core integrators to assemble multiple components into a subsystem. The tool provides reliable, error-free subsystem netlist generation, design configuration and high-quality synthesis of the subsystem. It also provides auto-connection, egister map generation, testbench generation, and simple test builds for DesignWare® Library components. The coreBuilder tool guides the core developer through packaging a core or design for reuse with coreConsultant or coreAssembler. The coreBuilder tool captures a developer’s detailed knowledge of design characteristics and packaging requirements in a technology-independent package, enabling core integrators to easily configure and synthesize the core across a wide range of target technologies. Available versions:...

ID:softmed

ID:softmed ID:956575828

ID:956575828