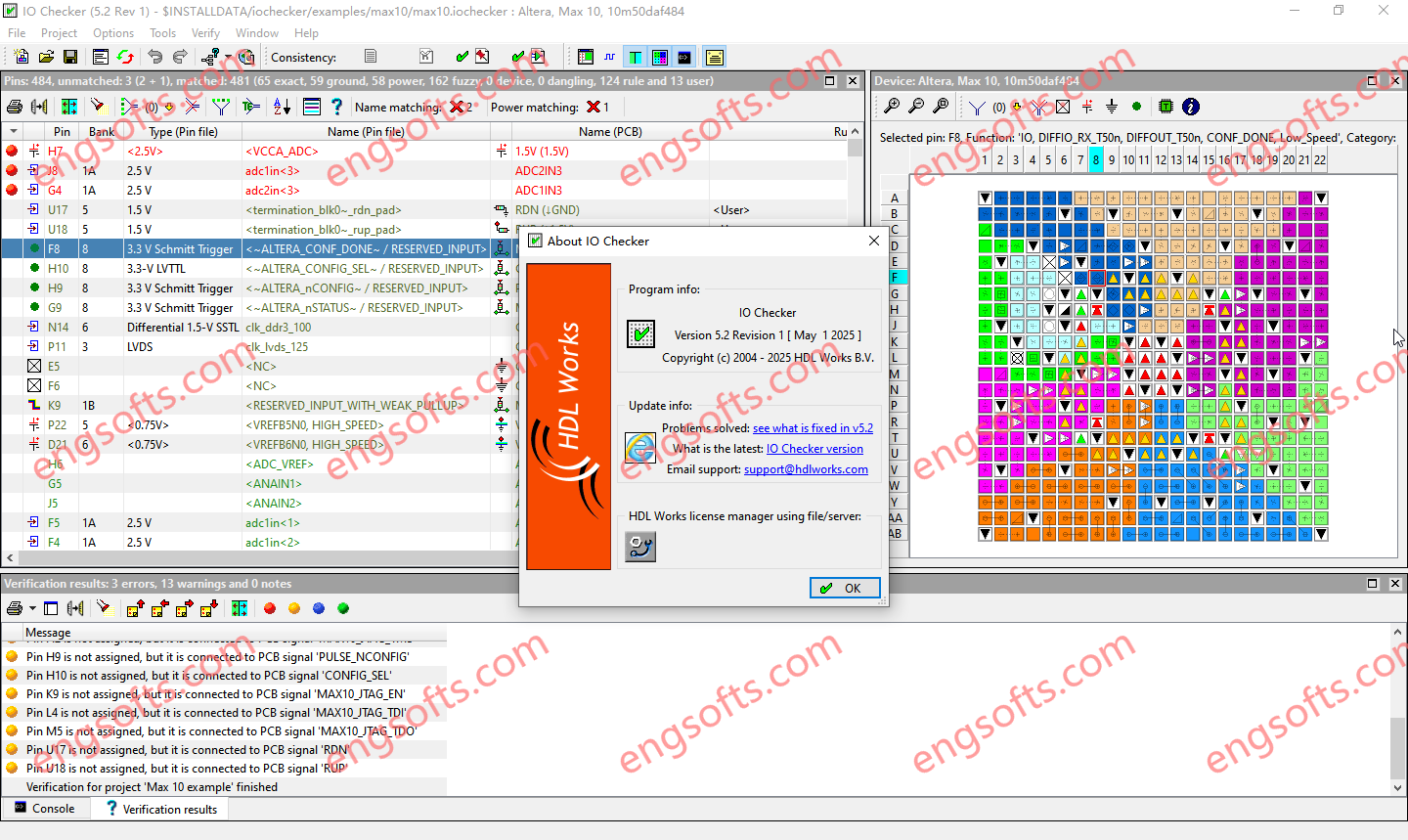

IO Checker 使用基于正则表达式的规则来匹配 FPGA 和 PCB 设计环境中的信号名称。即使单个信号可能存在差异,该工具也能验证匹配组。这些规则可以自动生成,也可以由设计人员进行微调。自动化方法通常可以匹配 80% 到 90% 的器件引脚。 可用版本: 5.2.x , 5.1.x ,… HDL Works IO Checker 5.2 Rev1 Win/Linux IO Checker 的灵活性使其可用于任何设计流程,无需任何设计方法论。规则生成器结合排序后的问题视图,使工程师能够在半小时内验证一个拥有 1000 多个引脚的器件。 一旦定义了项目及其规则,保持 FPGA 和 PCB 数据的一致性就变得非常简单。所有过期的文件都会一次性处理,并且所有更改都会被报告。 功能与优势 使用正则表达式比较 FPGA 和 PCB 引脚名称 创建 &更新 FPGA 约束文件 自动生成规则 电源引脚电压检查 用户可自行确认已验证的差异 一键验证和一致性检查 报告引脚列表和网络列表中的增量更改 专注于十几个差异,而不是上千行代码 适用于任何设计流程 HTML 报告 What is new in the 5.2 release More Information in English: HDL Works IO Checker 5.2

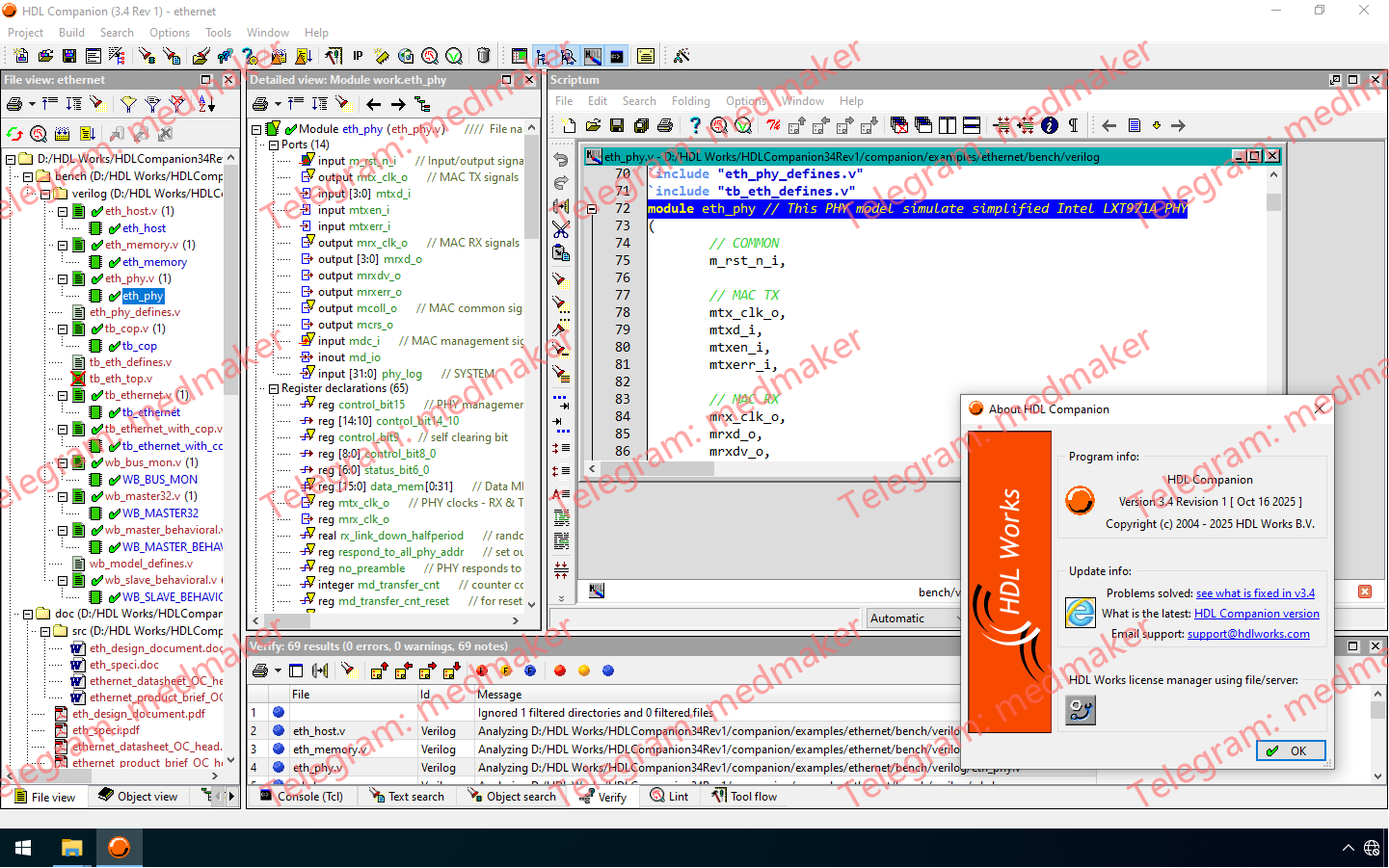

HDL Companion 是 HDL 设计师的瑞士军刀。它能帮助您快速掌握并维护任何 HDL 设计的概览,包括第三方 IP、遗留代码和其他 HDL 源文件。只需将完整的设计目录和设计文件拖入 HDL Companion,即可在几秒钟内生成完整的设计概览,揭示设计的各个方面。其图形用户界面 (GUI) 提供了多种导航方式,方便您浏览设计并查找所需细节。 可用版本: 3.4.x , 3.3.x ,… HDL Works HDL Companion 3.4 Rev1 Win/Linux Tested Picture 内置的模糊解析器可以接受任何 SystemVerilog、VHDL 或混合 HDL 设计代码;即使代码不完整或包含错误。语法正确的 HDL 代码也可以进行代码检查,以发现编译器未报告的问题。 HDL Companion 采用独特的布局,包含三个主窗口和一个控制台窗口,它们共同提供从高层结构到源代码细节的完整设计概览。其出色的导航功能(包括信号跟踪)使您可以轻松查找对象并查看其详细信息。 控制台窗口显示所有语法错误和警告,您可以使用从控制台窗口到 Scriptum 窗口的热链接轻松地在 HDL 源代码中找到它们。控制台窗口还可以用作 Tcl 解释器,可以在其中执行任何 Tcl 脚本或 shell 命令。 What is new in 3.4 More Information in English: HDL Works HDL Companion 3.4

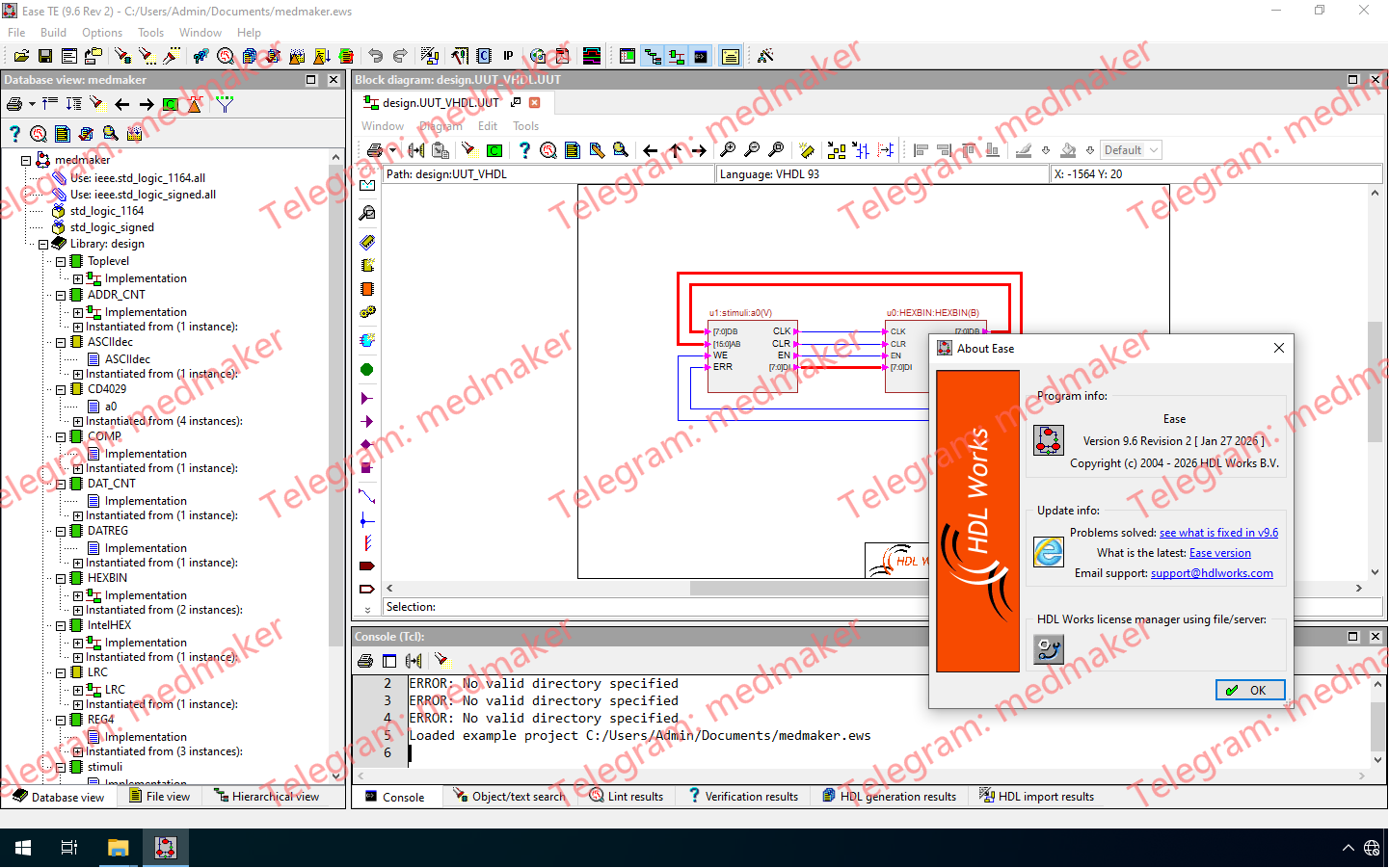

EASE 兼具图形化和文本化两种 HDL 输入方式,让您可以自由选择。您无需精通 Verilog 或 VHDL。创建新设计时,只需使用图形和文本混合方式输入即可。EASE 会自动为您生成所选语言(VHDL 或 Verilog)的优化 HDL 代码。行业标准的版本控制环境可处理设计和配置管理,支持多个用户同时在同一个 EASE 项目中工作。 可用版本: 9.6.x , 9.5.x ,… HDL Works EASE 9.6 Rev2 Win/Linux Tested Picture 功能与优势 图形化设计环境,可自动生成分层 VHDL 或 Verilog 代码 符合以下标准: – VHDL:IEEE-1076 87、93 等2008 – Verilog:IEEE-1364 95、2001、2005 – SystemVerilog:IEEE-2005、2009、2012、2017 虚拟记录可降低图表复杂性并提高灵活性 真正的多用户设计环境和相关的版本控制,由功能强大的设计环境浏览器管理 一键导入旧版 Verilog 或 VHDL 设计并提取图形层次结构 与业界最流行的仿真器和综合工具无缝集成 平台无关的数据库 集成 HDL 语言编辑器 实时错误报告 What is new in the 9.6 release More Information in English: HDL Works EASE 9.6

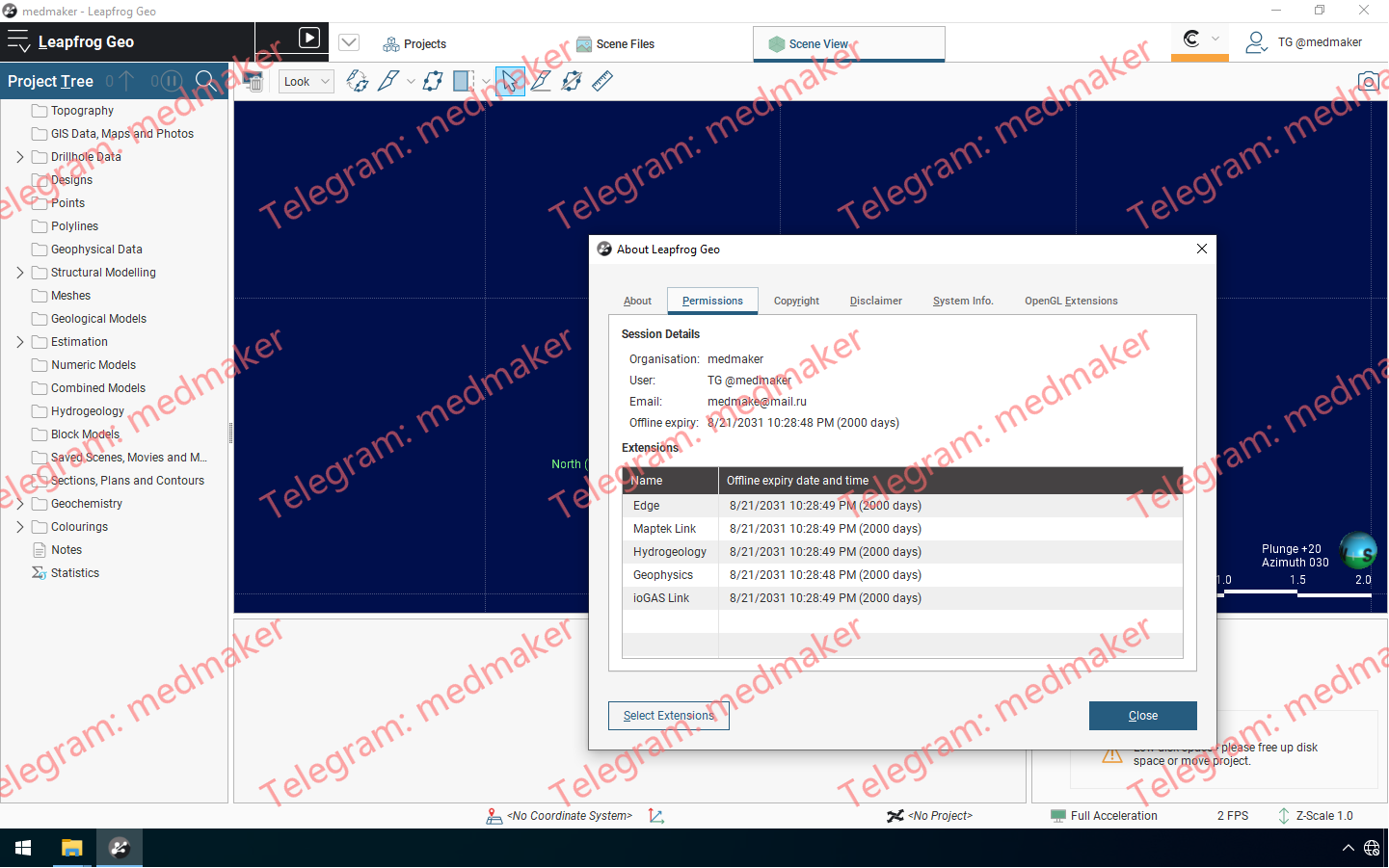

Leapfrog Geo/Works/Energy 帮助您可视化和理解数据,以便您可以与各个技术级别的利益相关者沟通风险,并在所有土木工程和环境项目中做出更明智的决策。 可用版本: 2025.3.x ,… Seequent Leapfrog Geo/Works/Energy 2025.3.1 Tested Picture 节省您的解读时间 通过简化的工作流程,改变您查看和处理数据的方式。快速生成剖面图,并使用可将模型与工程设计集成的工具。 通过快速创建和更新地质模型,提高您的 3D 地下建模效率。随着新数据的输入,您的模型和输出(例如剖面图)会动态更新,无需重新创建,从而节省时间和成本。 3D 地下建模在理解地质条件方面提供了无与伦比的精度和效率。更好地识别和评估项目生命周期各个阶段的风险,并及早发现挑战。 清晰沟通 以 3D 形式查看地下信息,即使是复杂的数据也能清晰呈现,从而加深您的理解。 高度可视化的 3D 地下模型有助于您更好地解读地质条件。使用包括 Leapfrog Viewer 和视频在内的免费可视化工具,清晰地向所有利益相关者传达风险,并导出高质量图像和剖面图布局,用于报告和演示。 与所有团队协作 Leapfrog Works 支持行业标准的地质勘察数据格式。您还可以将地质模型与工程设计、BIM 工作流程和地下水流模型相结合,从而全面了解您的项目。 在制定有关地质条件的关键决策时,让地质学家参与其中。将您的地质信息模型与建筑信息模型相结合,并与其他团队协作,共同开发基础设施信息模型。 More Information in English: Seequent Leapfrog Geo/Works/Energy 2025.3.1 Testing Viseo