Tessent Silicon Lifecycle Management solutions include advanced debug, safety & security features and in-life data analytics to meet the evolving challenges of today’s silicon lifecycle. Ensure the highest test quality, accelerate yield ramp and improve safety, security and reliability across the silicon lifecycle using best-in-class solutions for design-for-test (DFT), debug and in-life monitoring plus powerful data analytics. Tessent Advanced DFT Address the challenges of in-system test for today’s complex SoCs and chiplets with market-leading logic and memory test products that combine capabilities in a powerful test flow to ensure total chip coverage. Tessent Embedded Analytics Close productivity gaps using actionable insights from embedded analytics that shorten total development time, accelerate debug and reduce risk and cost to ensure timely market...

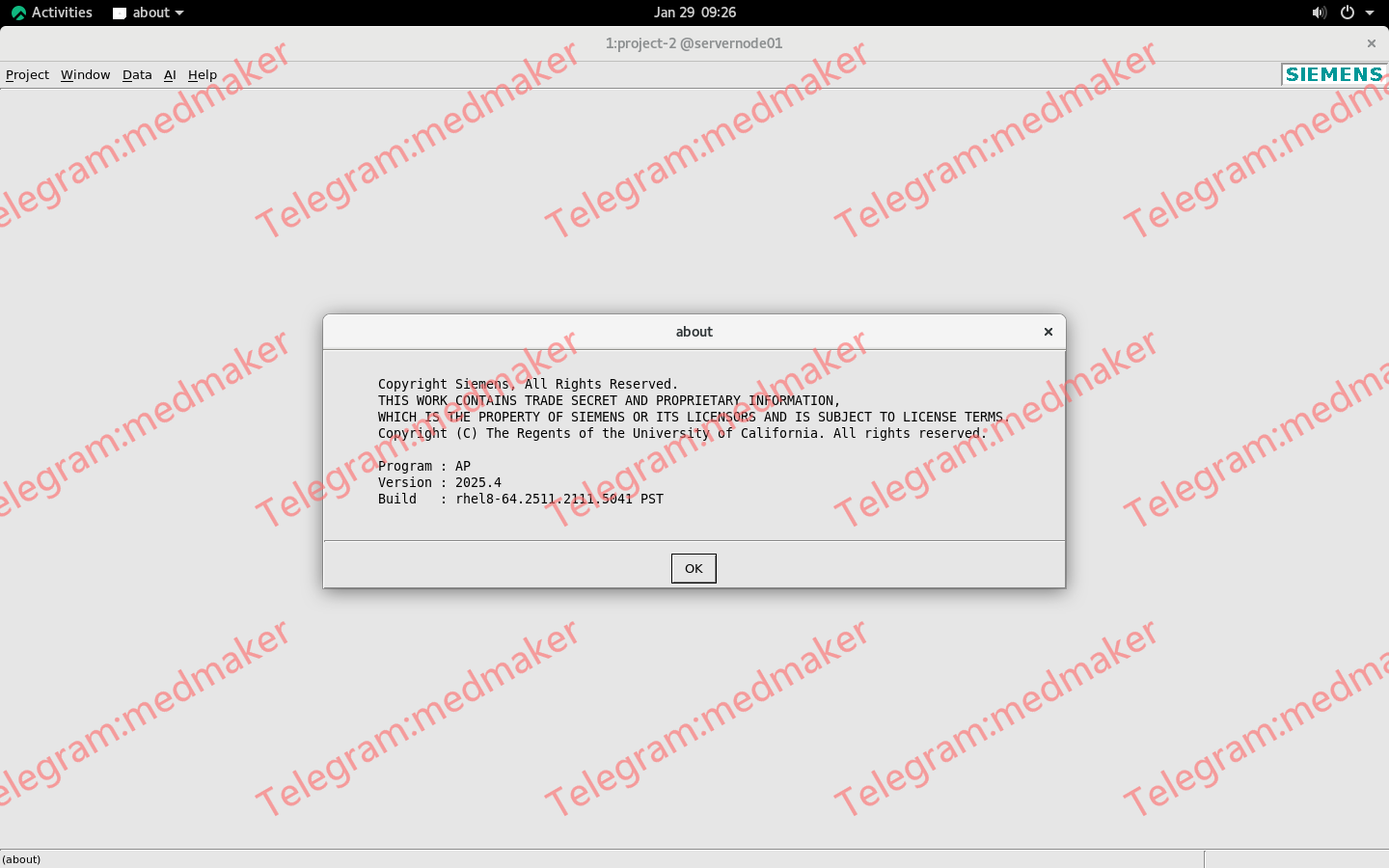

Aprisa 是一款面向现代 SoC 的以详细布线为中心的物理设计解决方案。无论您的目标是加快流片速度、降低总体拥有成本,还是实现最低功耗,Aprisa 都凭借其专利技术和一流的支持,确保您取得成功。 Aprisa 为复杂的数字 IC 设计提供完整的顶层分层设计和模块级实现功能。其以详细布线为中心的架构和分层数据库,能够在极具竞争力的运行时间内实现快速设计收敛和最佳结果质量 (QoR)。 可用版本:2025.x , 23.x , … Siemens Aprisa 2025.4 Linux Tested Picture 缩短设计收敛时间 统一的数据模型将真实的布线信息和寄生参数引入流程中的任何引擎和步骤。设计人员可以在布线前阶段就自信地了解其设计可实现的功耗、功耗和功耗比 (PPA),从而大幅减少全流程迭代次数。 AI 驱动的宏布局技术 只需经验丰富的设计师所需时间和精力的一小部分,即可实现专家级设计师品质的宏布局。无需进行全流程迭代即可锁定给定设计的最佳宏布局。 低功耗专利技术 将低功耗作为功耗敏感型设计的主要设计指标,同时不牺牲性能。设计人员可以选择满足其最佳 PPA 的权衡方案,从而减少流片最后阶段的功耗清理工作。 More for English: Siemens Aprisa 2025.4 Linux

Solido Design Environment is a comprehensive AI-powered design environment for all SPICE-level design and verification, and is a single unified solution for nominal and variation analysis. Used by thousands of designers to produce the most competitive products in hp computing, AI, IoT, automotive and mobile applications. Brute force-accurate signoff variation 1000X faster Orders of magnitude faster than brute-force simulation Full coverage verification across PVTs and Monte Carlo Brute-force Monte Carlo and SPICE accurate high-sigma verification Variation-aware design sensitivity, debugging and optimization Comprehensive design environment to boost engineering efficiency Significantly reduces documentation time/effort Identifies design weaknesses previously undetectable Easy to use and deploy Intuitive GUI for interactive design and analysis GUI or batch mode Works with all process technologies Integrated with...

Precision offers vendor-independent FPGA synthesis. It provides best-in-class performance and area, high-reliability design capabilities and tight links to simulation and formal equivalency checking. Siemens offers three unique FPGA synthesis solutions – Precision Hi-Rel, Precision RTL Plus and Precision RTL. Precision’s products are tightly integrated with Siemens’ FormalPro LEC for equivalency checking and HDL Designer for design capture and design verification using ModelSim/Questa. Precision RTL Precision RTL, Siemens entry-level FPGA synthesis product, offers best-in-class quality of results with a vendor-independent FPGA synthesis solution. Precision RTL Plus Precision RTL Plus, adds DO-254 certification utilities for mil-aero applications, on-chip debug and validation and resource optimization for DSPs and RAMs. Precision Hi-Rel Precision Hi-Rel, enhances Precision RTL Plus with automated mitigation of SEUs/SETs in...

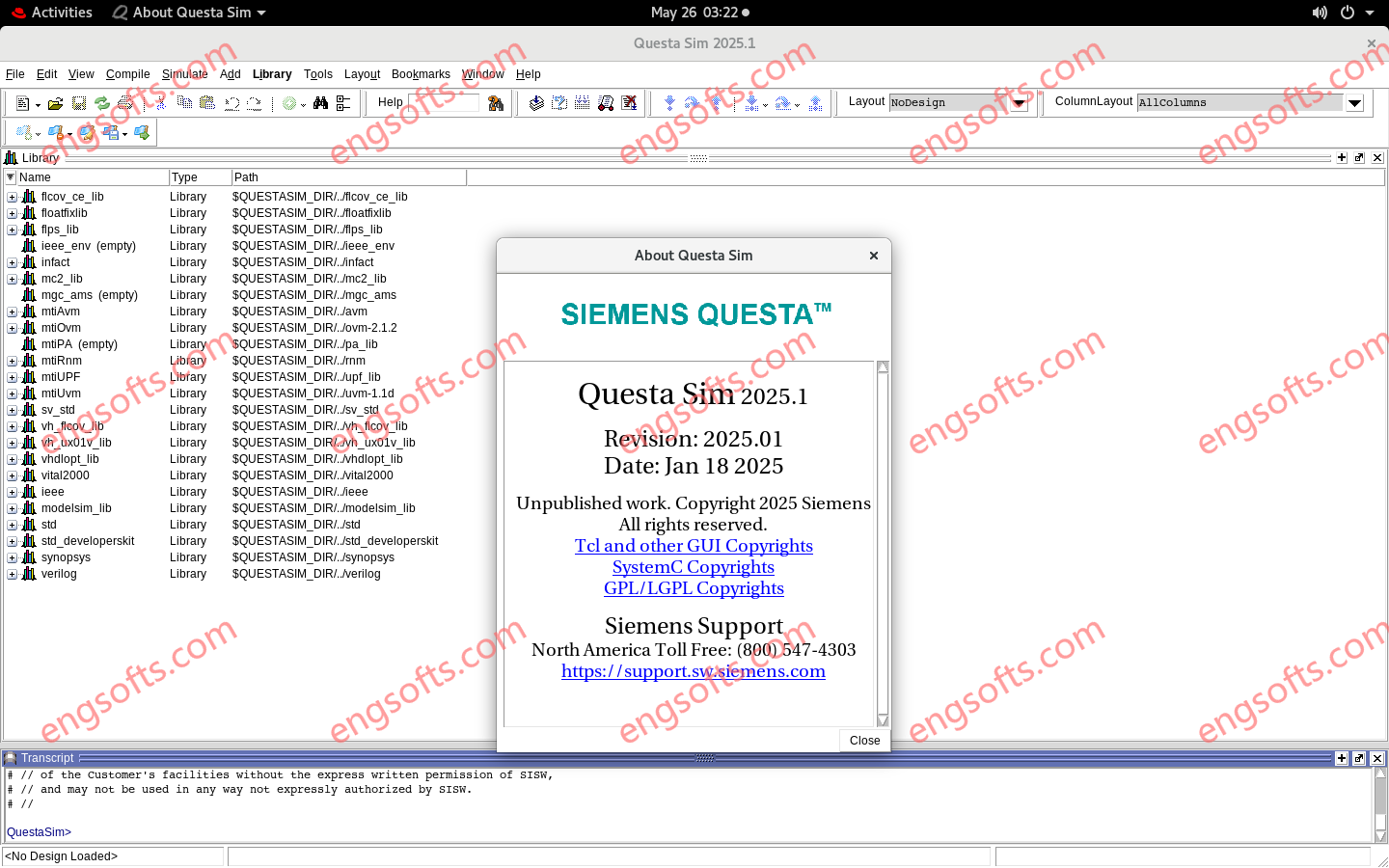

The Questa advanced simulator is the core simulation and debug engine of the Questa verification solution; the comprehensive advanced verification platform capable of reducing the risk of validating complex FPGA and SoC designs. Available other versions: 2024.1 ,10.7 Siemens Questa Advanced Simulator 2025.1 Linux Tested Picture The QuestaSim verification solution delivers on these requirements for complex SoC designs. QuestaSim achieves industry-leading performance and capacity through aggressive, global compile and simulation optimization algorithms for SystemVerilog, VHDL, and SystemC. Meanwhile, its Questa Visualizer debug environment provides high-performance, high-capacity debugging for dramatic regression throughput improvements when running large test suites. QuestaSim Benefits Industry-leading high performance multi-language simulator High-performance, high-capacity unified debug Reference simulator for LRM compatibility UVM, SystemVerilog, VHDL, SystemC, and mixed language...

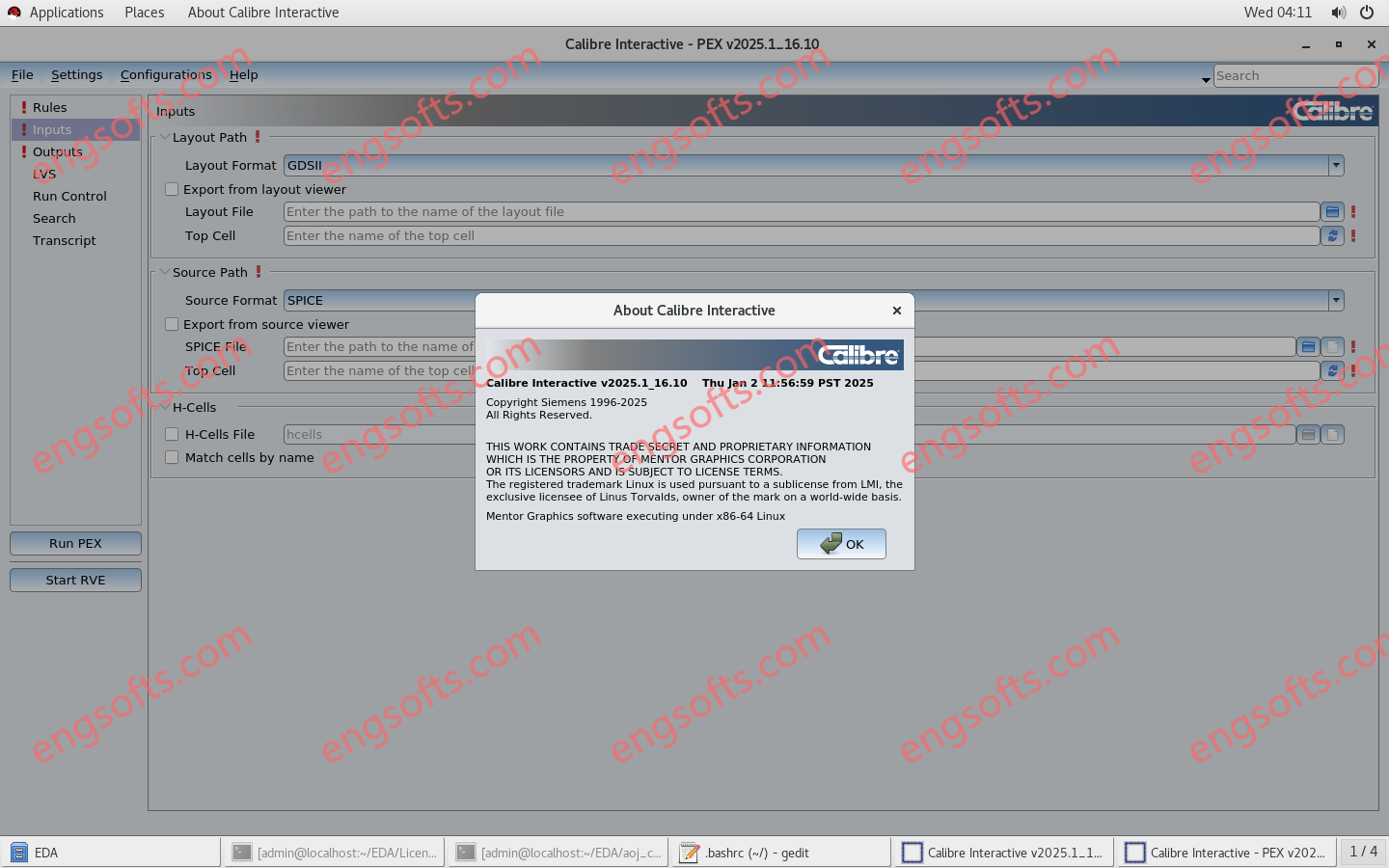

Calibre Design Solutions is the industry leader for IC verification, delivering a complete IC verification and DFM optimization EDA platform that speeds designs from creation to manufacturing, addressing all sign-off requirements. Siemens Calibre 2024.2 Linux Tested Picture Calibre Design Solutions Portfolio Calibre Design Solutions delivers the most accurate, most trusted, and best-performing IC sign-off verification and DFM optimization in the EDA industry. Calibre Physical Verification The Calibre nmDRC Platform provides foundries, IDMs, and fabless companies with comprehensive, innovative verification technology for all nodes and processes. Calibre Circuit Verification The industry-leading Calibre circuit verification toolsuite includes layout vs. schematic (LVS) checking, reliability verification, and parasitic extraction. Calibre Reliability Verification Calibre reliability verification performs checks against electrical and physical design rules and...

Siemens.com IC-Custom 2024.3 is an enterprise-ready, custom IC design flow for innovative designs supporting both FinFET and planar analog, analog mixed-signal. With over 30 years of experience and thousands of design tape outs, this platform is well suited for “More than Moore” designs. Custom IC Design 2024 Release Highlights

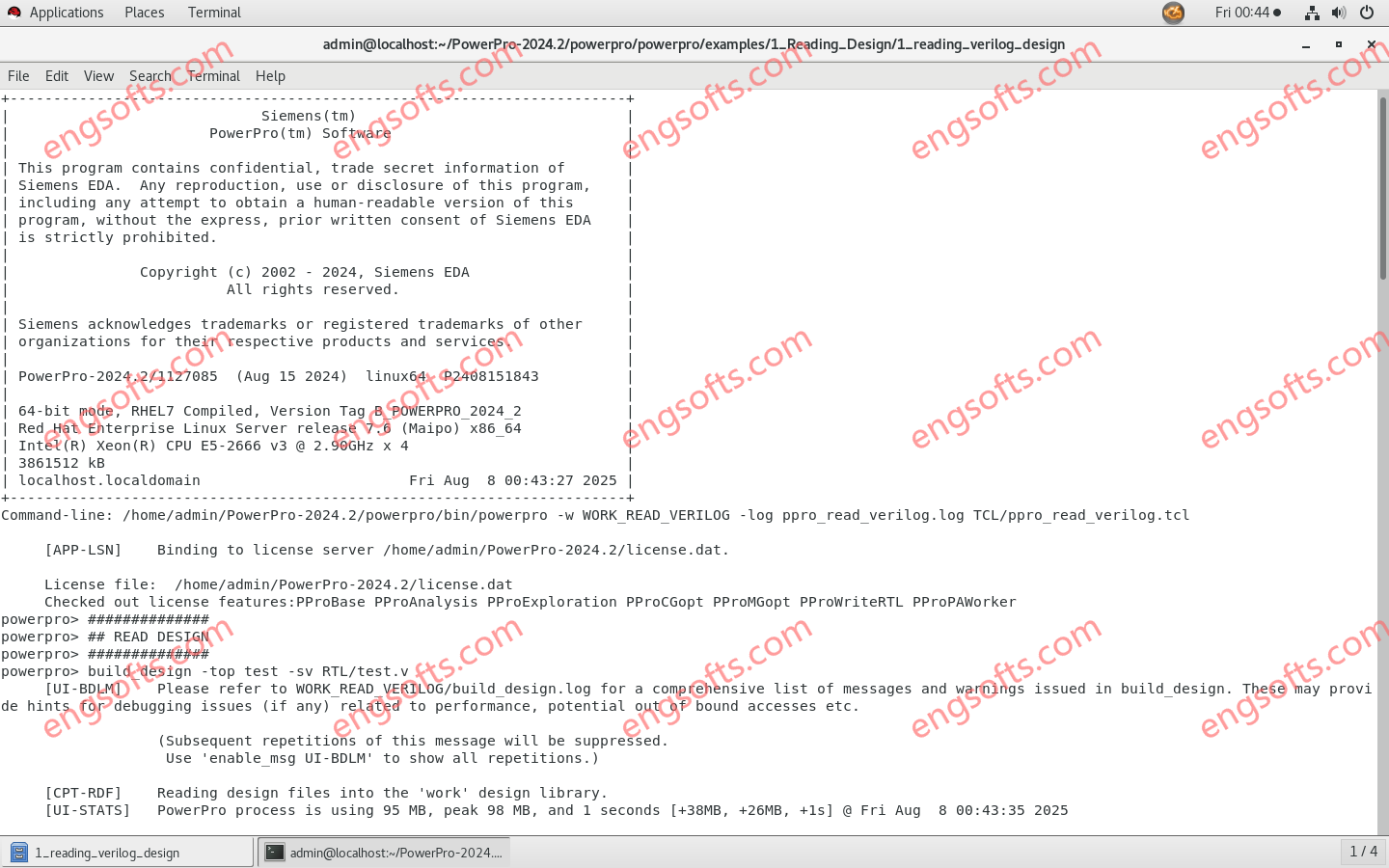

PowerPro offers the most comprehensive set of features to RTL designers to “design-for-low-power”. It offers power estimation for both RTL and Gate-level designs, early power checks to quickly find power issues during RTL development and clock and memory gating to optimize the design for power. Available versions: 2024.2 , 2022.1 , … Siemens PowerPro 2024.2 Linux Tested Picture PowerPro Power Analysis & Optimization Platform PowerPro offers the most comprehensive set of features to RTL designers to “design-for-low-power”. It offers power analysis for both RTL and gate-level designs, early power checks to quickly find power issues during RTL development and clock and memory gating to optimize the design for power. RTL Power Estimation PowerPro RTL Power Estimation delivers highly accurate estimations...

Tanner, part of Siemens EDA’s Custom IC design solution, is packed with new features and improvements. Further product details L-Edit IC L-Edit is a complete hierarchical physical layout tool with cross-probe to schematic, layout and LVS & full integration with Calibre.Read more S-Edit Increases productivity for complex IC design, links to analog mixed simulation and schematic driven layout .Read more Tanner Calibre® One DRC/LVS/xRC The Tanner-Calibre One IC verification suite is an integral part of the Tanner analog/mixed-signal (AMS) physical design environment, creating an easy path to the proven capabilities of Calibre verification tools.Read more Tanner Designer Tanner Designer helps teams easily track analog verification throughout the entire design cycle.Read more Tanner Digital Implementer Integrated, flexible digital synthesis and place...

Catapult has the broadest portfolio of hardware design solutions for C++ and SystemC-based High-Level Synthesis (HLS). Catapult’s physically-aware, multi-VT mode, with Low-Power estimation and optimization, plus a range of leading Verification solutions make Catapult HLS more than just “C to RTL”. Catapult High-Level Synthesis Solutions Catapult High-Level Synthesis solutions deliver C++ and SystemC language support, FPGA and ASIC independence, ASIC power estimation and optimization plus the latest in Physically aware multi-VT area and performance optimization to elevate your designs. C++/SystemC Synthesis A comprehensive HLS flow taking C++ or SystemC as the design input and optimally targeting ASIC, eFPGA or FPGA implementations tuned for frequency and target technology. Low-Power Solutions When it comes to early design space exploration, power estimation, and...