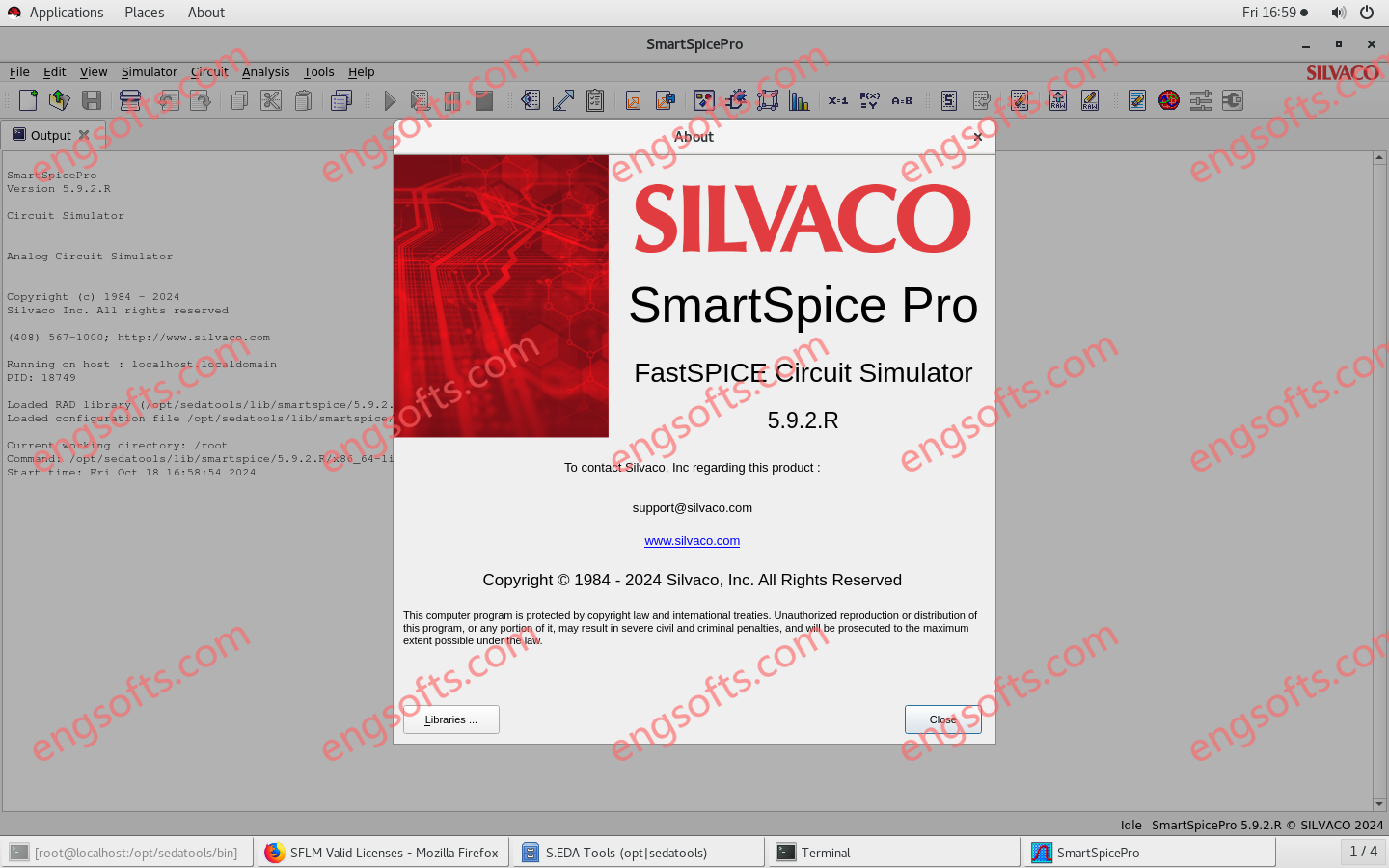

Silvaco offers a full IC-CAD design flow including design capture, circuit simulation, layout design, physical verification, parasitic extraction and reduction, and post-layout analysis including statistical variation, and yield analysis. Silvaco SmartSpice Pro 2024 v5.9.2 Linux64 Tested Picture Schematic Editor Gateway is a highly productive environment with intuitive editing, capacity to support large and complex hierarchical or flat designs, ability to automatically generate symbols from existing legacy netlists and support for industry standard netlist and interface formats. It features tight integrations to Silvaco TCAD and analog custom design tools. Layout Editor Expert is a hierarchical IC layout editor featuring high capacity and flexible use across many silicon technologies in analog, mixed-signal, RF and digital circuits. As a key part of Silvaco’s custom IC...

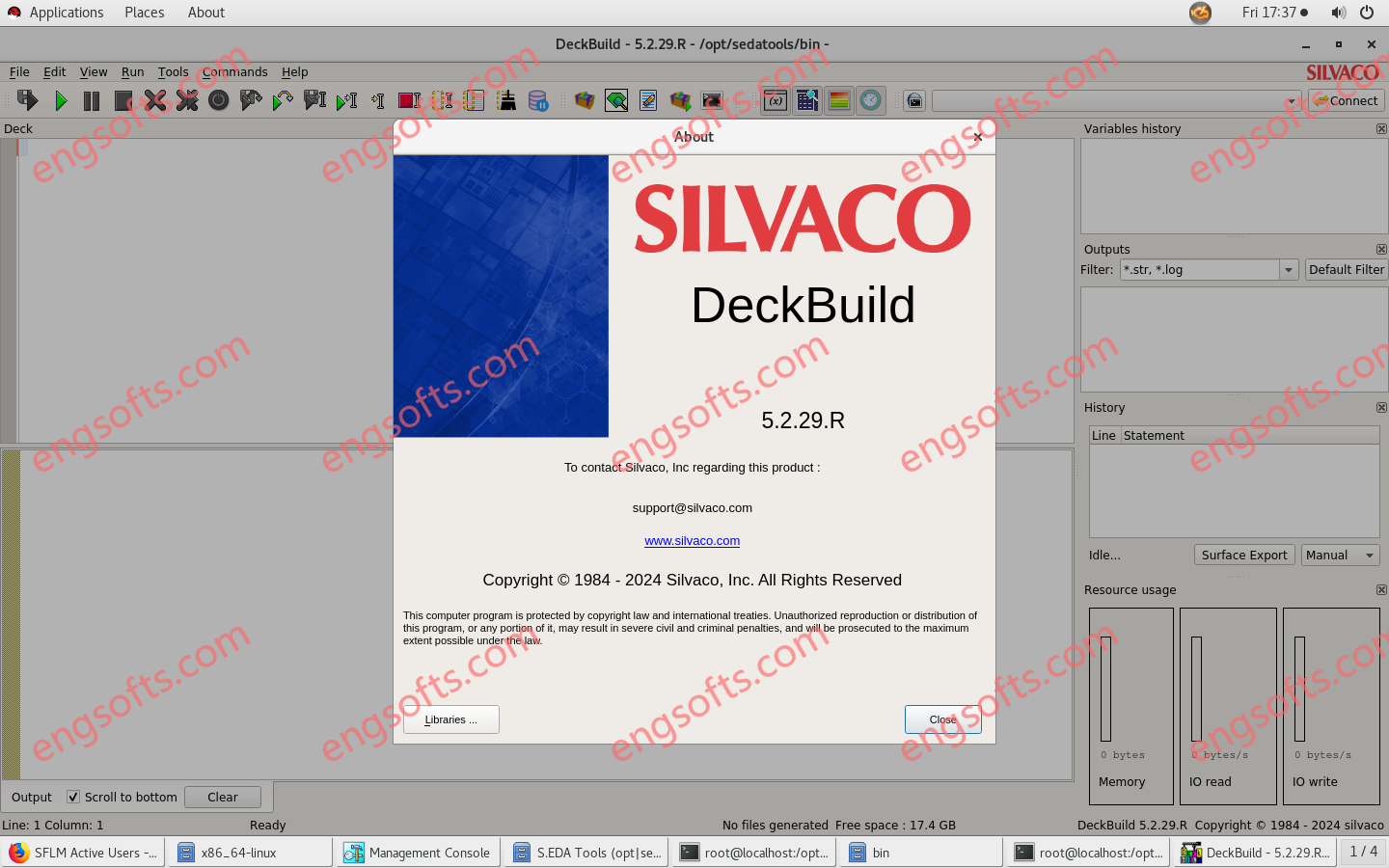

TCAD software solutions are key to developing new semiconductor processes and devices, dramatically reducing costs and time to market.The package includes Victory TCAD,Legacy + Interconnect and Utmost IV. Silvaco DeckBuild 2024 v5.2.29 Linux64 Tested Picture Reduce Development Costs Reduce the time and manufacturing cycles spent to develop semiconductor technologies ITRS roadmaps indicates that TCAD simulation can reduce the costs during development cycles by ~30% Silvaco Tonyplot 2024 v3.10 Linux64 Tested Picture Visualize Internal Physical Processes Using simulation, you can see ‘inside” the device. Experimental measurements tell you what happens, but not why it happens. TCAD can tell you why. For example: Reverse voltage characterization on a power device tells you what happens at high reverse biases. The device experiences reverse breakdown at a specific voltage A TCAD...

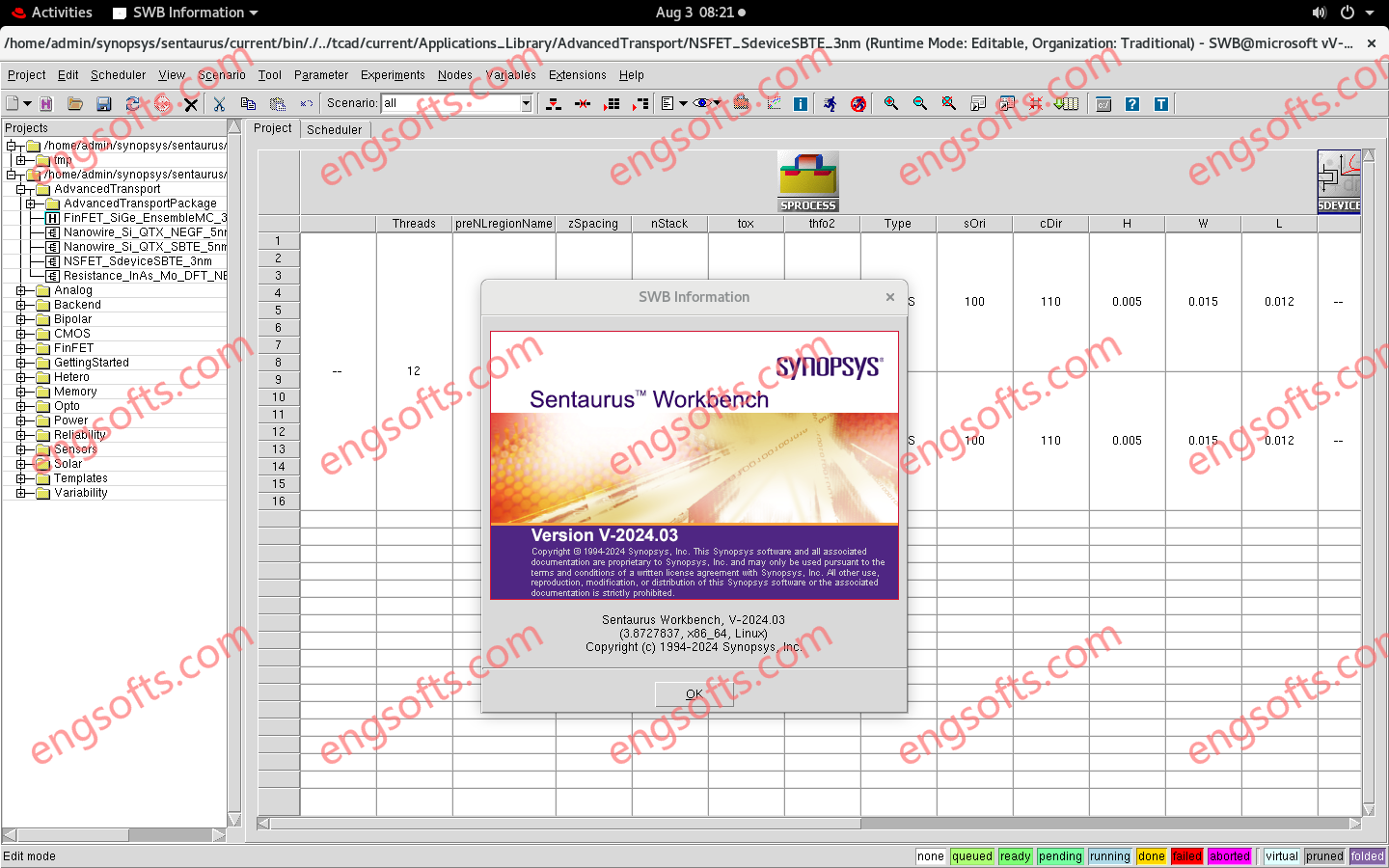

Sentaurus is a suite of TCAD tools which simulates the fabrication,operation and reliability of semiconductor devices. The Sentaurus simulators use physical models to represent the wafer fabrication steps and device operation, thereby allowing the exploration and optimization of new semiconductor devices. The Sentaurus TCAD tools work seamlessly and can be combined into complete simulation flows in 2-D and 3-D.Sentaurus TCAD supports silicon and compound semiconductor technologies, covering a broad range of semiconductor applications. Synopsys Sentaurus TCAD 2024.03 Linux Tested Picture Key Applications: CMOS, FinFET Memory (DRAM, NVM) Power Devices (Si, SiC, GaN) RF Devices (GaAs, InP, GaN) Optoelectronics (CIS, Solar Cells,Photodetectors) BEoL Reliability Value of Sentaurus TCAD in Technology Development and Optimization Semiconductor manufacturers face the challenge of developing process...

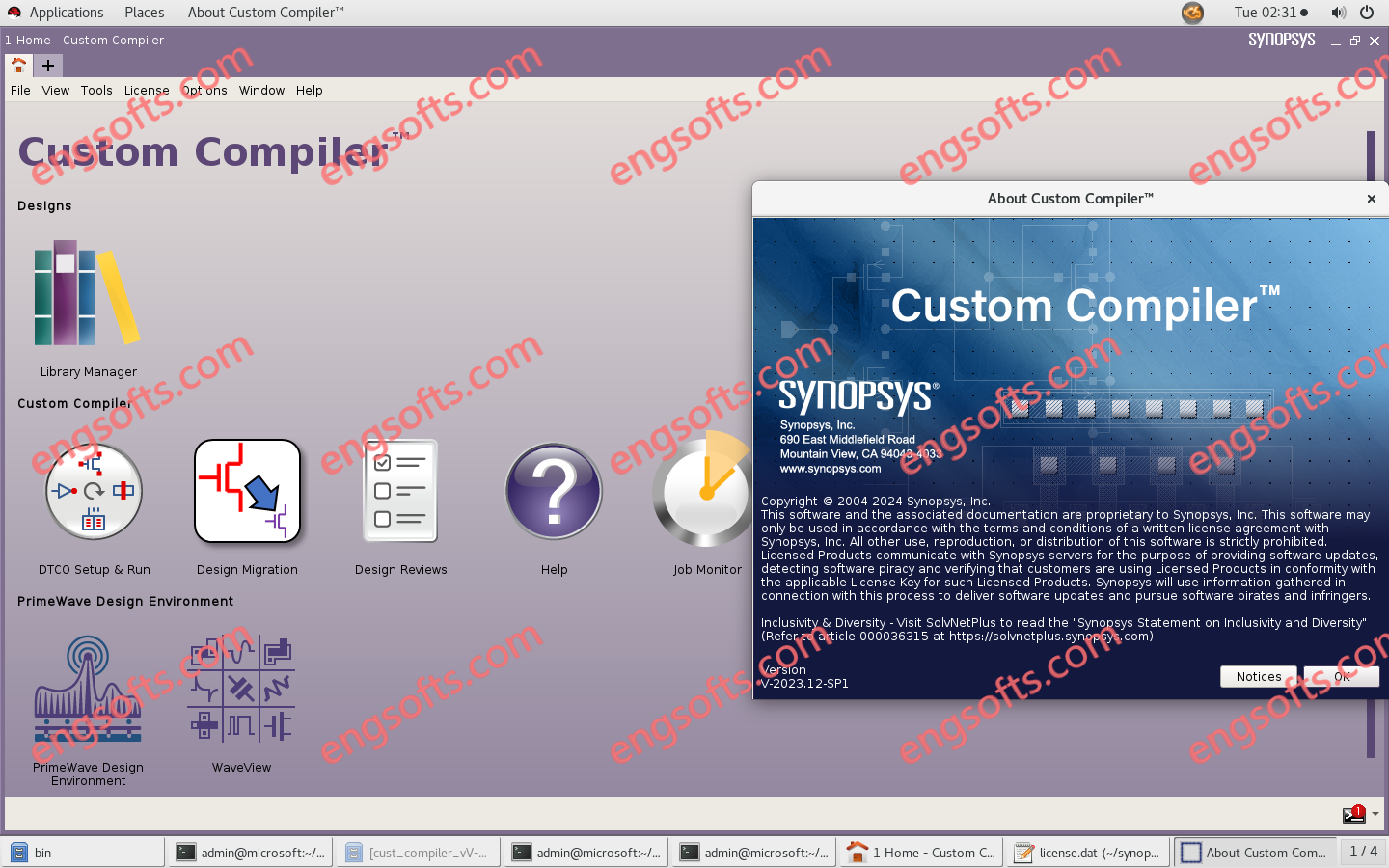

The Synopsys Custom Compiler™ design environment is a modern solution for full-custom analog, custom digital, and mixed-signal IC design. As the heart of the Synopsys Custom Design Family Custom Compiler provides design entry, simulation management and analysis, and custom layout editing features. It delivers industry-leading productivity, performance, and ease-of-use while remaining easy to adopt for users of legacy tools. Synopsys Custom Compiler 2023.12-SP1 Linux64 Tested Picture The Custom Compiler design environment includes features for mixed-signal design entry, design debug, simulation management, analysis, and reporting. For layout, Custom Compiler provides fast and user-friendly polygon editing features and boosts productivity with its pioneering visually-assisted automation flow. Visually assisted automation is an innovative approach that delivers 2-10X better layout productivity—especially for difficult FinFET-based...

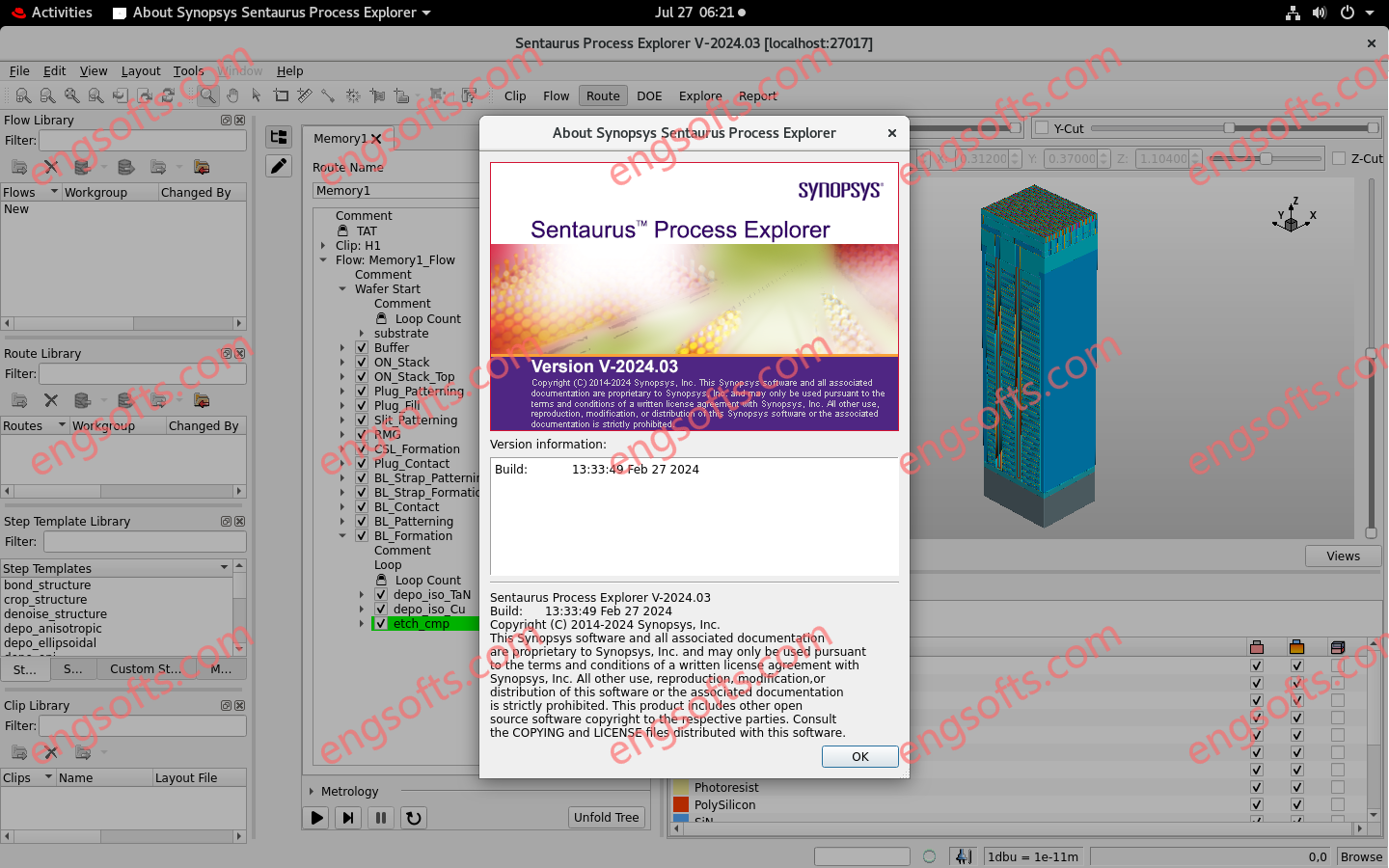

Sentaurus Process Explorer is a fast 3D process emulator used to identify and correct process integration issues during technology development. Synopsys Sentaurus Process Explorer 2024.03 Linux64 Tested Picture Sentaurus Process Explorer produces highly realistic 3D representations of process structures using GDSII mask data and a process recipe as input. Sentaurus Process Explorer is linked to the Synopsys TCAD simulators, such as Raphael FX, to enable the high accuracy RC extraction in Design Technology Co-Optimization (DTCO) applications.

PathWave RFIC Design (GoldenGate) 2024 includes new capabilities which includes new Fast Envelope algorithm, Krylov GPU acceleration, SystemVue VTB updated package, updated support for TMI, new circuit simulation models, improvements in Vrituoso Integration and usability improvements. Go beyond traditional RF simulation to design, analyze, and verify radio frequency integrated circuits (RFICs). Achieve confidence with steady-state and nonlinear solvers for design and verification. Wireless standard libraries accelerate the validation of complex RFICs. accurately model components on silicon chips optimize designs with sweeps and load-pull analysis simulate RF designs in the Cadence Virtuoso and Synopsys Custom Compiler environments increase performance using Monte Carlo and yield analysis assess EVM for the latest communication standards early in the design phase utilize the latest foundry...

CoventorMP 2.1 (MEMS+ 7.101 and CoventorWare 11.101) provides 3D MEMS simulation, analysis, and design automation software for the development of micro- and nano-scale devices and systems. These modules cover the full MEMS design flow for system-level simulation, layout generation, and finite element analysis (FEA) and model generators for IC simulators. The list includes: CoventorWare Designer for MEMS physical design, including process layout and solid modelling CoventorWare Analyzer for preprocessing, field solving and visualizing results MEMS+ Simulator for reduced-order model extraction MEMS+ Innovator for assembling a MEMS device using 3D parametric components MEMS+ Scene3D for looking at MEMS+ Simulator, MATLAB/Simulink, or Cadence’s Virtuoso results in 3D A 2D Layout Editor was introduced in 2018 CoventorMP 2.101 for Red Hat Enterprise Linux Desktop 6 and 7, 64-bit New features...