Solido Design Environment is a comprehensive AI-powered design environment for all SPICE-level design and verification, and is a single unified solution for nominal and variation analysis. Used by thousands of designers to produce the most competitive products in hp computing, AI, IoT, automotive and mobile applications. Brute force-accurate signoff variation 1000X faster Orders of magnitude faster than brute-force simulation Full coverage verification across PVTs and Monte Carlo Brute-force Monte Carlo and SPICE accurate high-sigma verification Variation-aware design sensitivity, debugging and optimization Comprehensive design environment to boost engineering efficiency Significantly reduces documentation time/effort Identifies design weaknesses previously undetectable Easy to use and deploy Intuitive GUI for interactive design and analysis GUI or batch mode Works with all process technologies Integrated with...

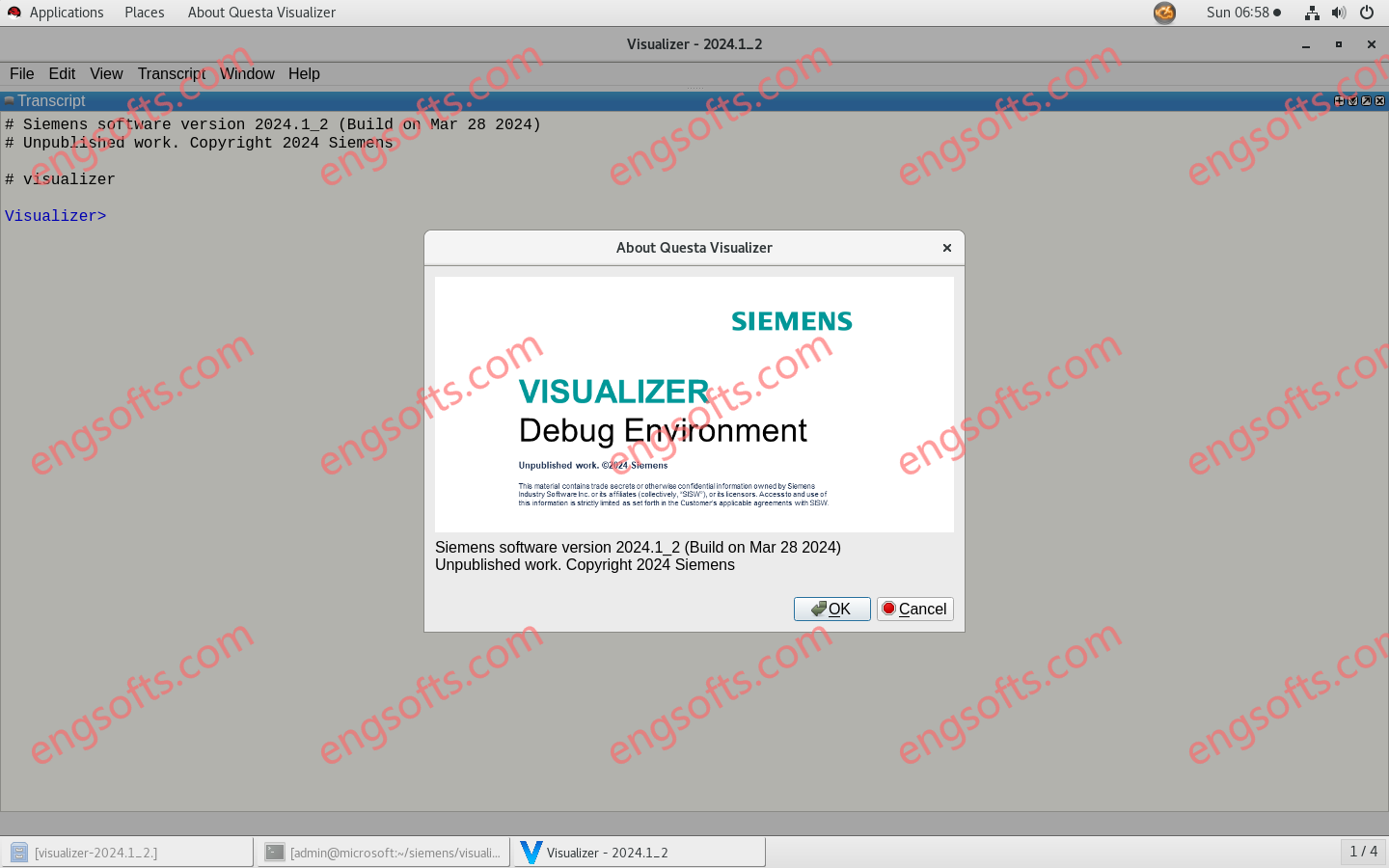

Questa Visualizer Debug Environment is SystemVerilog class-based and UVM-aware to speed up overall debug time, even on today’s most complex SoCs and FPGAs. Siemens Questa Visualizer Debug Environment 2024.1_2 Linux Tested Picture The changing landscape of debug For years the process of ASIC and FPGA design and verification debug consisted primarily of comprehending the structure and source code of the design with waveforms showing activity over time, based on testbench stimulus. Today, functional verification is exponentially complex with the emergence of new layers of design requirements (beyond basic functionality) that did not exist years ago; for example, clocking requirements, security requirements, safety requirements, and requirements associated with hardware-software interactions. Given these complex interactions, effective debug often demands experts that are...

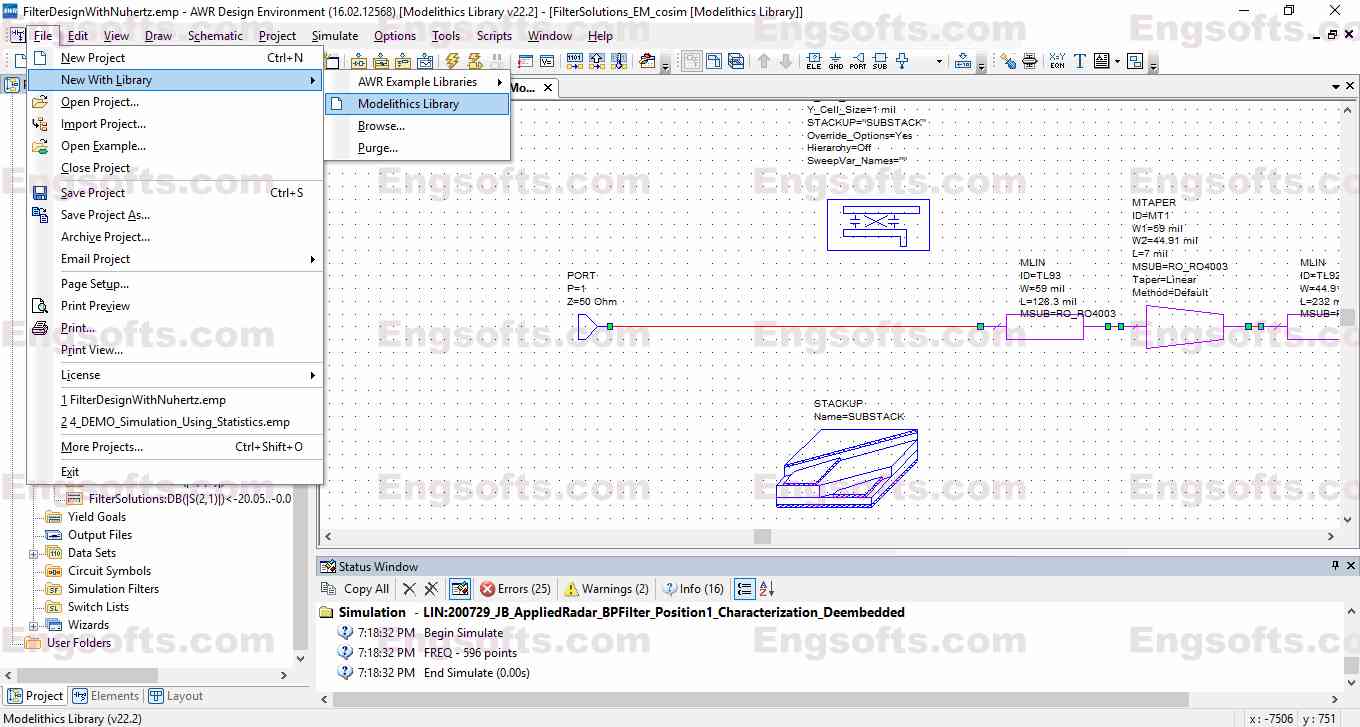

Modelithics announced the release of the latest version, v22.2, of the Modelithics COMPLETE Library for use with the Cadence AWR Design Environment Platform. This version adds nearly 50 new models for various components to the Modelithics COMPLETE Library. With these additions, the Modelithics COMPLETE Library now includes over 825 models that represent over 25,000 passive and active RF/microwave components. This collection of simulation models comprises surface-mount RLC components, diodes, transistors, amplifiers, attenuators, filters, couplers and other system components. Version 22.2 adds new scalable Microwave Global Models™ to the Modelithics COMPLETE Library, including five models for Amotech capacitors, three models for Coilcraft inductors, three models for Kemet capacitors, three models for Kyocera-AVX capacitors, three models for Smiths Interconnect resistors and one for...