Active-HDL is a Windows based, integrated FPGA design creation and simulation solution for team-based environments. Active-HDL’s integrated design environment (IDE) includes a full HDL and graphical design tool suite and RTL/gate-level mixed-language simulator for rapid deployment and verification of FPGA designs. The design flow manager evokes 200+ EDA and FPGA tools, during design entry, simulation, synthesis and implementation flows and allows teams to remain within one common platform during the entire FPGA development process. Active-HDL supports industry leading FPGA devices from AMD, Intel, Lattice, Microchip, Quicklogic and more. Top Features and Benefits Project Management Unified Team-based Design Management maintains uniformity across local or remote teams Configurable FPGA/EDA Flow Manager interfaces with 200+ vendors tools allows teams to remain on one...

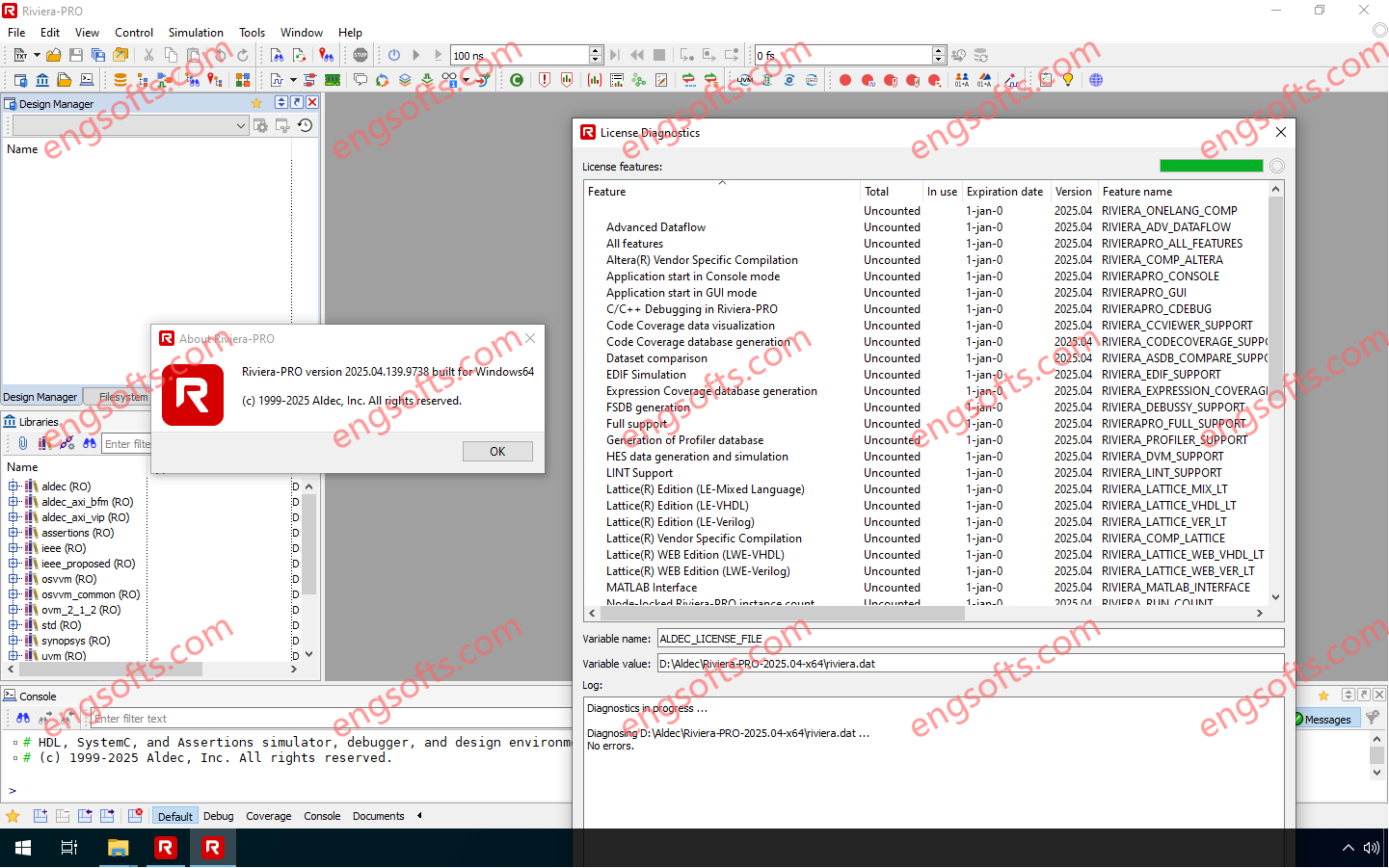

Riviera-PRO addresses verification needs of engineers crafting tomorrow’s cutting-edge FPGA and SoC devices. Riviera-PRO enables the ultimate testbench productivity, reusability, and automation by combining the high-performance simulation engine, advanced debugging capabilities at different levels of abstraction, and support for the latest Language and Verification Library Standards. Available versions: 2025.04 , 2024.04 , … Aldec Riviera-PRO 2025.04 Win/Linux64 Tested Picture Riviera-PRO 2024.04 New Release Key Highlights The SystemVerilog type operator can be used on the list of the actual parameters of classes and design units parameterized with type. The type operator can be used in the type specification of typedef. The modules parameterized with type can be bound to instances with the use of the bind statement. Assigning the value null to SystemVerilog covergroup defined in a class outside of the class constructor is...