Synplify FPGA synthesis software is the industry standard for producing high-performance and cost-effective FPGA designs. Synplify software supports the latest VHDL and Verilog language constructs including SystemVerilog and VHDL-2008/2019. The software also supports FPGA architectures from a variety of FPGA vendors including Achronix, Intel, Lattice, Microsemi and AMD/Xilinx, all from a single RTL and constraint source.

In addition, the Synplify synthesis tool provides high performance, faster runtime, area optimizations for cost and power reduction, incremental and team-design capabilities for faster FPGA design development.

It includes features such as TMR and HAMMING-3 for FSM, that automates the creation of highly reliable designs such as those used in medical, automotive, industrial automation, communications, military, and aerospace applications.

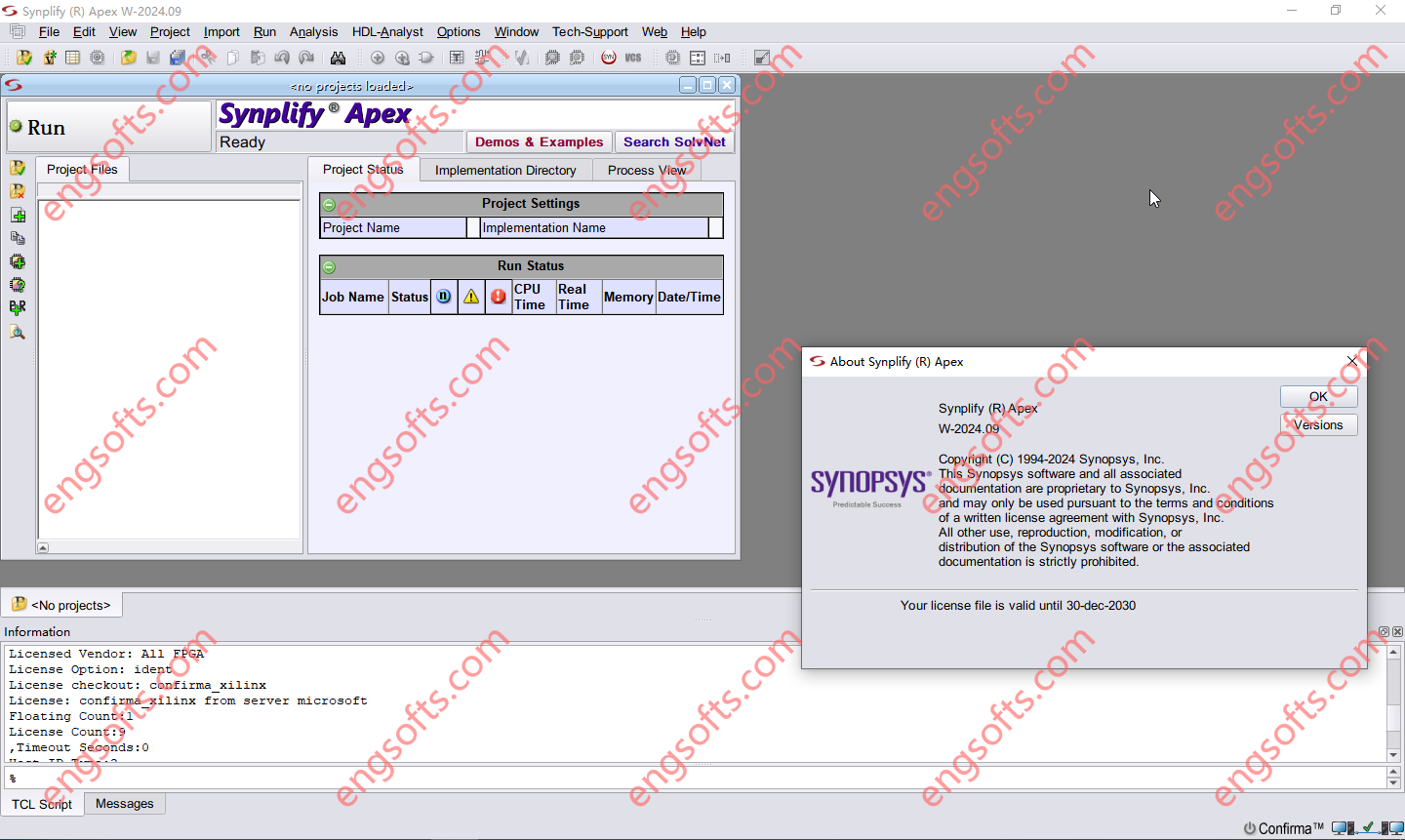

Synopsys Synplify FPGA 2024.09 Win/Linux64 Tested Picture

Synplify Features

- Advanced Verilog, System Verilog and VHDL support

- Best quality of results (QoR) for timing performance and area/cost reduction

- Support for high reliability and safety-critical design including DO-254, ISO 26262 and IEC 61508

- Accelerated runtimes delivering up to 3X runtimes with support for up to 8 processors per license

- Distributed synthesis with support for single or multiple machines

- Static timing analysis and reporting to measure design performance and back-annotate to correlate with post place and route performance.

- Integrated Identify RTL Debugger to quickly find functional errors

- Fault injection and debugging support to measure effectiveness of safety and high reliability features

- HDL Analyst interactive graphical analysis and debug tool for design diagnosis, problem isolation and functional and performance analysis

- Advanced design debug and diagnosis through HDL Analyst and hierarchical debug flows

- FSM Compiler and FSM Explorer for automatic extraction and optimization of finite state machines from RTL

- Integration with VCS® and Verdi

- Scripting and Tcl/Find support for flow automation and customizable synthesis, debug, and reporting