Aprisa is a detail-route-centric physical design solution for the modern SoC. Whether your goal is to speed time to tapeout, reduce total cost of ownership, or achieve the lowest power usage, Aprisa is here with patented technologies and best-in-class support to ensure your success.

Aprisa offers complete functionality for top-level hierarchical design and block-level implementation for complex digital IC designs. Its detail-route-centric architecture and hierarchical database enable fast design closure and optimal quality of results (QoR) at a competitive runtime.

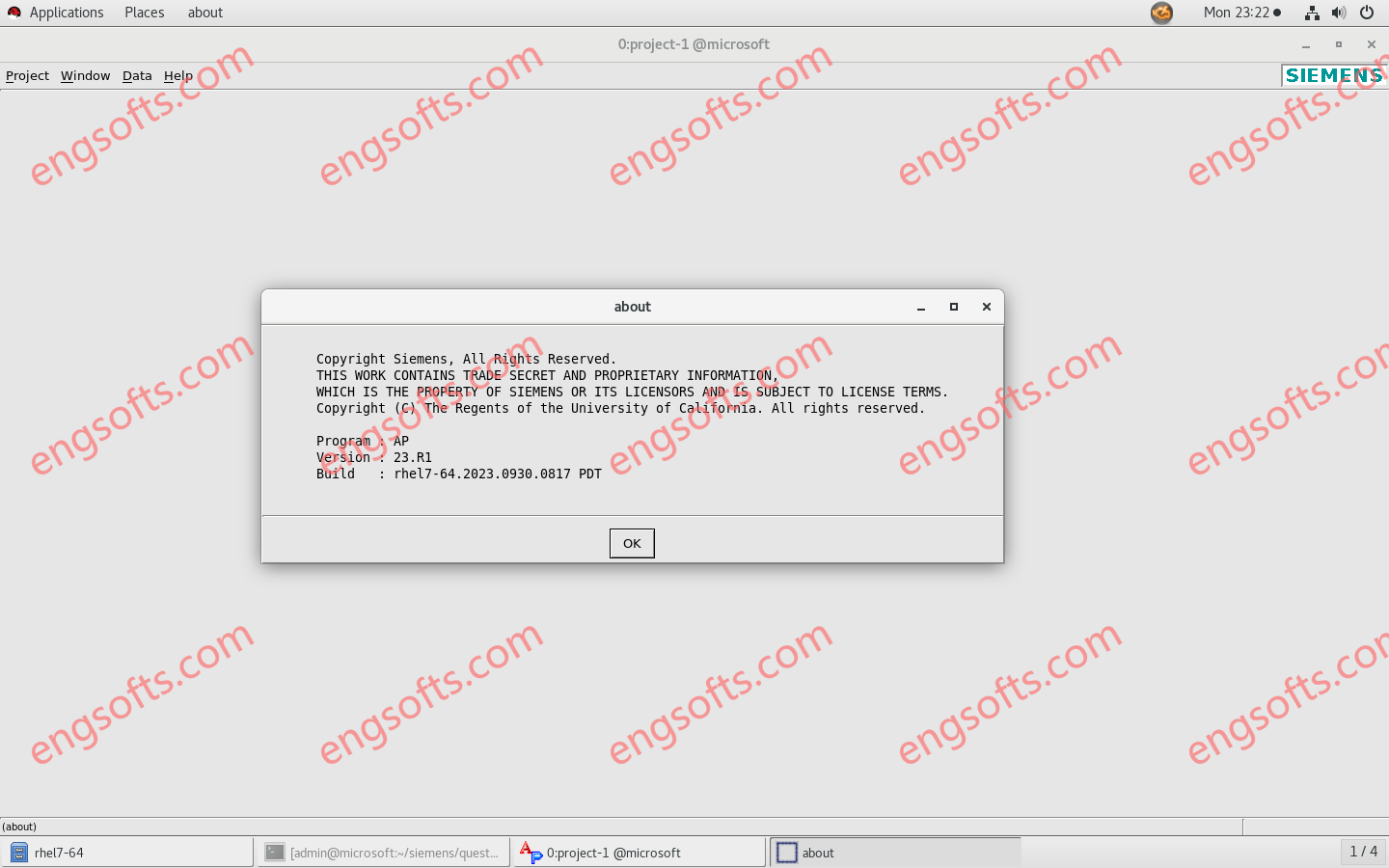

Siemens Aprisa 2023.1 Linux Tested Picture

Reduced time-to-design closure

A unified data model brings real route information and parasitics to any engine and step in the flow. Designers can confidently know their design’s achievable PPA at pre-route stage, greatly reducing full-flow iterations

AI-driven macro placement technology

Expert designer quality macro placement at a fraction of the time and effort that it would take an experienced designer. Eliminates the need for full-flow iterations to lock down the optimal macro placement for a given design

Low power patented technology

Target low power as a primary design metric for power sensitive designs, without sacrificing performance. Designers choose the tradeoffs that meet their optimal PPA, reducing power cleanup on the last mile of the design tapeout

softmed

softmed 956575828

956575828

Must log in before commenting!

Sign Up