Precision offers vendor-independent FPGA synthesis. It provides best-in-class performance and area, high-reliability design capabilities and tight links to simulation and formal equivalency checking. Siemens offers three unique FPGA synthesis solutions – Precision Hi-Rel, Precision RTL Plus and Precision RTL. Precision’s products are tightly integrated with Siemens’ FormalPro LEC for equivalency checking and HDL Designer for design capture and design verification using ModelSim/Questa. Precision RTL Precision RTL, Siemens entry-level FPGA synthesis product, offers best-in-class quality of results with a vendor-independent FPGA synthesis solution. Precision RTL Plus Precision RTL Plus, adds DO-254 certification utilities for mil-aero applications, on-chip debug and validation and resource optimization for DSPs and RAMs. Precision Hi-Rel Precision Hi-Rel, enhances Precision RTL Plus with automated mitigation of SEUs/SETs in...

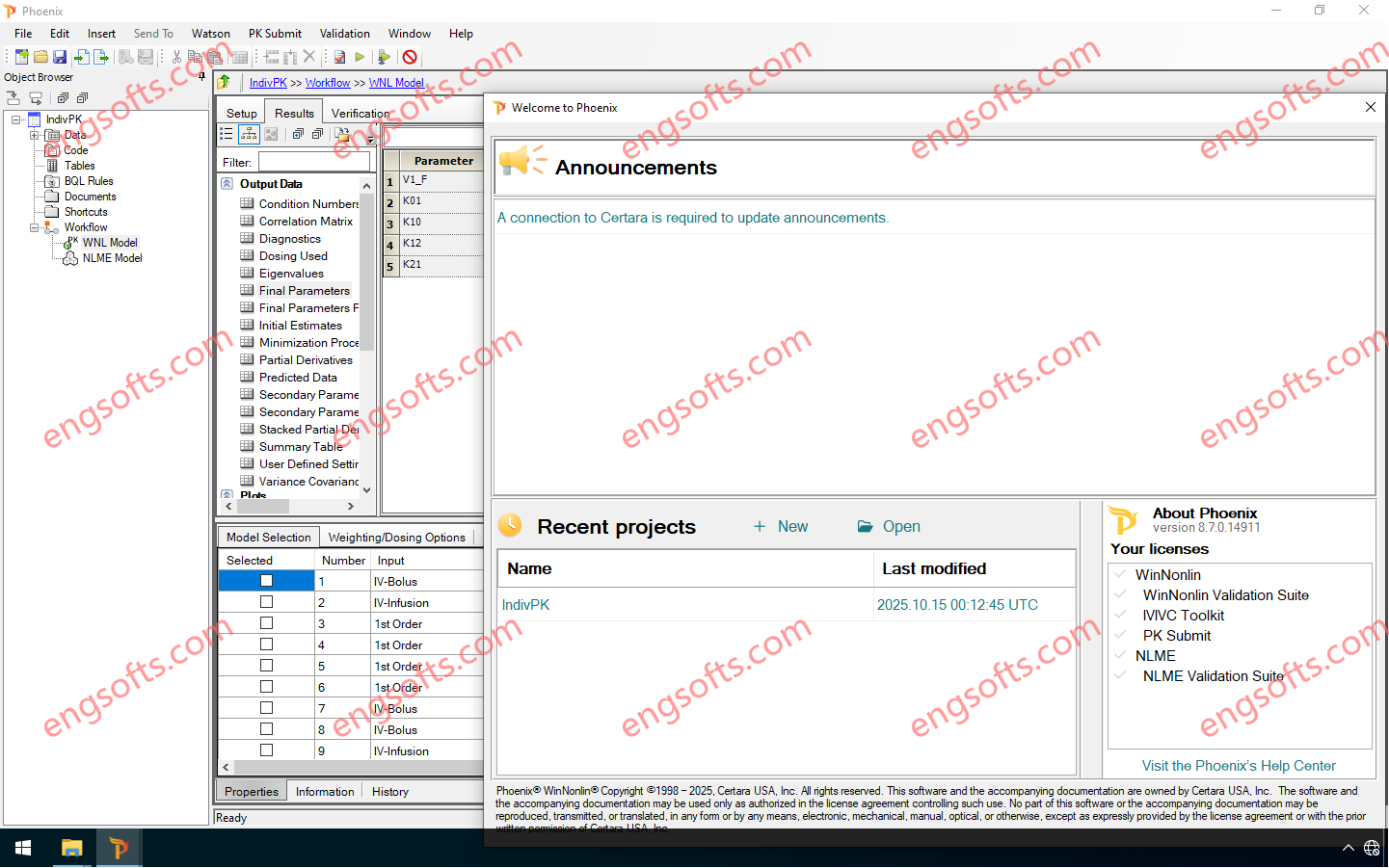

Phoenix delivers comprehensive tools for PK/PD modeling, empowering preclinical scientists and clinical pharmacologists to make critical drug development decisions like these with confidence, even for the most complex modalities. Certara Phoenix 2026 v8.7.0 Tested Picture Accomplish More with Phoenix 8.7 Set and manage default configurations for mappings, data preparation, NCA, PK parameters, and CDISC standards across modules. Map variables to the PK Submit® model, use data converters and unit tools, and apply automated validation rules. Enable or disable modules, apply default expressions, select BLQ rule sets, and visualize profiles and sampling designs. Bulk edit dosing parameters, normalize PK values, calculate totals from diastereomers, categorize analytes, and automate complex calculations. Instantly generate CDISC domains, including SUPPPP and concentration-related domains, directly after...

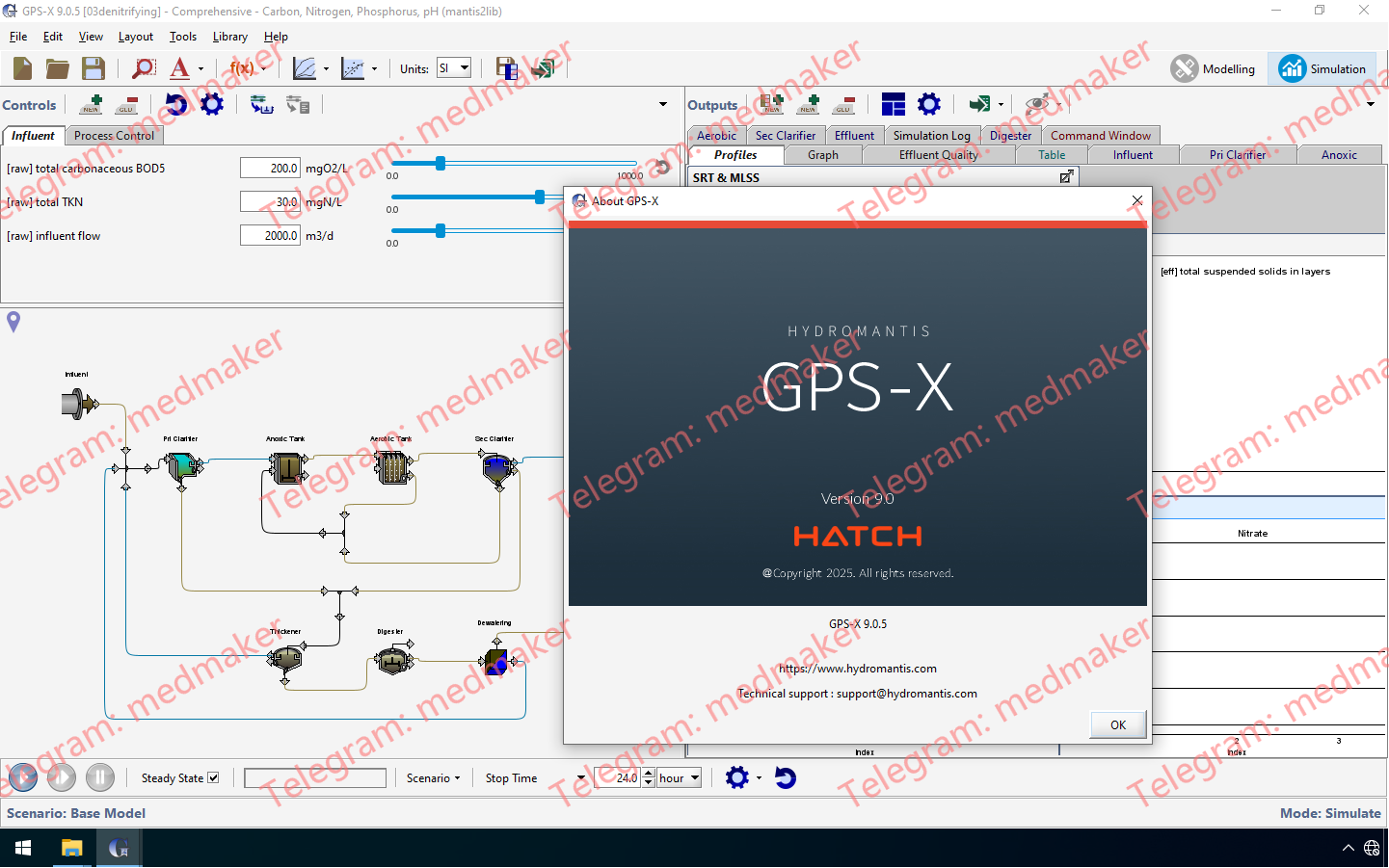

GPS-X 是一款污水建模仿真软件,用于设计新建或升级现有的市政和工业废水处理厂。 可用版本: 9.x , 8.x ,… Hydromantis GPS-X 9.0.5 Tested Picture Hydromantis 最新发布的 GPS-X v9.0 版本包含以下功能: 新增界面功能 新增模型输出基准测试功能,可快速识别超出典型范围的参数 新增数据过滤和异常值记录功能,适用于所有输入时间序列 场景现在可以包含对输入控制器的更改 新增仿真日志,用于跟踪仿真过程和查看警告 新增废水模型功能 新增过程控制器模型 比例控制器 – 创建流量控制控制器 步进控制器 – 为多个操作值设置离散设定点范围(例如 ABAC)。 – 基于氨的曝气控制) 每周调度控制器 – 轻松设置每周工艺运行计划(例如,离心机仅在工作日上午 8 点至下午 4 点运行) 条件控制器 – 根据模型中的其他参数值设置参数值(例如,如果进水量大于某个特定值,则设置旁路流量) 离散事件调度器 – 创建离散参数更改,使其在未来的预定或随机时间发生 所有水箱和水流中氧化还原电位 (ORP) 的估算 澳大利亚水量平衡模型 (AWBM) – 一种复杂的径流模型,可根据降雨量模拟雨水流量 延迟管道模型 – 模拟单元过程间流量延迟的影响 更新的化学药剂投加模型 – 新增按化学药剂体积(例如 L/min、gal/d 等)投加的功能 更新的各种模型校准 – 通过我们应用 GPS-X 的经验,反映废水处理技术的进步 各种错误修复和软件改进 More Information in English:Hydromantis GPS-X 9.0.5

Ansys Totem is the proven, trusted industry leader for power noise and reliability signoff for analog and mixed-signal designs built on cloud-native elastic compute infrastructure. Available versions: 2025.x ,2024.x ,2023.x ,… ANSYS Totem/Totem-SC 2025R2.2 Linux64 Tested Picture Ansys Totem revolutionizes transistor-level power integrity and reliability analysis, empowering users to conduct thorough assessments on analog mixed-signal IP and full-custom designs. It reshapes the conventional flow of analog mixed-signal power noise and reliability analysis by accommodating various design environments for modeling and characterization. Totem boasts a robust extraction and simulation engine, complemented by an intuitive graphical interface for in-depth root cause analysis and debugging of results. Power Integrity and Noise Verification at Transistor Level Totem-SC offer an ultra high-capacity version of Totem...

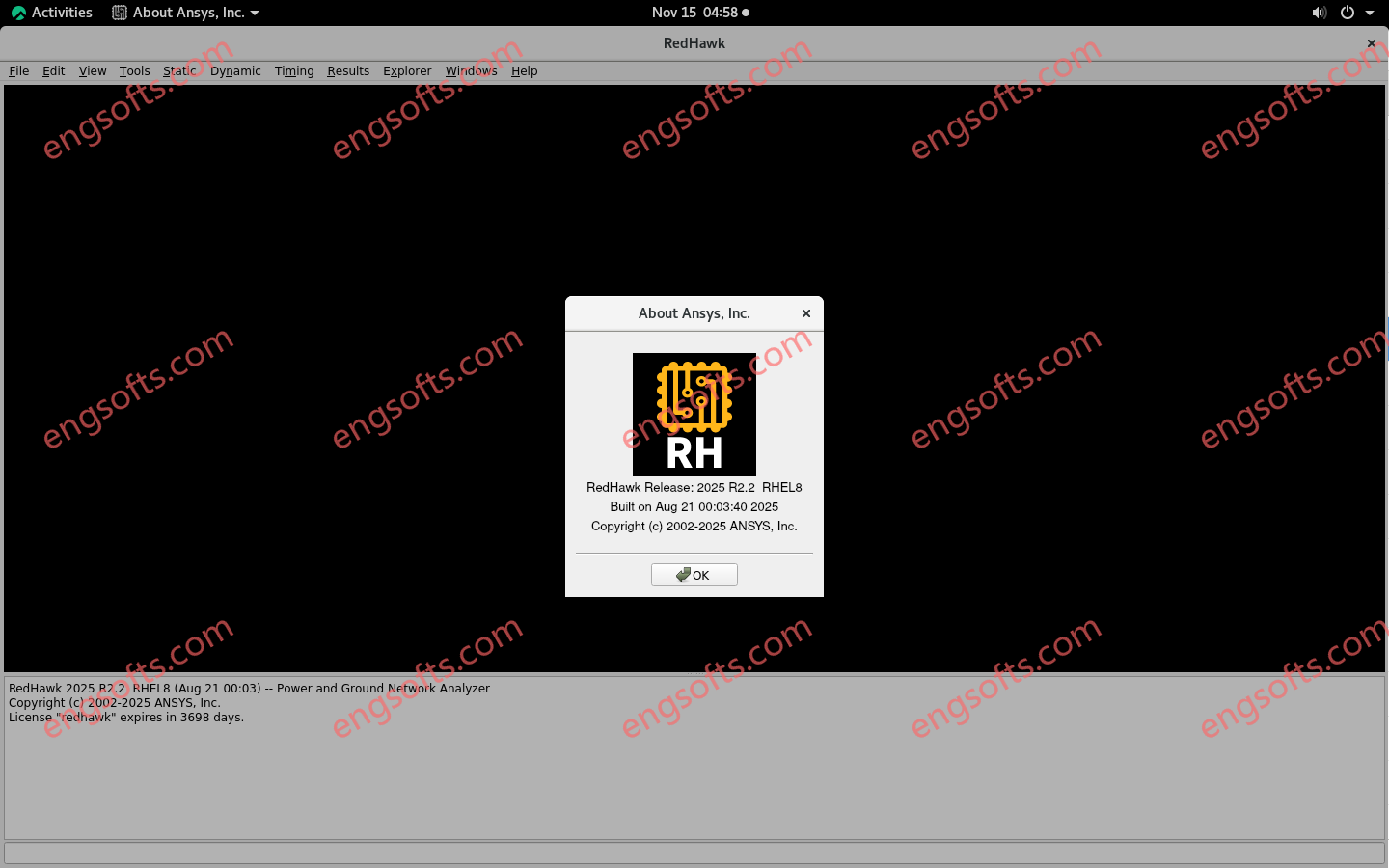

RedHawk-SC is the proven, trusted industry leader for power noise and reliability signoff for digital IP and SoCs down to 3nm and built on cloud-native elastic compute infrastructure Available versions: 2025.x ,2024.x ,2023.x ,… ANSYS Redhawk 2025R2.2 Linux64 Tested Picture RedHawk-SC is the premier solution for power noise and reliability signoff, renowned for its reliability in digital IP and SoCs scaling down to 3nm. It boasts a cloud-native elastic compute infrastructure, ensuring scalability and flexibility to meet the evolving demands of semiconductor design. As the trusted industry leader, RedHawk-SC provides comprehensive support for power integrity verification, enabling designers to achieve optimal performance and reliability in their designs while leveraging cutting-edge technology and cloud resources. IR-drop signoff Thermal-aware EM analysis Timing...

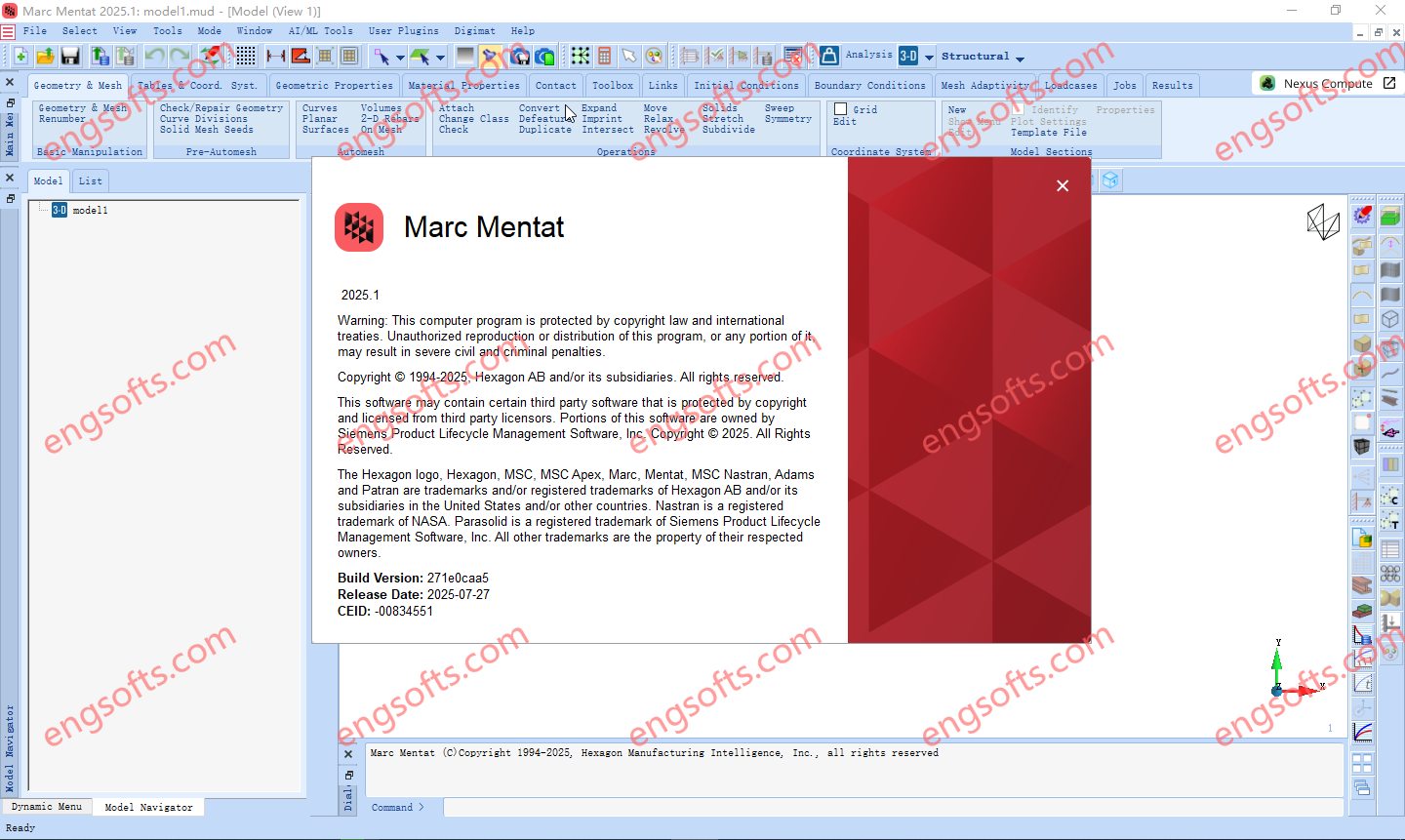

Marc 2025.2 版本在预处理过程中全面支持单位,新增了温度相关的超单元、新的非线性高级摩擦模型、增强了从先前分析中定义模拟初始条件的功能、改进了橡胶或弹性体力学行为的温度依赖性建模,并提高了混合接触算法的鲁棒性。Marc 2025.2 的亮点包括单位感知后处理、改进的 RBE2 和 RBE3 控制等。支持512 核心及以上。 可用版本: 2025.x , 2024.x , … MSC Marc and Mentat 2025.1 Tested Picture 2025.2版本亮点包括: 准确解读结果: 无论您查看的是模型图、历史图还是路径图,Mentat 在后处理过程中都能始终如一地显示单位。 更好地控制 RBE: 轻松显示或隐藏、快速识别和选择 RBE2 和 RBE3 单元。它们在后处理过程中也可见。 使用用户材料子程序实现更多功能: UMATERIAL 子程序现在支持壳、梁、各向异性和表格。 以最小的改动或无需改动即可重用 Abaqus UMAT 子程序,从而简化工作流程。 利用增强的接触建模功能: 混合节点到线段接触方法现在支持用户自定义分离行为,并且与载荷控制刚体粘合接触的结果更加精确。 More Information in English: MSC Marc and Mentat 2025.2

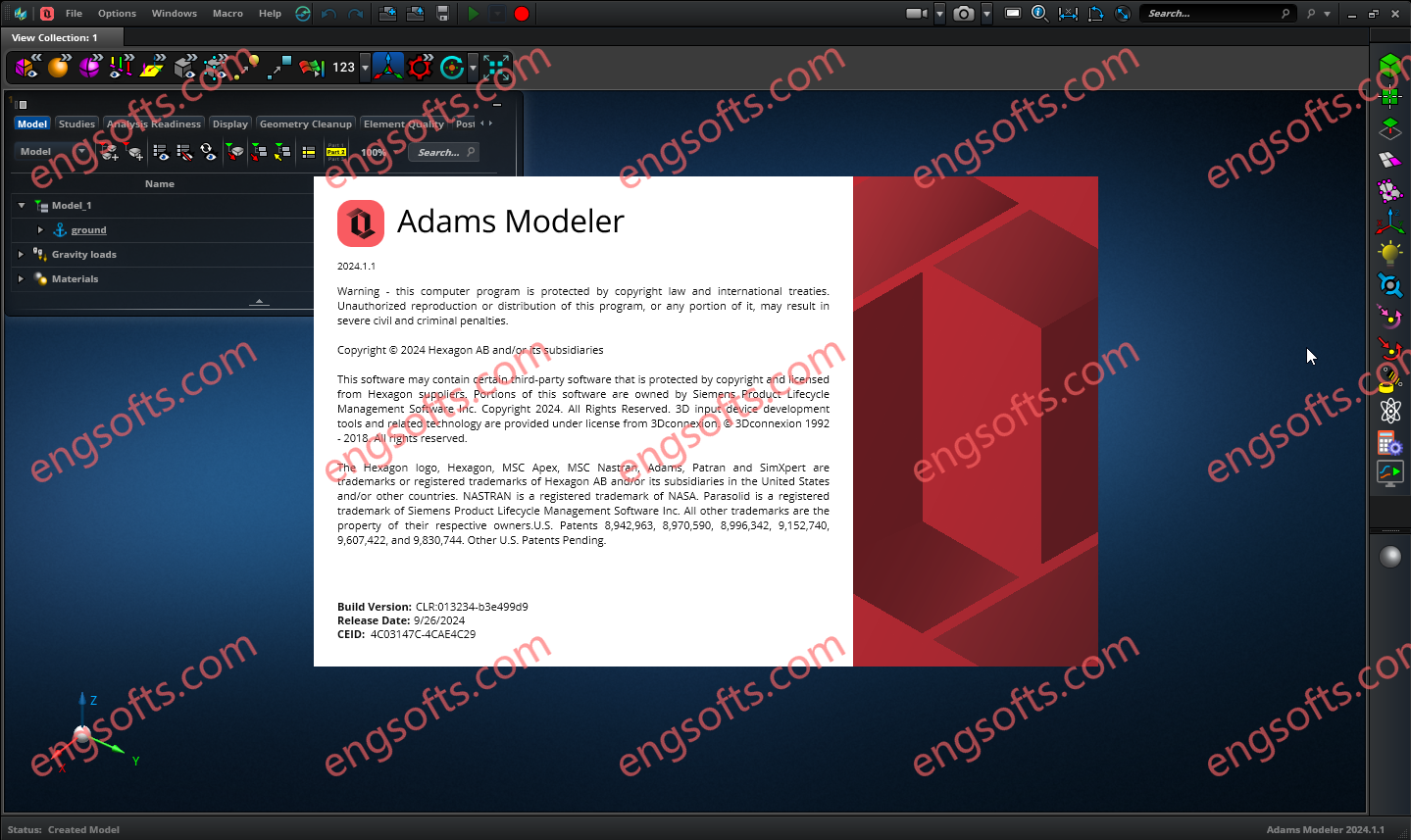

Adams Modeler 配备了强大的新一代前处理器和后处理器,使您能够以令人难以置信的逼真细节和物理效果渲染模型。支持512 核心及以上。 可用版本: 2025.x , 2024.x , … MSC Adams Modeler 2024.1 Tested Picture Adams Modeler 2025.1 版本包含以下功能: 支持非线性梁 (XBEAM) 利用 Apex 平台增强的定义和修改功能,支持底层 Adams FEPart 对象。 支持几何参考的宏记录 记录涉及几何体选择的用户操作时,这些操作现在会永久保存在宏中。 支持关节摩擦 用户现在可以指定关节摩擦特性,每个关节可以使用通用或单独的摩擦属性。 More Information in English: MSC Adams Modeler 2025.1

MSC CoSim 兼具稳定性和易用性,应用广泛,涵盖多个行业,可帮助您解决复杂的多物理场问题。CoSim 2025.1 改进了与 Adams 和 Marc、Marc/MSC Nastran 以及 scFLOW 的耦合分析功能。此外,图形界面中还新增了命令规范选项。支持512 核心及以上。 可用版本: 2025.x , 2024.x , 2023.x , 2022.x ,… MSC CoSim 2025.1 新增功能 Adams 增强功能 – Marc 耦合 MSC CoSim 2025.1 现在支持 Marc 估计的时间增量。最初,CoSim 引擎会将内部计算的新时间增量 (dt_new) 发送给 Marc 和 Adams。然而,Marc 还会计算一个单独的估计值 dt_est,该值可能小于 dt_new。在 MSC CoSim 2025.1 中,CoSim 引擎现在会同时考虑这两个值,并在仿真中使用较小的时间增量。 这一新标准有望提升性能和收敛性。由于使用了更合适的时间增量,可以减少缩减次数。这对于以前需要大量缩减的高度非线性作业尤其有利。 Marc-scFLOW 增强功能 & MSC Nastran-scFLOW 耦合 CoSim 条件向导中新增了一个参数,用于控制 CoSim 迭代循环的最小次数。现在可以在 Marc-scFLOW 的迭代 CoSim 模式和 Nastran-scFLOW 的静态 CoSim 模式下设置最小迭代次数。 此增强功能通过防止循环过早终止来提高精度和稳定性。对于难以定义收敛阈值的复杂系统,设置更加简便,尤其适用于非线性系统或难以收敛的问题。此外,它还提供了一种在流固耦合仿真中实现更高精度的简便方法。 其他增强功能 Marc-scFLOW 耦合中的热耦合仿真现在也支持通过 scFLOW 命令(COSIM 命令)的新规范来实现。 备注: CoSimPRE 的配置步骤与使用传统 scFLOW 命令(COSIM_STRUCTURE 命令)时相同。 要在 scFLOW 中使用此功能,需要在 Cradle CFD 2025.1 中使用 scFLOW pre/solver。 在 scFLOWpre 的 [环境设置] 对话框中,选择 [新规范] 作为 [使用 MSC CoSim 进行协同仿真的命令规范],即可使用 scFLOW 的新命令规范。 某些功能,例如 6 自由度分离和重启,仅在使用新规范的 scFLOW 命令时可用。未来将使用新的命令规范添加与 scFLOW 耦合相关的新功能。 More Information in English: MSC CoSim 2025.1

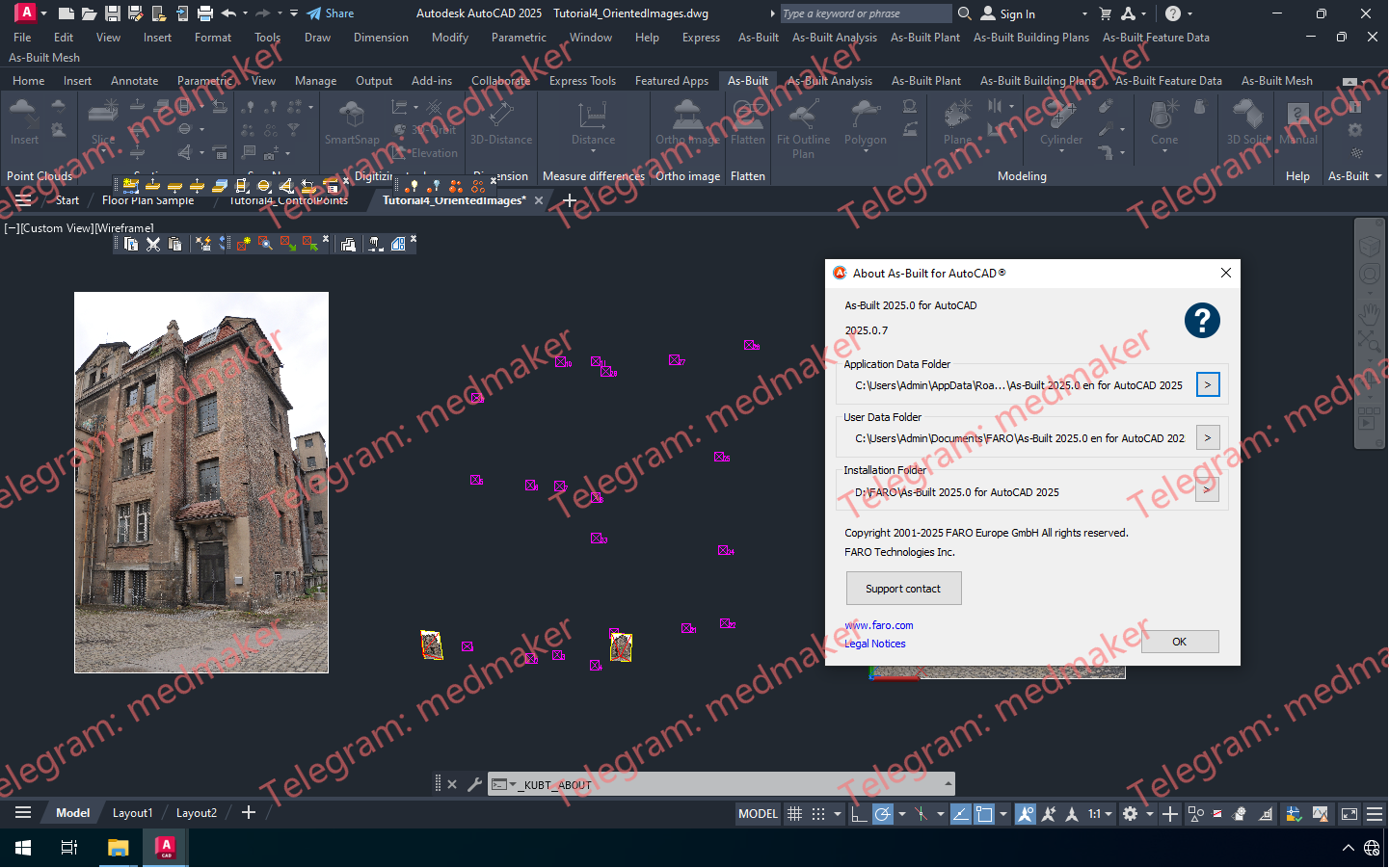

FARO As-Built for AutoCAD 是所有 PointSense for AutoCAD 产品的后续产品。它包含 PointSense Pro、Building、Heritage 和 Plant 的所有功能,并新增了其他功能。As-Built for AutoCAD 支持多种语言。 可用版本: 2025.x , … 预先安装: 所有 AutoCAD 2023-2026及其相关的Civil 3D, Architecture, Plant 3D FARO As-Built 2025.0.7 for AutoCAD 2025 Tested Picture As-Built for AutoCAD 提供强大的工具,可从点云中生成平面图、图像平面图和 3D 模型,用于建筑、施工和工程领域的竣工数据采集和规划。设备组件和管道系统及其所有参数均可被自动检测和记录。无需建模即可确定精确的连接点。分析工具可用于对建模对象进行质量控制,以及确定和可视化变形。集成的特征数据采集功能可用于设施管理和房地产管理,也可用于生成管道系统组件清单或绘制历史建筑立面的损坏图。摄影测量工具是历史建筑清单和文档记录的重要补充,尤其适用于历史建筑保护和建筑研究。 More Information in English: FARO As-Built 2025.0.7 for AutoCAD 2023-2026

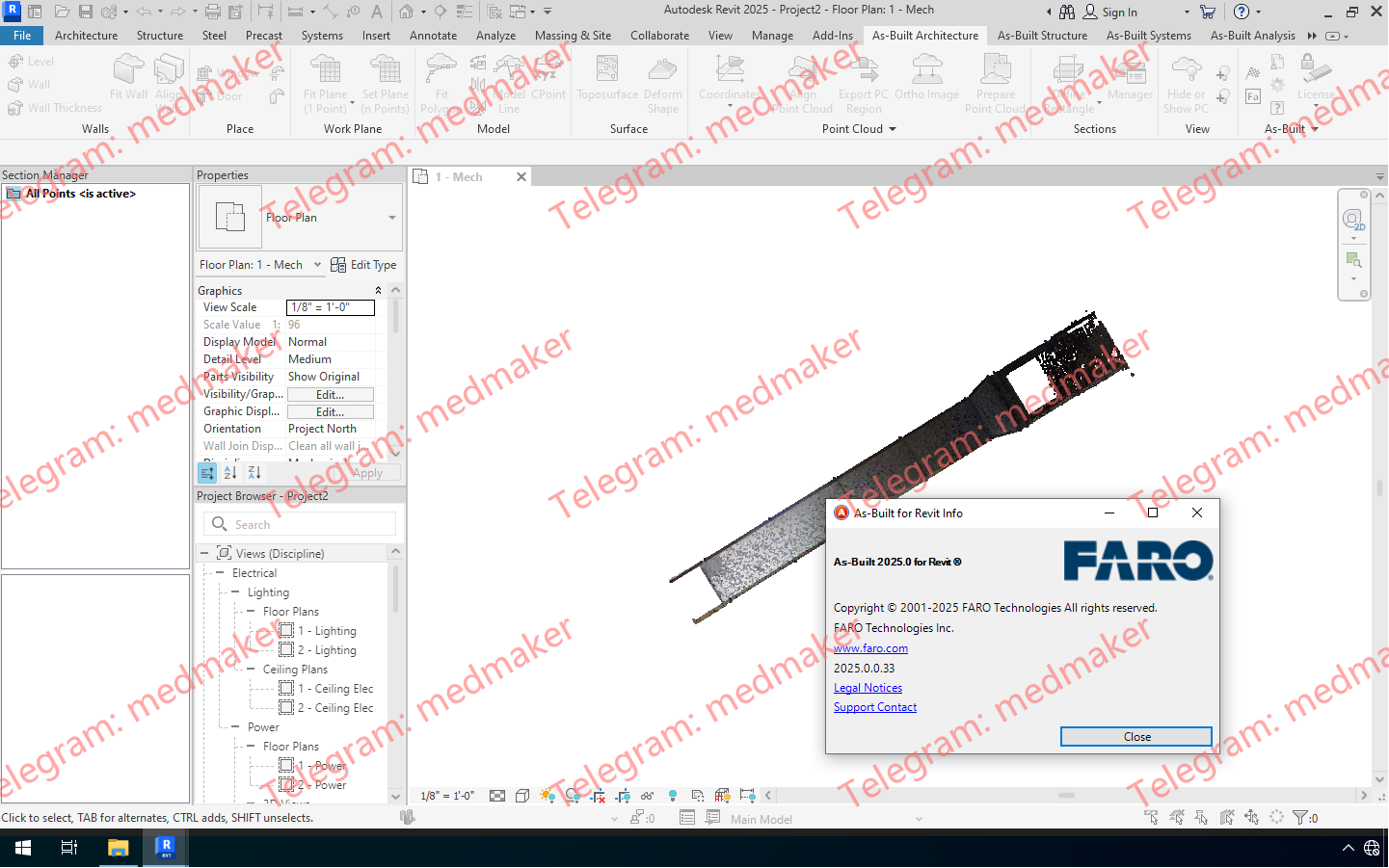

As-Built for Autodesk Revit 提供快速直观的工作流程,可将 3D 激光扫描数据直接导入 Autodesk Revit,并使用 Revit 对象和 BIM 模型进行处理。 可用版本: 2025.x , … 预先安装: 所有 Revit 2023-2026 (Architecture、Structure、MEP和来自 Architecture, Engineering & Construction Industry Collection的Revit完整版) FARO As-Built 2025.0 for Revit 2025 Tested Picture As-Built for Revit是处理大型点云的 Revit 用户的理想之选,并可与熟悉的 Revit 用户界面无缝集成。它包含一系列用于评估 3D 激光扫描数据的工具,以及用于建模和细化 BIM 元素的自定义命令。 More Information in English: FARO As-Built 2025.0 for Revit 2023-2026