EDA 第3页

Electrical & Power Engineering softwares.

Ansys Totem is the proven, trusted industry leader for power noise and reliability signoff for analog and mixed-signal designs built on cloud-native elastic compute infrastructure. Available versions: 2025.x ,2024.x ,2023.x ,… ANSYS Totem/Totem-SC 2025R2.2 Linux64 Tested Picture Ansys Totem revolutionizes transistor-level power integrity and reliability analysis, empowering users to conduct thorough assessments on analog mixed-signal IP and full-custom designs. It reshapes the conventional flow of analog mixed-signal power noise and reliability analysis by accommodating various design environments for modeling and characterization. Totem boasts a robust extraction and simulation engine, complemented by an intuitive graphical interface for in-depth root cause analysis and debugging of results. Power Integrity and Noise Verification at Transistor Level Totem-SC offer an ultra high-capacity version of Totem...

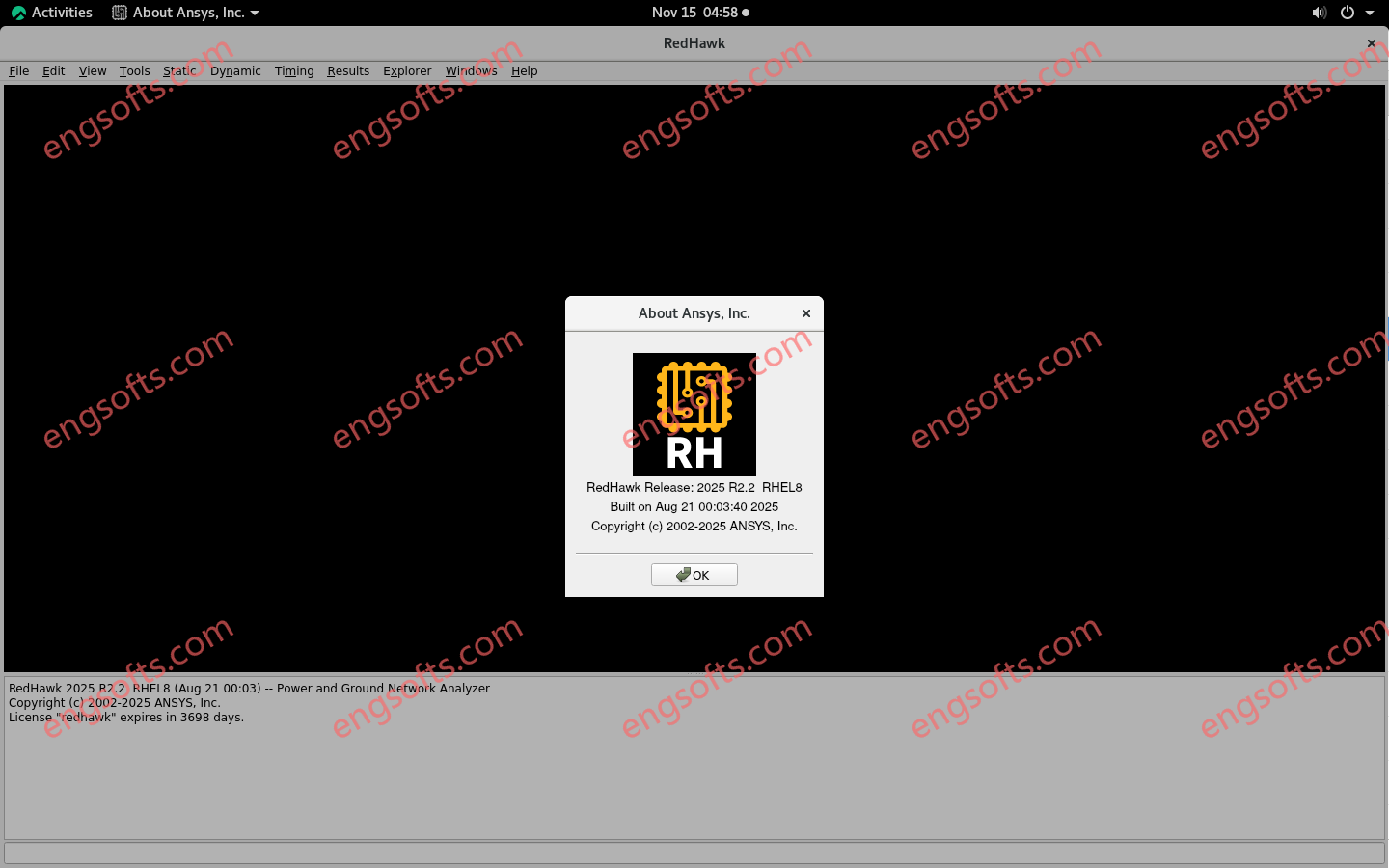

RedHawk-SC is the proven, trusted industry leader for power noise and reliability signoff for digital IP and SoCs down to 3nm and built on cloud-native elastic compute infrastructure Available versions: 2025.x ,2024.x ,2023.x ,… ANSYS Redhawk 2025R2.2 Linux64 Tested Picture RedHawk-SC is the premier solution for power noise and reliability signoff, renowned for its reliability in digital IP and SoCs scaling down to 3nm. It boasts a cloud-native elastic compute infrastructure, ensuring scalability and flexibility to meet the evolving demands of semiconductor design. As the trusted industry leader, RedHawk-SC provides comprehensive support for power integrity verification, enabling designers to achieve optimal performance and reliability in their designs while leveraging cutting-edge technology and cloud resources. IR-drop signoff Thermal-aware EM analysis Timing...

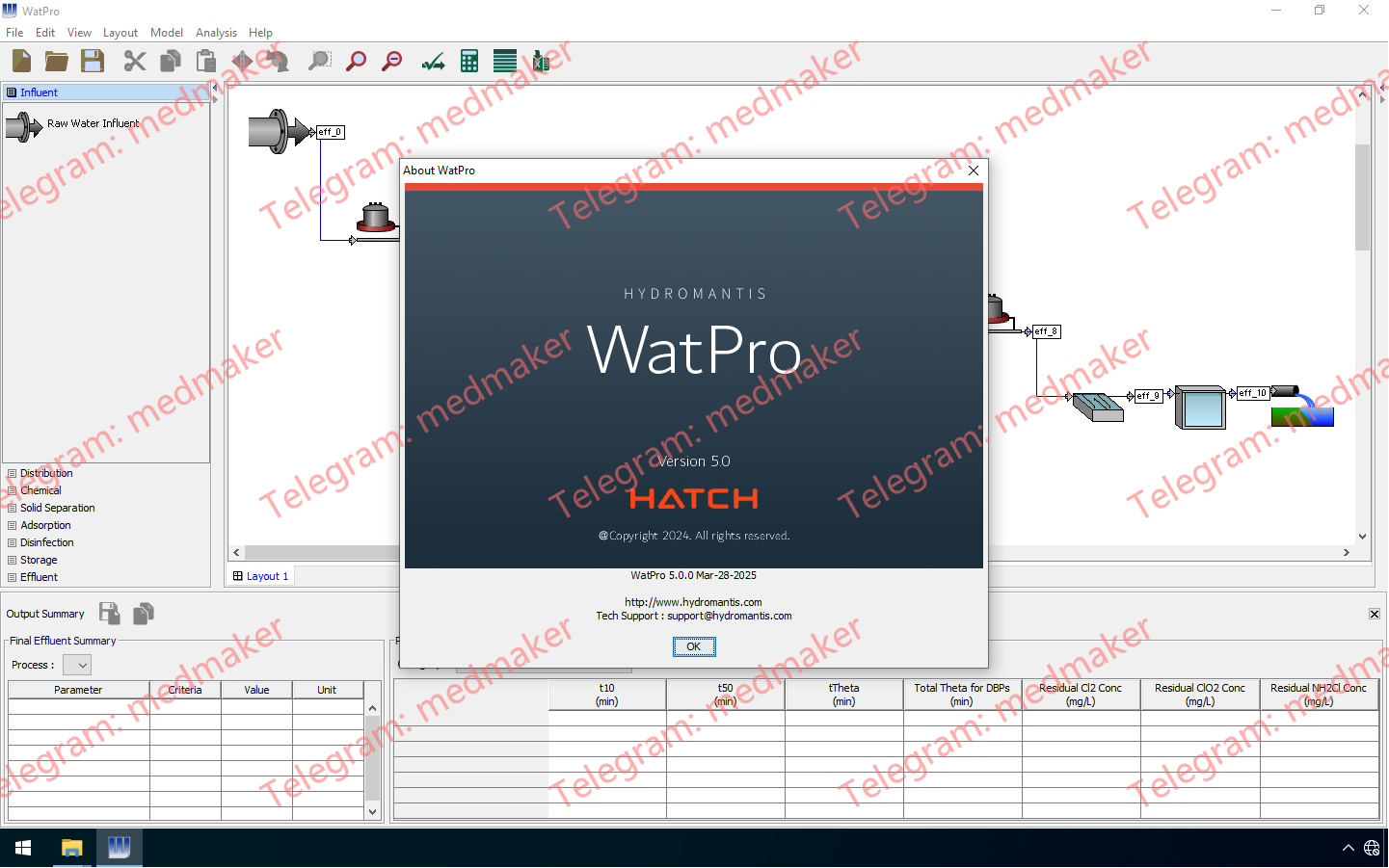

WatPro 是一款精密的工具,可以从微生物和化学的角度对饮用水处理设施的性能进行简单的评估。 可用版本: 5.x ,… Hydromantis WatPro 2025 v5.0 Tested Picture 该软件可以对消毒副产物 (DBP) 的形成、贾第鞭毛虫和病毒的灭活、有机物的去除、消毒剂的衰减以及 pH 值进行稳态分析。 More Information in English:Hydromantis WatPro 2025 v5.0

Device Modeling MBP 是一款一站式解决方案,可为大批量模型生成提供自动化和灵活性。该软件包含用于行业标准模型的自动化提取包,以及用于建模策略定制的开放接口。此外,它还提供用于高级统计和失配模型提取、布局邻近效应 (LPE) 建模、静态随机存取存储器 (SRAM) 单元建模、HVMOS 建模、可扩展电感器建模和角库生成的交钥匙解决方案。 可用版本: 2026.x , 2025.x ,… Keysight Model Builder Program (MBP) 2026.0 Tested Picture Device Modeling MBP 2026 是一个完整的建模解决方案,集成了 SPICE 仿真、模型参数提取和模型库生成。 新的机器学习工具包支持机器学习优化器,提供示例自动提取流程,并提供 Python API 和相关实用程序。MBP 2026 还增强了模型库支持,新增了 Python API 和 MBP 脚本函数,改进了 MBP 图形用户界面,支持 BSIM-CMG112.0,并进行了其他方面的增强。. 它使您能够: 利用内置 SPICE 引擎提高建模效率 构建自动化提取包 通过用户友好的图形用户界面轻松调整模型参数 使用整个模型库进行微调 提供全面的建模解决方案 使用脚本环境进行自定义 More Information in English: Keysight Model Builder Program (MBP) 2026.0

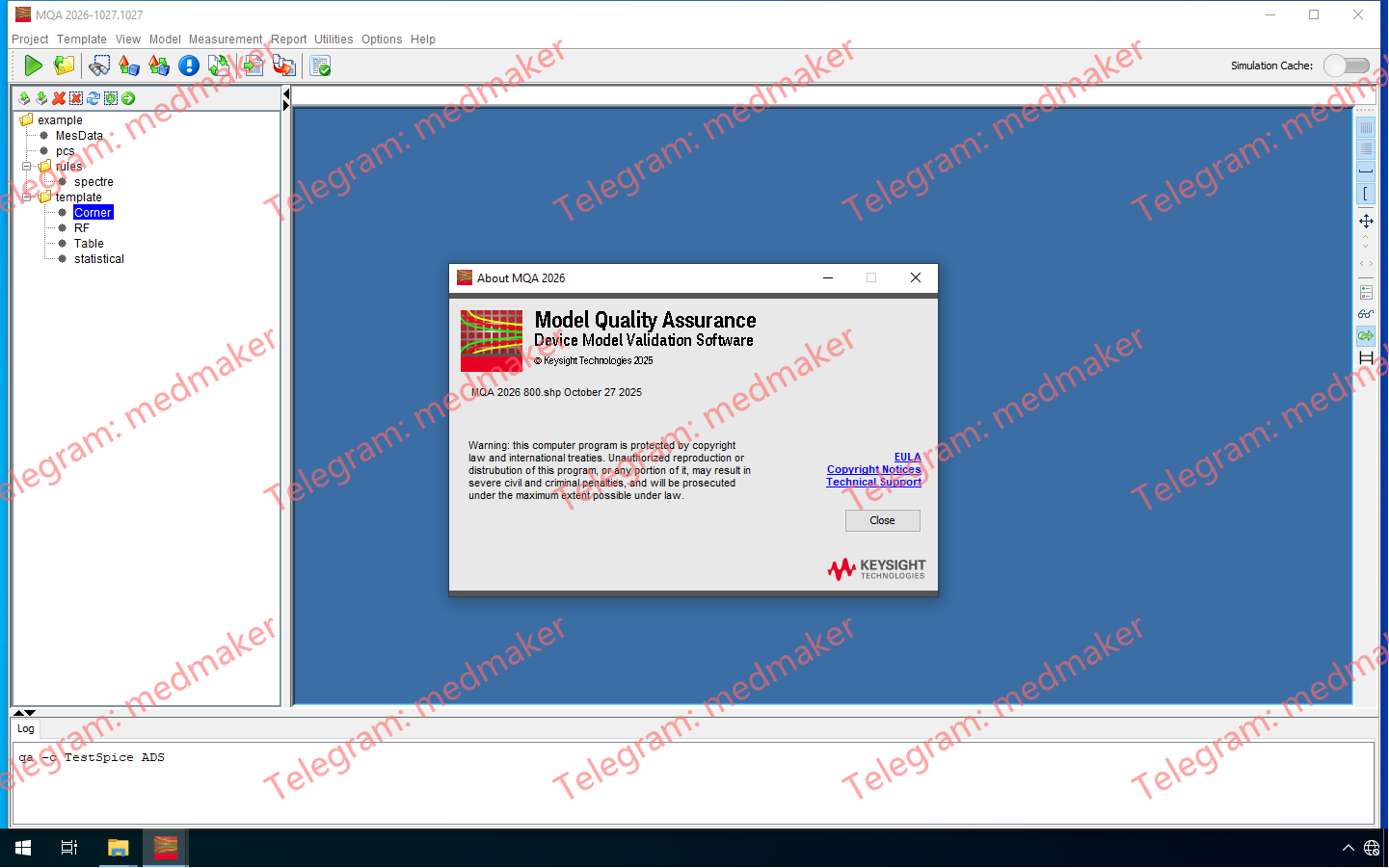

Device Modeling MQA 2026 是 MQA 的下一个主要版本,MQA 是业界标准的自动化 SPICE 模型验证软件。 Device Modeling MQA 支持新的老化模型质量保证 (Aging Model QA) 规则,包括对 OMI 模型质量保证 (OMI Model QA) 的支持以及新的 MOSRA 分析规则。MQA2026 还升级了 BSIM-CMG 默认规则,并增强了 MQA 图表数据表,以突出显示错误。 可用版本: 2026.x , 2025.x ,… Keysight Modeling MQA 2026 Tested Picture MQA 2026 支持新的老化模型质量保证规则,包括 OMI 模型质量保证和 MOSRA 分析的新规则。它还升级了 BSIM-CMG 默认规则,增强了 MQA 图表数据表以突出显示错误,并进行了其他改进。 自动化质量保证流程 轻松识别模型问题 标准化模型验证流程 自定义基于知识的检查程序 自由比较不同模型/代工厂/技术 一键生成质量保证报告 More Information in English: Keysight Modeling MQA 2026

EasyPower 2025, with major new features including support for NFPA 70E 2024, Harmonics updates for IEEE 1547 and 2800, the ability to change names directly on the one-line, and a powerful new licensing service. Other new features include improvements to data entry in the database browser, auto-calculated library information for more equipment, the ability to store and view arc flash calculations in the Database Browser, and support for Revit® 2025. Available versions: 25.00.x,24.00.x ,… EasyPower Advanced 2025 Tested Picture EasyPower 2025 Update This topic describes new EasyPower features and enhancements, security improvements, and bug fixes that are included in the release. Features and Enhancements Store Short Circuit and Arc Flash Analysis Results in the Database Store Short Circuit and Arc Flash Results...

PathWave Vector Signal Analysis (89600 VSA) is a comprehensive set of tools for demodulation and vector signal analysis. Discover signal analysis software tools to explore every facet of a signal and optimize your designs. Measure a broad range of signals including 5G, IoT, radar and more. Gain greater insight in frequency, time and modulation domains. Compatible with signal analyzers, network analyzers, oscilloscopes and many more test instruments. Available versions: 2026 v30.x , 2025 v29.x ,… Keysight PathWave Vector Signal Analysis (89600 VSA) 2026 v30.00 Tested Picture Pinpoint Signal Problems Reach deeper into signals to find the root cause of problems in time, frequency, and modulation domains. Record and playback signals for troubleshooting. Isolate unexpected interactions with unlimited markers and trace-to-trace...

Active-HDL is a Windows based, integrated FPGA design creation and simulation solution for team-based environments. Active-HDL’s integrated design environment (IDE) includes a full HDL and graphical design tool suite and RTL/gate-level mixed-language simulator for rapid deployment and verification of FPGA designs. The design flow manager evokes 200+ EDA and FPGA tools, during design entry, simulation, synthesis and implementation flows and allows teams to remain within one common platform during the entire FPGA development process. Active-HDL supports industry leading FPGA devices from AMD, Intel, Lattice, Microchip, Quicklogic and more. Top Features and Benefits Project Management Unified Team-based Design Management maintains uniformity across local or remote teams Configurable FPGA/EDA Flow Manager interfaces with 200+ vendors tools allows teams to remain on one...

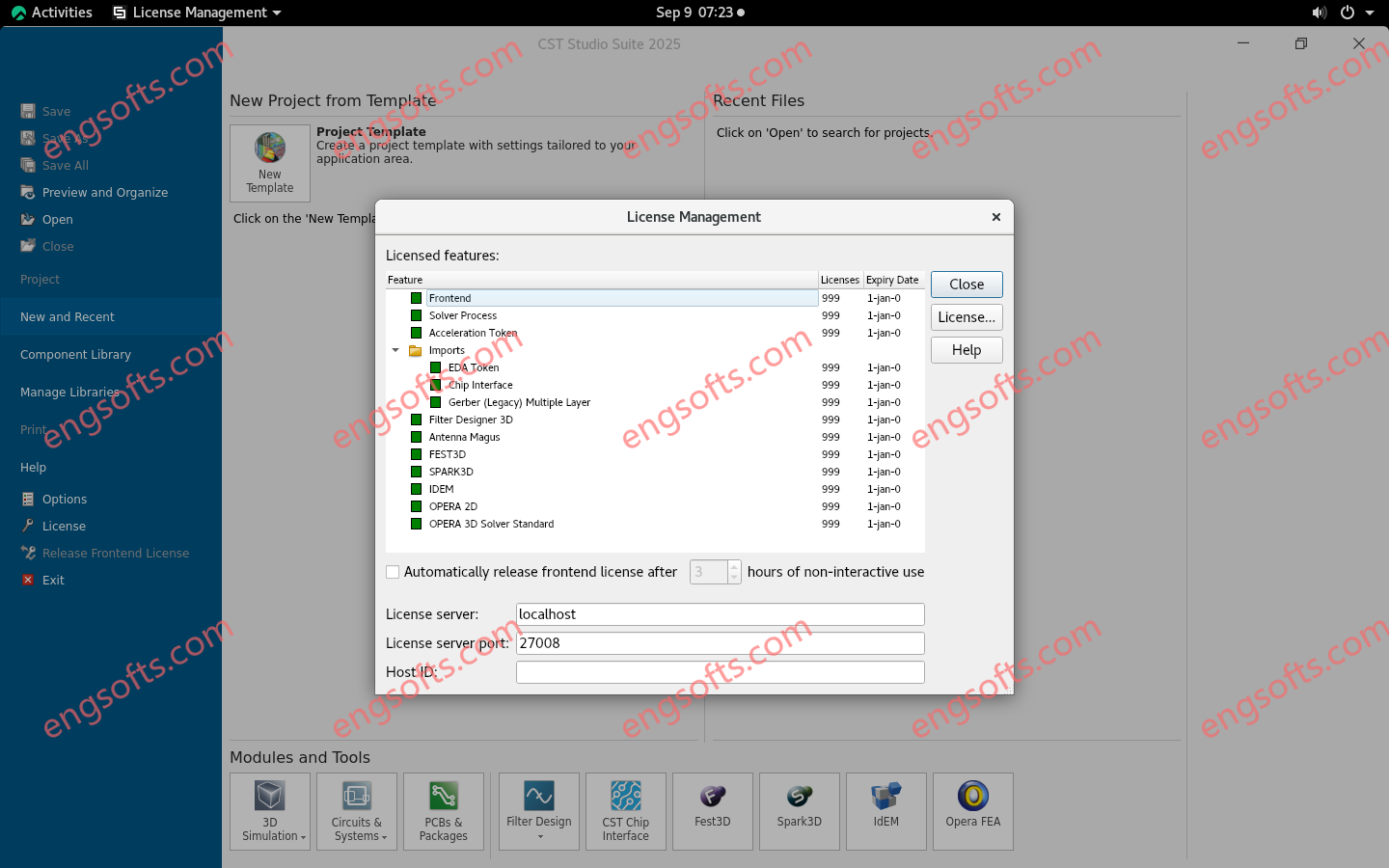

CST Studio Suite 是一款一流的电磁和多物理场仿真软件包,被全球领先的科技和工程公司广泛使用。CST Studio Suite 的求解器覆盖整个频率范围,提供丰富的工具用于产品设计、分析和优化;现在,它还可以与 3DEXPERIENCE 平台集成,实现协作工作流程。推荐使用 64 位 Red Hat Enterprise Linux 和 Suse Linux Enterprise 版本。有关支持的版本的更多信息,请参阅[此处]。 the supported OS guide. 可用版本: 2025 , 2024 , 2023 , 2022 ,… CST Studio Suite 2025 SP5 Linux64 Tested Picture CST Studio Suite 的单一用户界面集成了适用于整个电磁波谱应用的电磁场求解器。这些求解器可以耦合执行混合仿真,使工程师能够以高效便捷的方式分析由多个组件构成的完整系统。与其他 SIMULIA 产品协同设计,可将电磁仿真集成到设计流程中,并从早期阶段就驱动开发过程。 电磁分析的常见主题包括天线和滤波器的性能和效率、电磁兼容性和干扰 (EMC/EMI)、人体暴露于电磁场的情况、电机和发电机中的机电效应以及高功率器件中的热效应。 CST Studio Suite 同时支持 Windows 和 Linux 系统。在 2025 版本中,Linux 用户的体验得到了多项改进。有关功能和改进的完整列表,请参阅新版本随附的发行说明。 入门指南和示例 使用仿真进行设计决策时,正确设置模型至关重要。为了支持和指导用户,CST 提供了多本“入门指南”书籍,组件库中现在包含 500 多个可直接运行的仿真模型。这些模型可以帮助您了解最新版本 CST Studio Suite 的功能,以及如何开始建模和仿真设置。 如果您需要更多帮助,TECHNIA 提供经 Dassault Systèmes 认证的 CST Studio Suite 培训和支持。 Python CST 应用程序更新 最新版本中提供了更多 Python CST 应用程序,带来了新功能和更佳的性能。现在可以使用许多新方法编写自己的 Python 脚本,尤其是在查看 PCB Studio 和 Design Studio(CST 的原理图部分)时。对于 3D 仿真工作室/模块,大多数查询功能都已实现,包括结果获取。3D 建模仍然通过嵌入 VBA 代码来实现。 天线、射频组件和高频求解器 时域求解器 使用 T 求解器对单元结构进行(窄带)仿真,并应用 Floquet 边界条件 现在可以使用 TLM 求解器顺序激励多个同时激励列表 改进了 TLM 离散器和求解器初始化在复杂模型方面的性能 F 求解器 改进了使用四面体网格的方法的性能,尤其是在网格生成和细化过程中的曲率计算 为预定义频率采样提供多频自适应四面体网格细化选项 F 求解器 DDM(域分解方法) 进一步改进的性能 域分解求解器...

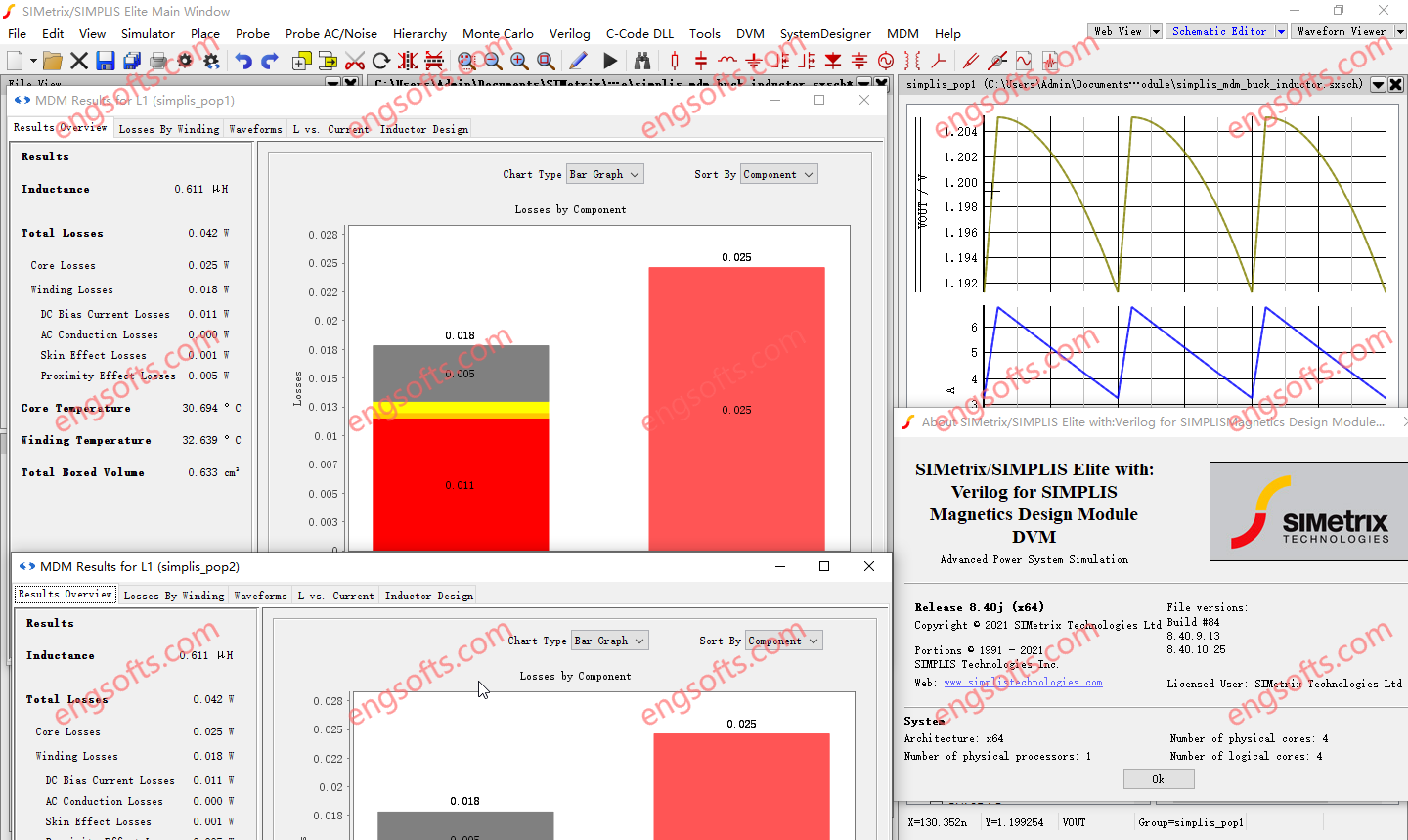

SIMetrix/SIMPLIS 是一款先进的仿真工具,专为高效设计电力电子电路而优化。SIMetrix/SIMPLIS 将精度和收敛性完美结合在一个独特而强大的设计环境中,使电源设计的仿真速度提升 10-50 倍。 可用版本: 9.x , 8.x ,… SIMetrix-SIMPLIS Elite with MDM 8.40 Tested Picture 波形查看器功能 固定探针的独立 X 轴 现在可以强制固定探针生成的曲线图具有独立的 X 轴,从而实现独立缩放。此前,只能在绘制曲线后手动设置 X 轴。 原理图编辑器功能 LTspice® 兼容性 原理图编辑器现在可以直接打开 LTspice® 原理图;只需像往常一样打开文件即可。如果所有使用的模型都受 SIMetrix 仿真器支持,则只需进行少量更改即可运行原理图仿真。 设计验证模块功能 测试计划编辑器 现在可以使用内置的测试计划编辑器创建和编辑测试计划。内置的测试计划编辑器不仅无需第三方电子表格或文本编辑器软件,还提供各种单元输入方面的帮助。这包括下拉选择列表和参数输入辅助。 除了单元格输入辅助外,测试计划编辑器还提供实时错误检查。将鼠标悬停在彩色单元格上即可获取更多信息。 测试计划向导 动态创建 DVM 测试计划,仅包含所需的目标和输入。 提供三个向导: 直流-直流 1 输入 1 输出 直流-直流 1 输入 2 输出 交流-直流 1 输入 1 输出 SIMPLIS 仿真器的新功能 变压器绕组损耗细分 使用 MDM 模拟变压器损耗时,“MDM 结果窗口”中的“变压器设计”选项卡现在提供每个绕组的详细损耗文本细分。用户现在可以查看每种类型(直流偏置、交流传导、趋肤效应和邻近效应)的绕组损耗在每个绕组中的具体数值。 MDM 数据库新增磁芯材料 MagDB 数据库新增 87 种软功率磁性材料。用户可以在 MagDB 窗口中查看这些材料的属性,也可以在 MDM 主窗口的“磁芯”选项卡中选择使用。 用户自定义磁芯损耗分析方程 在向 MDM 数据库添加新的磁芯材料或修改现有材料时,用户现在可以自定义磁芯损耗计算方程。具体操作方法是:打开 MagDB,从列表中选择一种磁芯材料,然后单击“分析方程”按钮,即可打开“磁芯损耗分析方程编辑器”。 该方程用于模拟正弦磁通激励引起的铁芯损耗,输出损耗单位为 W/m³,其输入参数包括频率(单位:Hz)、峰值磁通密度(单位:T)、温度(单位:°C)和直流偏置(单位:A/m)。用户可以使用 JavaScript 编写任意表达式,利用部分或全部输入参数来计算材料的体积铁芯损耗。一些铁芯材料制造商在其数据手册中提供了此类方程。 PFC POP 触发原理图 要启动 SIMPLIS 交流分析,必须先成功完成 SIMPLIS POP 分析。对于具有交流输入的 PFC 电路原理图,目前 POP 分析只能在非常特定的条件下才能成功,即开关频率为交流线路频率的整数倍——而许多 PFC 电路并非如此。 新型 PFC POP 触发器原理图设备可对模拟控制 PFC 整流电路的原理图进行 SIMPLIS POP 和交流分析,包括开关频率可变的电路以及开关频率并非交流线路频率整数倍的电路。 PFC POP 触发器可轻松切换交流和直流输入,并可与数字万用表 (DVM) 或电源配合使用,快速比较 PFC 在交流和直流输入下的波特图。 新增的测试功能可使 PFC POP 触发器与数字万用表 (DVM)...

.2026.png)

.2026.png)