EDA 第2页

Electrical & Power Engineering softwares.

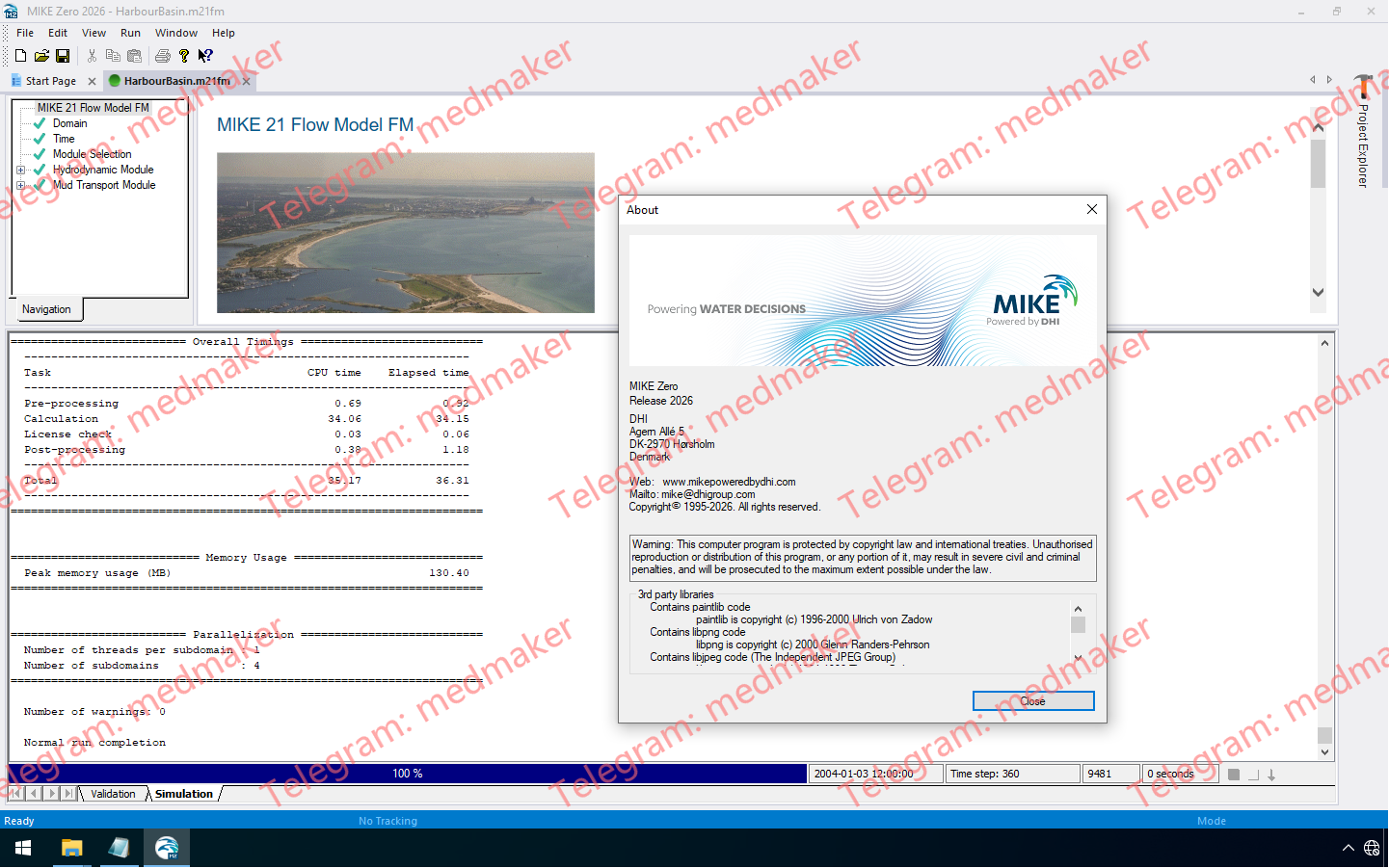

MIKE建模套件是工程师和科学家进行水环境建模的理想之选。该套件包含了DHI公司开发的MIKE内陆和海洋软件的大部分功能。用于在面向项目的环境中设置模拟、进行预处理和后处理分析、演示和可视化。 可用版本: 2026.x , 2025.x , 2024.x ,… DHI MIKE ZERO 2026.0 目前,MIKE Zero 2026.0框架提供以下DHI建模系统: MIKE 21:用于河口、近岸水域和海洋的二维建模系统 MIKE 3:用于深海、河口和近岸水域的三维建模系统 LITPACK:用于沿岸过程和海岸线动力学的建模系统 MIKE SHE:用于耦合地下水和地表水资源的建模系统 More Information in English: DHI MIKE ZERO 2026.0

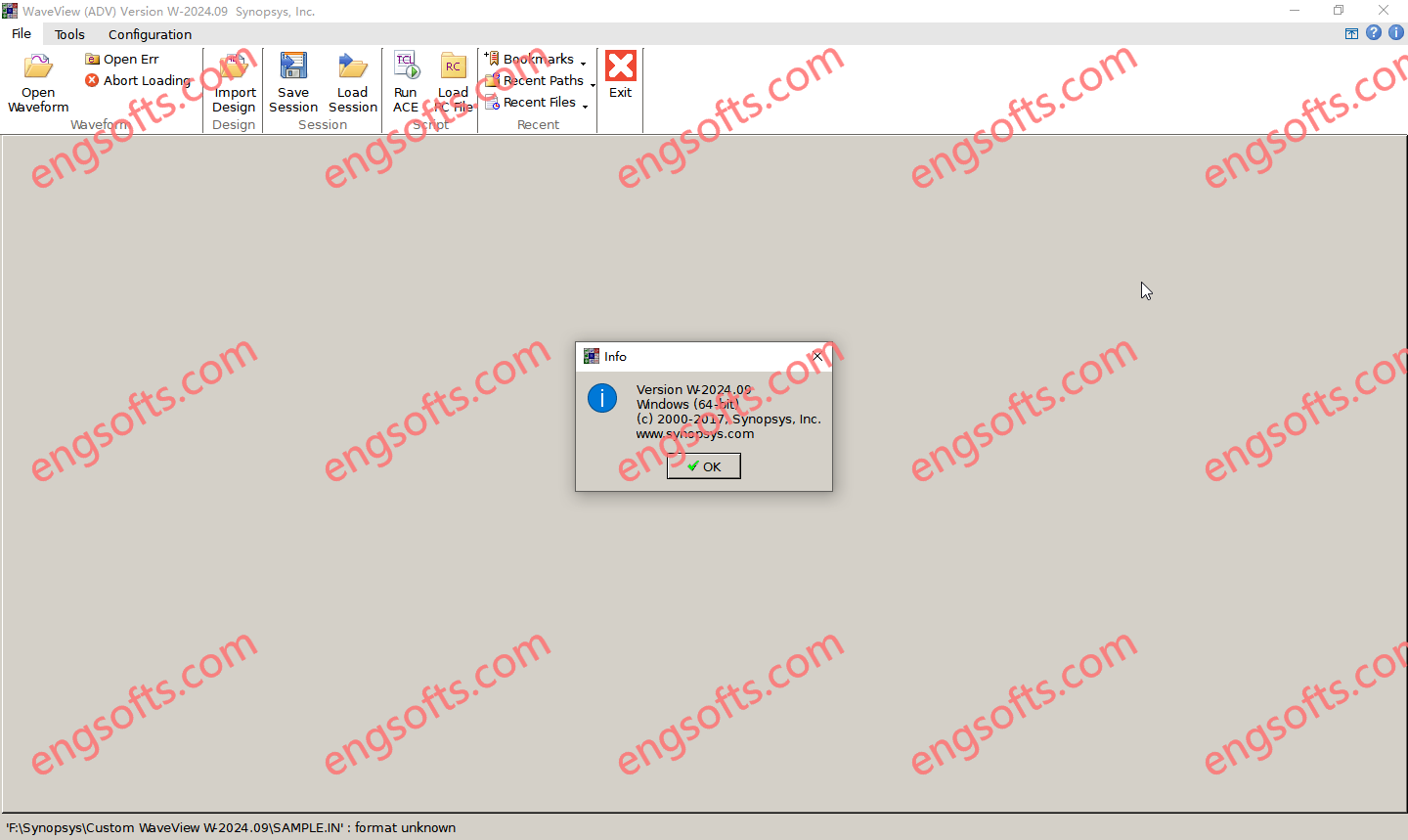

Custom WaveView ADV 提供完整的晶体管级分析和调试环境,用于 SPICE 和 FastSPICE 仿真的预处理和后处理。Custom WaveView ADV 与 Synopsys 的 HSPICE®、FineSim® 和 CustomSim™ 集成,可简化 SPICE 和 FastSPICE 仿真的调试和分析流程,并提高设计效率。 Custom WaveView ADV 与 Synopsys 电路仿真器的结合为设计团队提供了高性能、高效率的仿真调试和分析环境,适用于复杂的 SoC 设计。 Synopsys Custom WaveView ADV 2024.09 Win/Linux64 Tested Picture Custom WaveView ADV 是一款基于网表的调试环境,适用于 SPICE 和 FastSPICE 仿真器,例如 HSPICE、FineSim 和 CustomSim。 Custom WaveView ADV 还与 Custom WaveView 紧密集成,支持波形交叉探测。这些工具协同工作,帮助设计人员在高效的设计调试和波形分析环境中快速执行定制的高级分析。 Custom WaveView ADV 设计浏览器 Custom WaveView ADV 设计浏览器可以快速访问最复杂的层次结构设计数据,并完整显示设计和文件信息。设计浏览器可以导入网表,并允许遍历设计层次结构、显示信号和元件列表,以及追踪层次结构中包含的连接。图 1 所示的这些视图协同工作,可以快速访问设计层次结构的所有内容。除了显示设计层次结构之外,设计浏览器还会显示包含该设计的相关文件层次结构。强大的搜索功能允许用户根据字符串、信号、实例和模块名称在层次结构中查找设计组件。 More for English: Synopsys Custom WaveView ADV 2024.09

Tessent Silicon Lifecycle Management solutions include advanced debug, safety & security features and in-life data analytics to meet the evolving challenges of today’s silicon lifecycle. Ensure the highest test quality, accelerate yield ramp and improve safety, security and reliability across the silicon lifecycle using best-in-class solutions for design-for-test (DFT), debug and in-life monitoring plus powerful data analytics. Tessent Advanced DFT Address the challenges of in-system test for today’s complex SoCs and chiplets with market-leading logic and memory test products that combine capabilities in a powerful test flow to ensure total chip coverage. Tessent Embedded Analytics Close productivity gaps using actionable insights from embedded analytics that shorten total development time, accelerate debug and reduce risk and cost to ensure timely market...

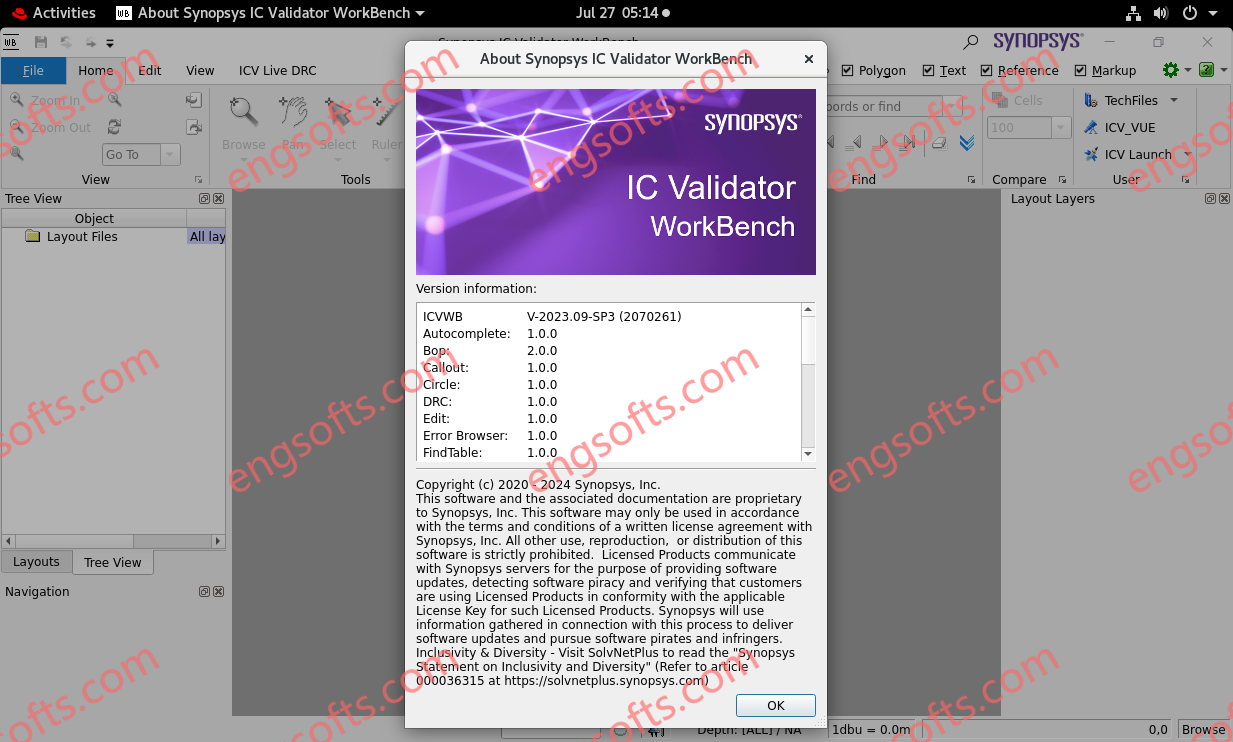

IC Validator WorkBench (ICVWB) 是一款功能强大、性能卓越的分层版图可视化和分析工具。它能够快速查看和编辑从小型 IP 模块到完整芯片数据库的 GDSII、OASIS® 和 LEF/DEF 版图。此外,ICVWB 还可以让您轻松可视化和访问 IC Validator (ICV) 物理验证工具套件正在检查的版图数据,并查看物理验证结果。ICVWB 基于之前的 IC WorkBench Edit/View Plus (ICWBEV) 产品开发而来,并针对物理验证设计人员的需求进行了改进。 Synopsys IC Validator Workbench 2023.09 Linux64 Tested Picture 优势 以低内存开销快速打开大型 GDSII、OASIS 和 LEF/DEF 文件。此外,缓存文件可以显著缩短后续会话的加载时间。 即时打开优化后的 OASIS 文件。 轻松调试单元和形状的层次结构和布局。 通过切割层功能,快速交互式地确定并显示形状连接性。 改进了对 IC Validator (VUE) 应用程序的支持,用于查看和纠正 DRC 和 LVS 错误。 提供多种模式,用于合并不同格式和数据库单位 (DBU) 的版图。 比较版图和单元,并生成差异报告/版图。 在分层版图中为 Sentaurus 定义 TCAD 仿真域。 More for English: Synopsys IC Validator Workbench 2023.09 Linux64

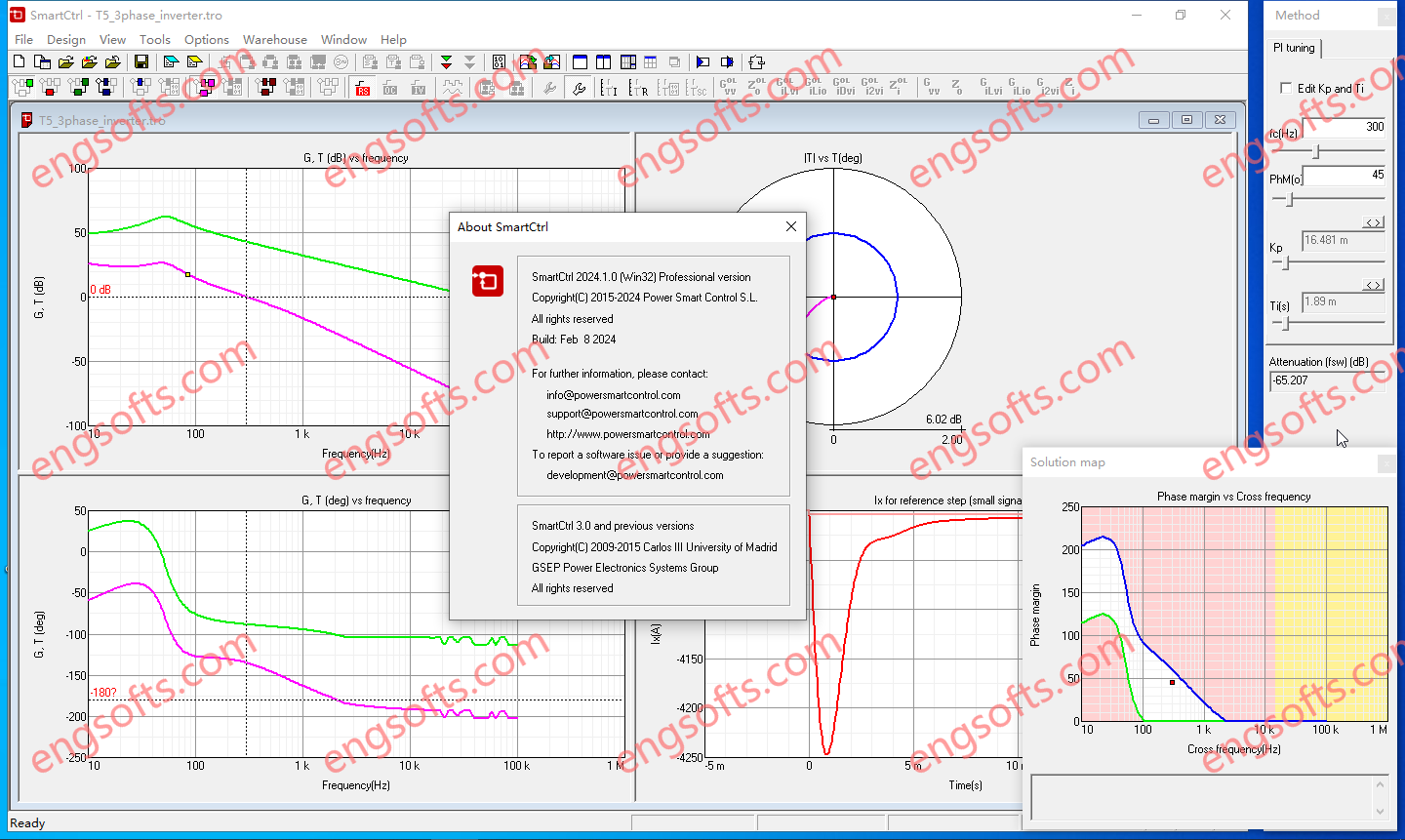

SmartCtrl 2025.1为您带来更加直观高效的控制系统,树立控制技术新标杆。 PSC SmartCtrl 2024.1 Tested Picture 新型交流-直流转换器拓扑:三相PFC升压转换器。 全面支持两种不同的控制结构: 🔺 Alpha-Beta 控制 🔺 DQ 控制 可选择两种主要的滤波器类型: 🔺 L 滤波器 🔺 LCL 滤波器 对于 LCL 滤波器,可以选择主动阻尼或被动阻尼。 可针对 Alpha-Beta 控制结构调整比例谐振补偿器。 可调整两种不同锁相环 (PLL) 的控制回路: 🔺 同步参考系锁相环 (SRFPLL) 🔺 正交信号发生器 – 同步参考系锁相环 (QSG-SRFPLL) 已实现四种常用的 EMI 滤波器结构。 包含一种新的传感链定义方式。 可选择五种调制器类型。 已开发系统级稳定性分析工具。分析 EMI 滤波器的输出阻抗与受控转换器的输入阻抗。 设计可以实现 s 域和全数字控制回路。 独立的浮动窗口,提升用户体验。 可导出到第三方仿真器。 自动生成 C 代码。 More for English: PSC SmartCtrl 2025.1

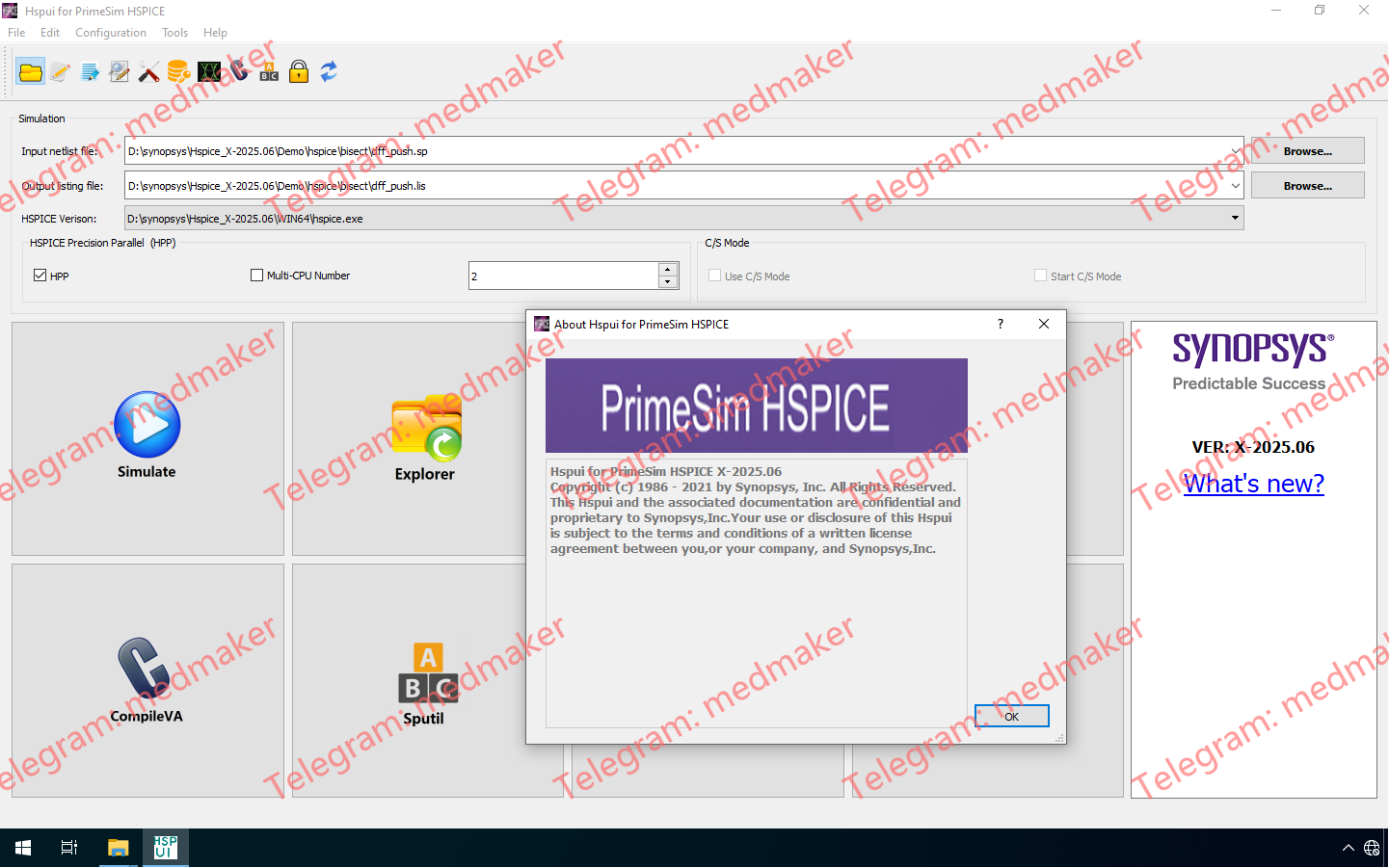

PrimeSim HSPICE is the industry’s ‘gold standard’ for accurate circuit simulation and offers foundry-certified MOS device models with state-of-the-art simulation and analysis algorithms. With extensive usage in chip/package/board/backplane signal integrity simulation, cell and memory characterization, and analog mixed signal IC design, PrimeSim HSPICE is the industry’s most popular, trusted and comprehensive circuit simulator. Available versions: 2025.x , 2024.x ,… Synopsys PrimeSim HSPICE 2025.6 Win64 Tested Picture PrimeSim™ SPICE is a high-performance SPICE circuit simulator for analog, RF, and mixed-signal applications. PrimeSim SPICE offers a unique multi-core/multi-machine scaling and heterogeneous compute acceleration on GPU/CPU delivering faster runtime with sign-off accuracy. PrimeSim SPICE supports high-frequency noise analysis, efficient S-Parameter handling while offering advanced analysis capabilities for periodic and non-periodic time-domain and frequency-domain...

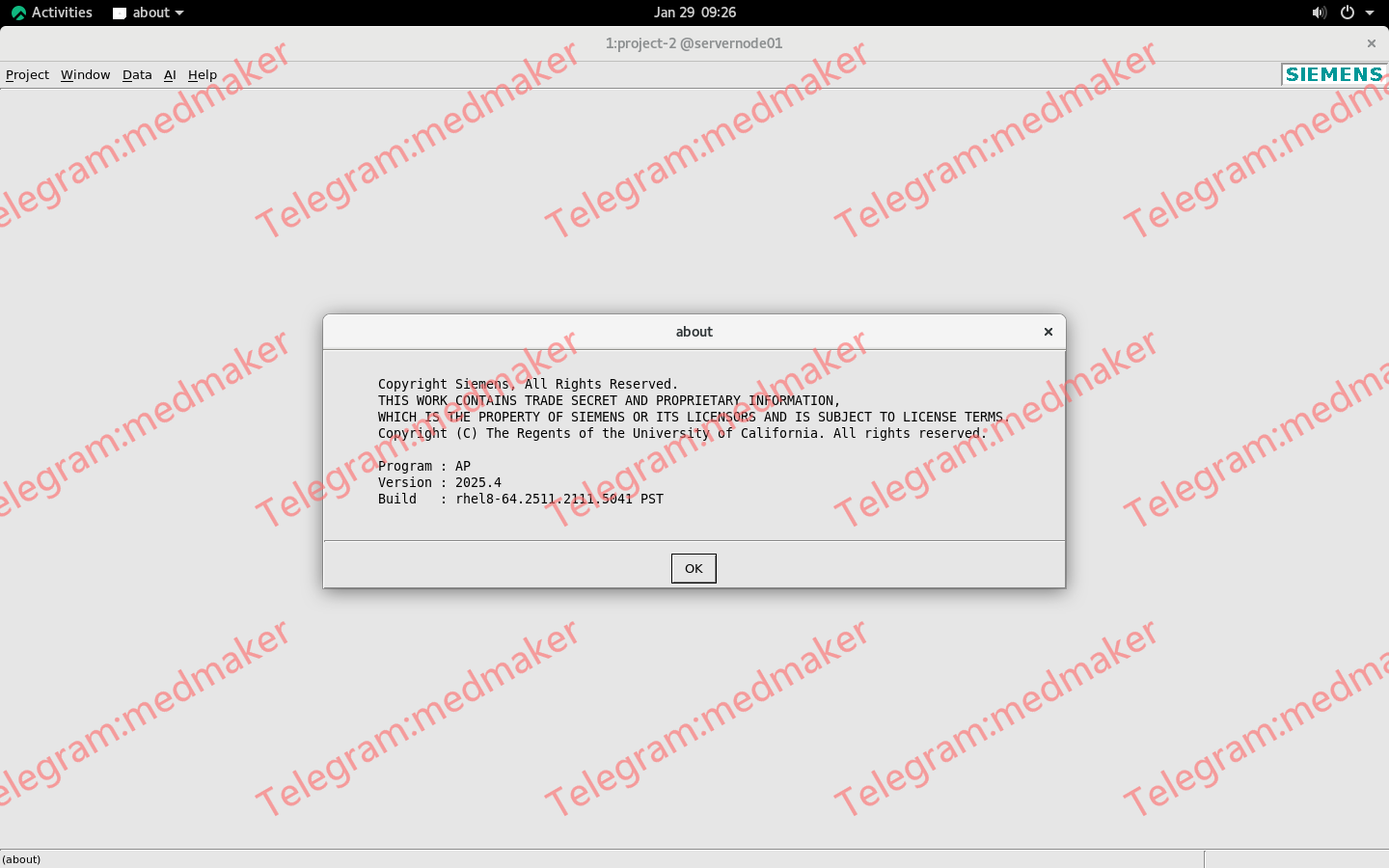

Aprisa 是一款面向现代 SoC 的以详细布线为中心的物理设计解决方案。无论您的目标是加快流片速度、降低总体拥有成本,还是实现最低功耗,Aprisa 都凭借其专利技术和一流的支持,确保您取得成功。 Aprisa 为复杂的数字 IC 设计提供完整的顶层分层设计和模块级实现功能。其以详细布线为中心的架构和分层数据库,能够在极具竞争力的运行时间内实现快速设计收敛和最佳结果质量 (QoR)。 可用版本:2025.x , 23.x , … Siemens Aprisa 2025.4 Linux Tested Picture 缩短设计收敛时间 统一的数据模型将真实的布线信息和寄生参数引入流程中的任何引擎和步骤。设计人员可以在布线前阶段就自信地了解其设计可实现的功耗、功耗和功耗比 (PPA),从而大幅减少全流程迭代次数。 AI 驱动的宏布局技术 只需经验丰富的设计师所需时间和精力的一小部分,即可实现专家级设计师品质的宏布局。无需进行全流程迭代即可锁定给定设计的最佳宏布局。 低功耗专利技术 将低功耗作为功耗敏感型设计的主要设计指标,同时不牺牲性能。设计人员可以选择满足其最佳 PPA 的权衡方案,从而减少流片最后阶段的功耗清理工作。 More for English: Siemens Aprisa 2025.4 Linux

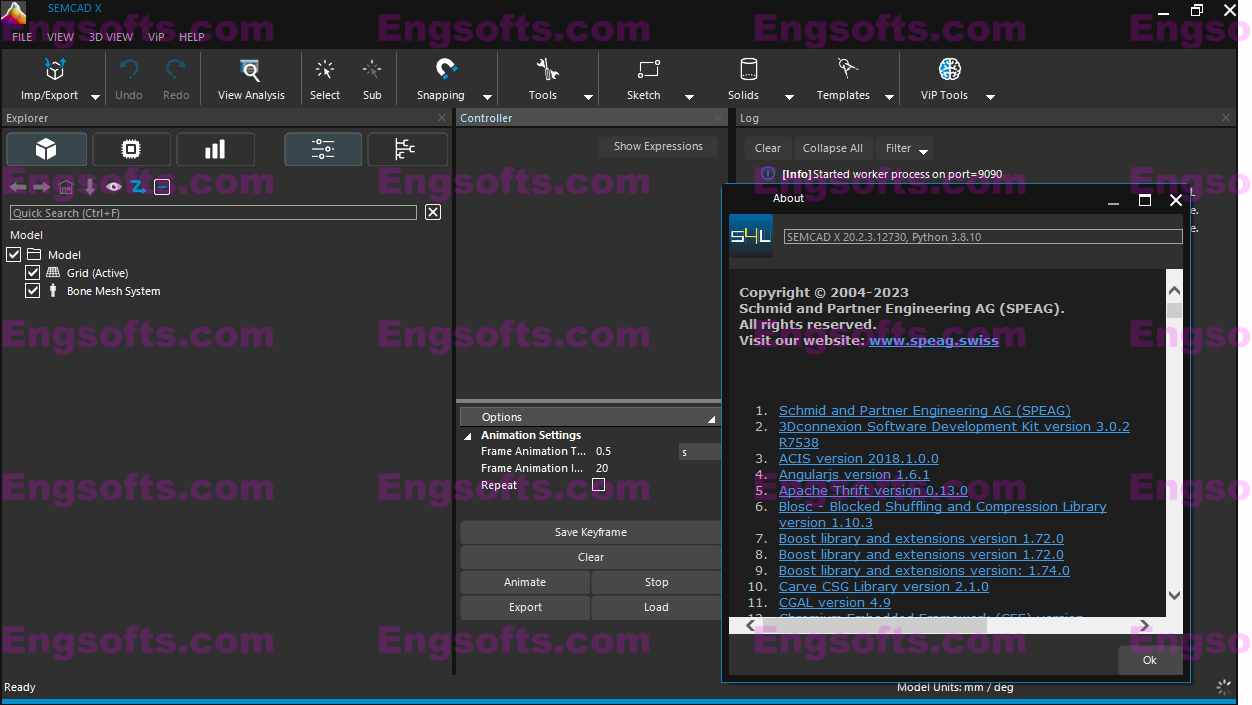

SEMCAD X Matterhorn V20.2 offers new features and major enhancements that further strengthen our customers’ in silico tool set for research, device design and optimization, and compliance evaluation. The highlights of SEMCAD X Matterhorn V20.2 in a nutshell: Python scripting: discover the power, flexibility, and comfort of SEMCAD X’s integration with JupyterLab together with the upgrade to Python V3.8 Dosimetry/compliance: SEMCAD X is compliant with the latest and forthcoming IEEE/IEC mmWave APD and SAR standards Reduced storage: results from full-wave simulations can now be automatically compressed, either on-the-fly or for already computed simulation results – resulting in massive file size savings (up to 20x) Productivity tools: explore a whole set of powerful new modelling tools and a streamlined graphical user interface (GUI) for an...

Solido Design Environment is a comprehensive AI-powered design environment for all SPICE-level design and verification, and is a single unified solution for nominal and variation analysis. Used by thousands of designers to produce the most competitive products in hp computing, AI, IoT, automotive and mobile applications. Brute force-accurate signoff variation 1000X faster Orders of magnitude faster than brute-force simulation Full coverage verification across PVTs and Monte Carlo Brute-force Monte Carlo and SPICE accurate high-sigma verification Variation-aware design sensitivity, debugging and optimization Comprehensive design environment to boost engineering efficiency Significantly reduces documentation time/effort Identifies design weaknesses previously undetectable Easy to use and deploy Intuitive GUI for interactive design and analysis GUI or batch mode Works with all process technologies Integrated with...

Precision offers vendor-independent FPGA synthesis. It provides best-in-class performance and area, high-reliability design capabilities and tight links to simulation and formal equivalency checking. Siemens offers three unique FPGA synthesis solutions – Precision Hi-Rel, Precision RTL Plus and Precision RTL. Precision’s products are tightly integrated with Siemens’ FormalPro LEC for equivalency checking and HDL Designer for design capture and design verification using ModelSim/Questa. Precision RTL Precision RTL, Siemens entry-level FPGA synthesis product, offers best-in-class quality of results with a vendor-independent FPGA synthesis solution. Precision RTL Plus Precision RTL Plus, adds DO-254 certification utilities for mil-aero applications, on-chip debug and validation and resource optimization for DSPs and RAMs. Precision Hi-Rel Precision Hi-Rel, enhances Precision RTL Plus with automated mitigation of SEUs/SETs in...