EDA

Electrical & Power Engineering softwares.

Synopsys 3DIC Compiler 2024.09 Linux Synopsys Avalon 2024.09 Linux Synopsys Certitude 2025.06/2024.09 Linux Synopsys Chamber Matching 2022.12 Synopsys CODE V 2025.03 Synopsys LightTools 2025.03 Synopsys LucidShape 2024.09 Synopsys LucidShape CAA V5 Based 2024.09 Synopsys coreTools 2025.06/2024.09 Linux64 Synopsys Custom Compiler 2024.09-SP1 Linux Synopsys Custom WaveView 2025.06 Synopsys DVE 2025.06/2024.09 Linux64 Synopsys Embedit 2025.06 Linux64 Synopsys ESP 2024.09 Linux64 Synopsys Euclide 2025.06 Win/Linux Synopsys FineSim 2025.06 Linux64 Synopsys Formality 2025.06/2024.09 Linux64 Synopsys Fusion Compiler 2025.06/2024.09 Linux64 Synopsys HSPICE 2025.06/2024.09 Win64/Linux64 Synopsys IC Compiler 2025.06/2024.09 Linux64 Synopsys IC Compiler II 2025.06/2024.09 Linux64 Synopsys IC Validator 2025.06/2024.09 Linux64 Synopsys IC Validator Workbench 2024.09 Linux64 Synopsys ICE Speed Adaptor 2023.09 Linux64 Synopsys Laker OA 2023.09 Linux64 Synopsys Library Compiler 2025.06/2023.12-SP3 Linux64 Synopsys LucidDrive 2024.03...

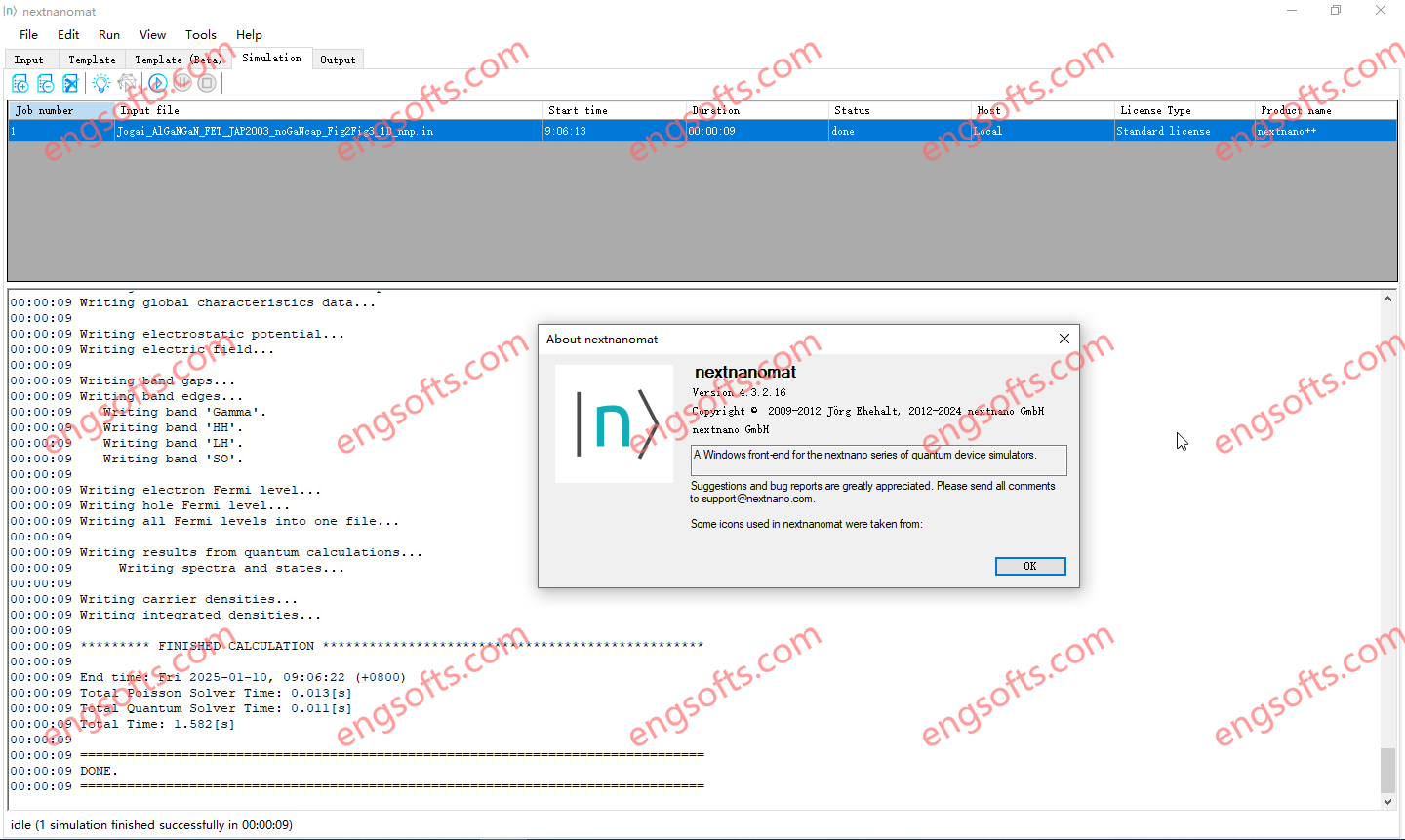

nextnano++软件包提供了一系列工具,用于设计、优化和分析任意几何形状的一维、二维和三维光电纳米器件。该软件包是模拟大量半导体结构特性的最佳选择。它允许您设计由量子阱、量子线和量子点构成的光电器件。 可用版本: 2026.x ,2025.x ,2024.x ,… NextNano++ Package 2026.02 使用 nextnano++ 软件包,您可以获得高级计算功能,包括能带结构、态密度、电荷分布、波函数、应变、压电效应、光谱、量子化电导等诸多计算。 此软件包包含: nextnano++ nextnano3 nextnano.MSB nextnanomat nextnanopy nextnano 拥有全面的高级功能套件,包括用户友好的图形化工作流程管理器、与 Python 库的无缝集成以及丰富的实用示例库,可加速学习和个性化设计开发。这有助于我们的客户缩短产品上市时间和发布周期,保持高性能并推动下一代技术的发展。 经济实惠,性价比高 nextnano 通过识别潜在问题、优化结构设计并提供具有竞争力的价格,帮助降低纳米结构研发成本。这使其成为个人研究人员和研究团队的经济之选,确保资源的高效利用。 高效省时 nextnano 能够快速准确地模拟复杂的纳米结构,从而节省您宝贵的时间,无需耗时的实验方法。 功能多样 nextnano 擅长模拟各种纳米结构,包括量子阱、纳米线、纳米点以及更复杂的结构,例如超晶格和异质结。 灵活便捷 nextnano 提供无与伦比的灵活性,可轻松自定义模拟参数,以满足您的特定研究需求。我们的软件旨在方便用户集成自己的模型和参数,为客户提供无缝体验。 More Information in English: NextNano++ Package 2026.02

The Physical Layer Test System (PLTS) 是高速互连(如电缆、背板、PCB 和连接器)信号完整性测量和数据后处理的行业标准。 可用版本: 2026.x ,2025.x ,… Keysight Physical Layer Test System (PLTS) 2026.0 全球众多信号完整性实验室在研发原型测试阶段都受益于PLTS的强大功能。如今1.6Tbps的互联网基础设施需要进行多端口通道分析,以减少可能导致比特错误的串扰问题。全新的PLTS 2024现已升级为功能强大的64位应用程序,能够使用更大的内存空间来存储大型数据文件,并支持16端口或32端口的S参数测量。 More Information in English: Keysight Physical Layer Test System (PLTS) 2026.0

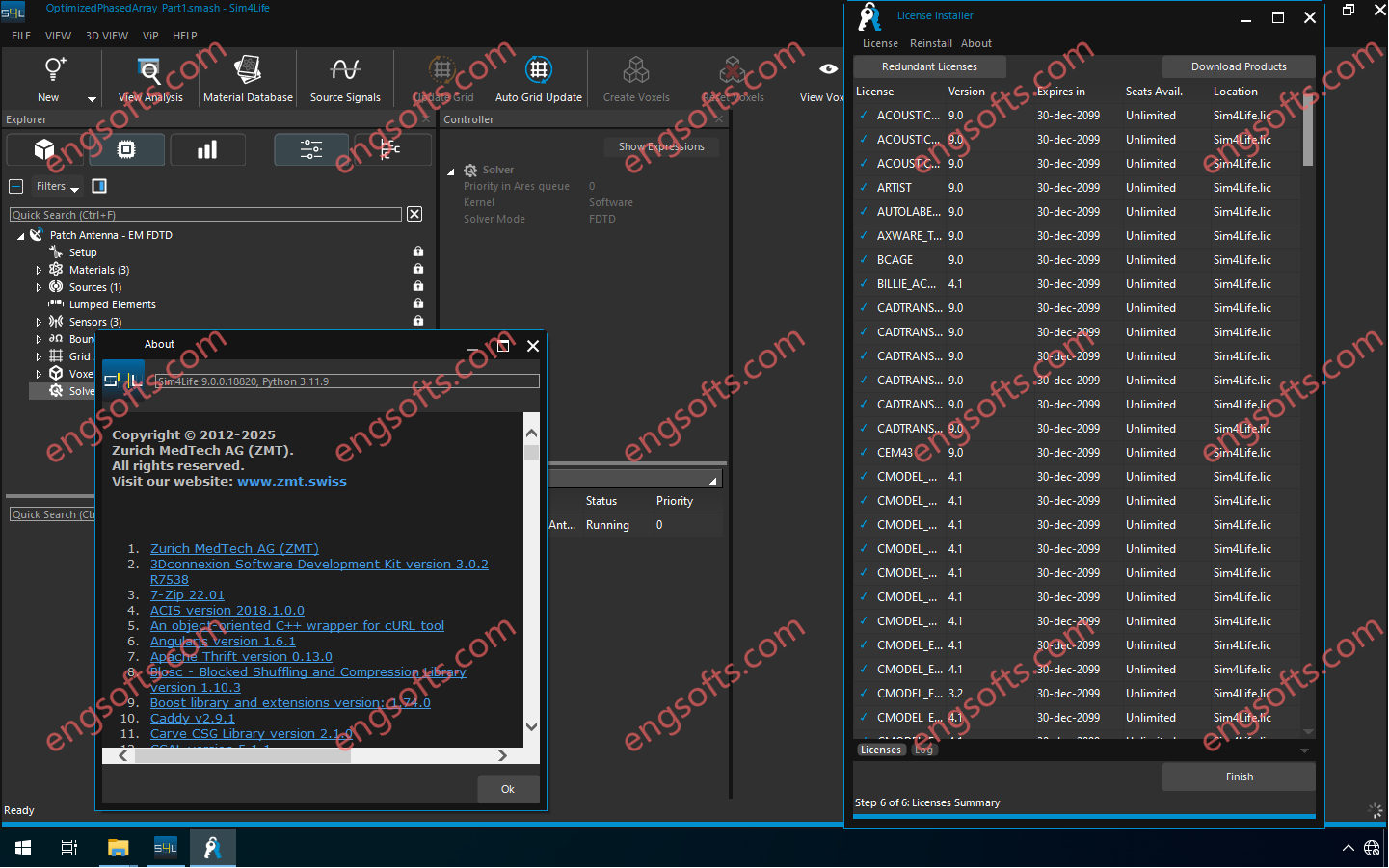

Sim4Life V9.4 是我们最新的仿真平台,适用于计算生命科学研究、设备设计和优化,以及安全性和电磁兼容性评估。 Sim4Life V9.4 进一步巩固了其作为神经刺激建模首选平台的地位,针对严苛的实际应用需求,在质量、鲁棒性和易用性方面进行了针对性改进。 可用版本: 9.x , 8.x , 7.x ,… ZMT Sim4Life 2025 v9.0 Tested Picture 神经刺激研究通常需要的不仅仅是电场映射。现代工作流程通常包括: • 解剖结构精细的个性化模型, • 高分辨率低频电磁模拟, • 神经元级响应建模, • 安全相关参数的评估,例如诱导组织加热和电荷注入。 Sim4Life 将这些组件集成到一个单一的计算框架中,从而实现可控的计算机模拟研究,将基于图像的建模、物理学和生理学联系起来。 9.4 版本在此基础上进行了扩展。Z43 的合作伙伴 IT’IS 基金会最近为具有具体设计、监管和转化需求的工业客户开展了两项定制研究项目,这两项项目不仅展示了该平台的功能,也体现了直接影响此版本改进的各类高要求应用。 Sim4Life 9.4 Release Notes More Information in English: ZMT Sim4Life 2025 v9.0

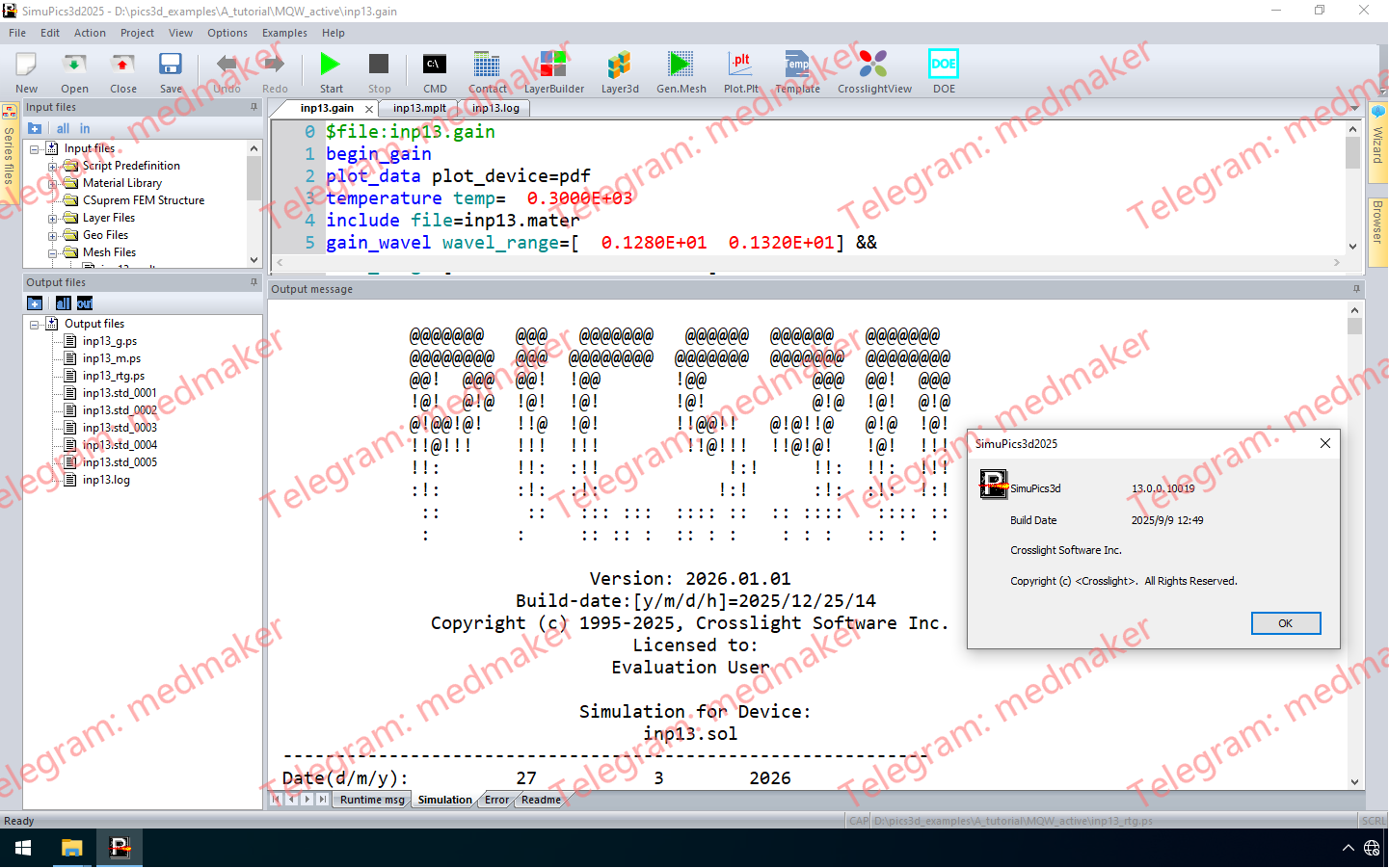

PICS3D(三维光子集成电路模拟器)是一款先进的三维模拟器,适用于表面发射和边缘发射激光二极管、半导体光放大器 (SOA) 以及其他类似的有源波导器件。它将二维/三维半导体方程(例如漂移扩散方程、泊松方程等)与横向和纵向的光模式耦合。量子阱/量子线/量子点的光学增益和自发辐射率等光学特性均采用自洽计算方法进行计算。 可用版本: 2025.x , 2024.x ,… Crosslight PICS3D (LASTIP) 2025.0 自 2016 版起,二维激光求解器 (LASTIP) 的功能也已集成到 PICS3D 中:这使得用户能够轻松模拟激光器件,而无需考虑显著的纵向效应,并为从事各种激光器件设计工作的用户提供更大的灵活性。 点击此处查看详情。 应用 边发射激光器的二维和三维仿真 DFB 和 DBR 激光器以及其他具有强纵向效应的器件 垂直腔面发射激光器 (VCSEL) 半导体光放大器 (SOA) 超辐射发光二极管 (SLED) 波导光电探测器 (WPD) 电吸收调制器 (EAM) 可调谐激光器和外腔激光器 半导体环形激光器 采样光栅激光器、增益耦合激光器和二阶光栅 自加热和热滚降 各种量子阱/量子线/量子点结构的模型 量子级联激光器(子带间模型) More Information in English:Crosslight PICS3D (LASTIP) 2025.0

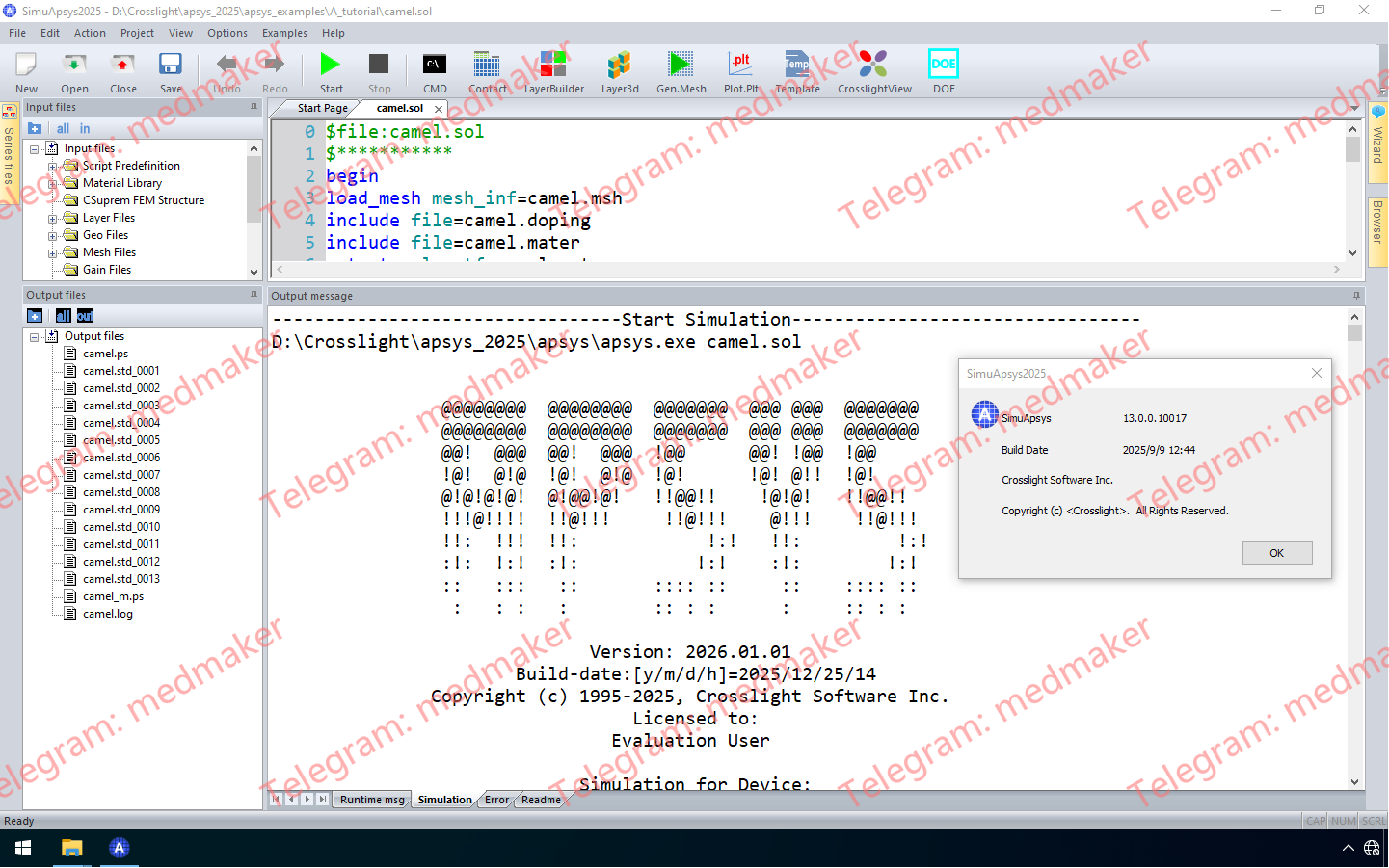

APSYS(半导体器件高级物理模型)基于二维/三维有限元分析,用于模拟化合物半导体器件(以硅为特例)的电学、光学和热学特性。该软件重点关注能带结构工程和量子力学效应。此外,其包含的各种光学模块也使得该仿真软件包在涉及光敏或发光器件的应用中极具吸引力。 可用版本: 2025.x , 2024.x ,… Crosslight APSYS 2025.0 应用 二极管、晶体管及其他各种硅器件 LED 和 OLED 太阳能电池 光电探测器 (PD) 高电子迁移率晶体管 (HEMT) 异质结双极晶体管 (HBT) 谐振隧道二极管 (RTD) 量子阱红外光电探测器 (QWIP) 具有强量子力学效应的小型 MOS 器件 (Quantum-MOS) 功率器件 特性 从上次保存的状态重新启动 业界领先的数值收敛性 丰富的材料宏库 热载流子的流体动力学模型 量子隧穿与输运 热电子发射模型 传热方程 深能级陷阱及其动力学 界面态 Poole-Frenkel模型 自洽量子阱计算 温度相关模型 碰撞电离 More Information in English:Crosslight APSYS 2025.0

nextnano.NEGF软件包是一款专为模拟平面结构中的量子输运而设计的尖端软件包。它是精确模拟量子级联激光器(QCL)、量子级联探测器(QCD)、超晶格和谐振隧道二极管(RTD)的最佳选择。借助nextnano.NEGF软件包,您可以获得先进的计算功能,包括能带结构、能量分辨载流子密度和态密度、光增益、输出功率和L-I-V特性、电光转换效率等诸多方面的计算。我们自豪地宣布,nextnano.NEGF是目前市面上用于模拟QCL量子输运的最佳商用工具。 可用版本: 2026.x ,2025.x ,2024.x ,… nextnano.NEGF 是一款先进的计算工具,也是 nextnano.NEGF 软件包的核心引擎。它采用前沿的非平衡格林函数 (NEGF) 理论,能够精确模拟平面结构中的量子输运,并考虑一系列散射过程,包括纵向极化光学声子散射、声学声子散射、带电杂质散射、界面粗糙度散射、合金散射以及电子-电子散射。 nextnano.NEGF 的开发目标是在有限的计算时间内为一维系统提供高精度的结果,同时它还能够计算光谱。这些特性,加上对各种散射过程的覆盖,使其成为对量子级联激光器 (QCL) 和谐振隧道二极管 (RTD) 等异质结构进行高精度模拟的理想工具。 nextnano.NEGF 工具旨在利用非平衡格林函数 (NEGF) 形式主义对半导体器件进行真实、精确的量子模拟。它模拟了由一维异质结构构成的各种半导体器件的电子输运和光学特性,例如: 量子级联激光器 (QCL) 量子级联探测器 (QCD) 谐振隧穿二极管 (RTD) 量子阱红外探测器 (QWIP) 超晶格 (SL) II型超晶格 (T2SL) 带间级联激光器 (ICL) More Information in English: NextNano NEGF 2026.02

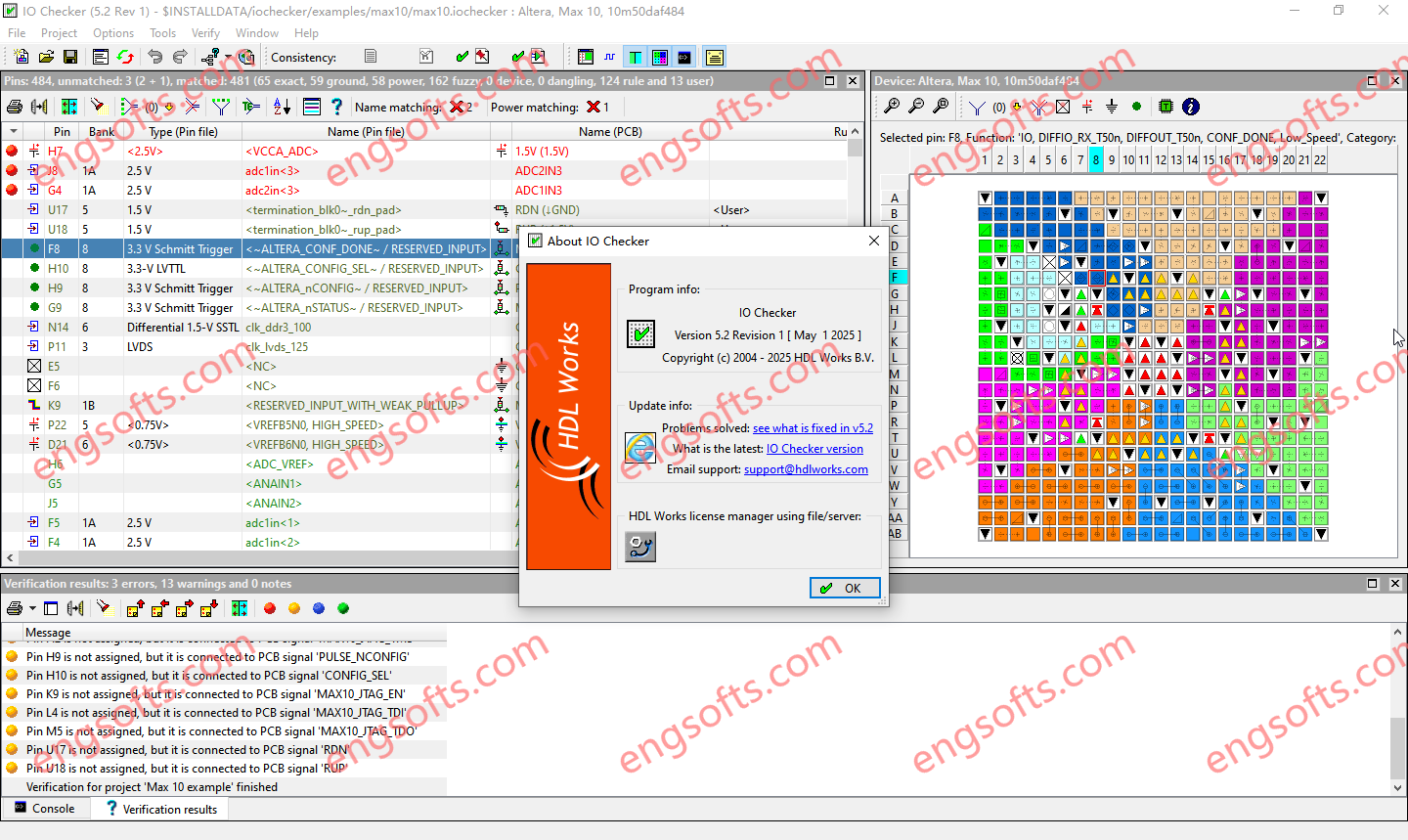

IO Checker 使用基于正则表达式的规则来匹配 FPGA 和 PCB 设计环境中的信号名称。即使单个信号可能存在差异,该工具也能验证匹配组。这些规则可以自动生成,也可以由设计人员进行微调。自动化方法通常可以匹配 80% 到 90% 的器件引脚。 可用版本: 5.2.x , 5.1.x ,… HDL Works IO Checker 5.2 Rev1 Win/Linux IO Checker 的灵活性使其可用于任何设计流程,无需任何设计方法论。规则生成器结合排序后的问题视图,使工程师能够在半小时内验证一个拥有 1000 多个引脚的器件。 一旦定义了项目及其规则,保持 FPGA 和 PCB 数据的一致性就变得非常简单。所有过期的文件都会一次性处理,并且所有更改都会被报告。 功能与优势 使用正则表达式比较 FPGA 和 PCB 引脚名称 创建 &更新 FPGA 约束文件 自动生成规则 电源引脚电压检查 用户可自行确认已验证的差异 一键验证和一致性检查 报告引脚列表和网络列表中的增量更改 专注于十几个差异,而不是上千行代码 适用于任何设计流程 HTML 报告 What is new in the 5.2 release More Information in English: HDL Works IO Checker 5.2

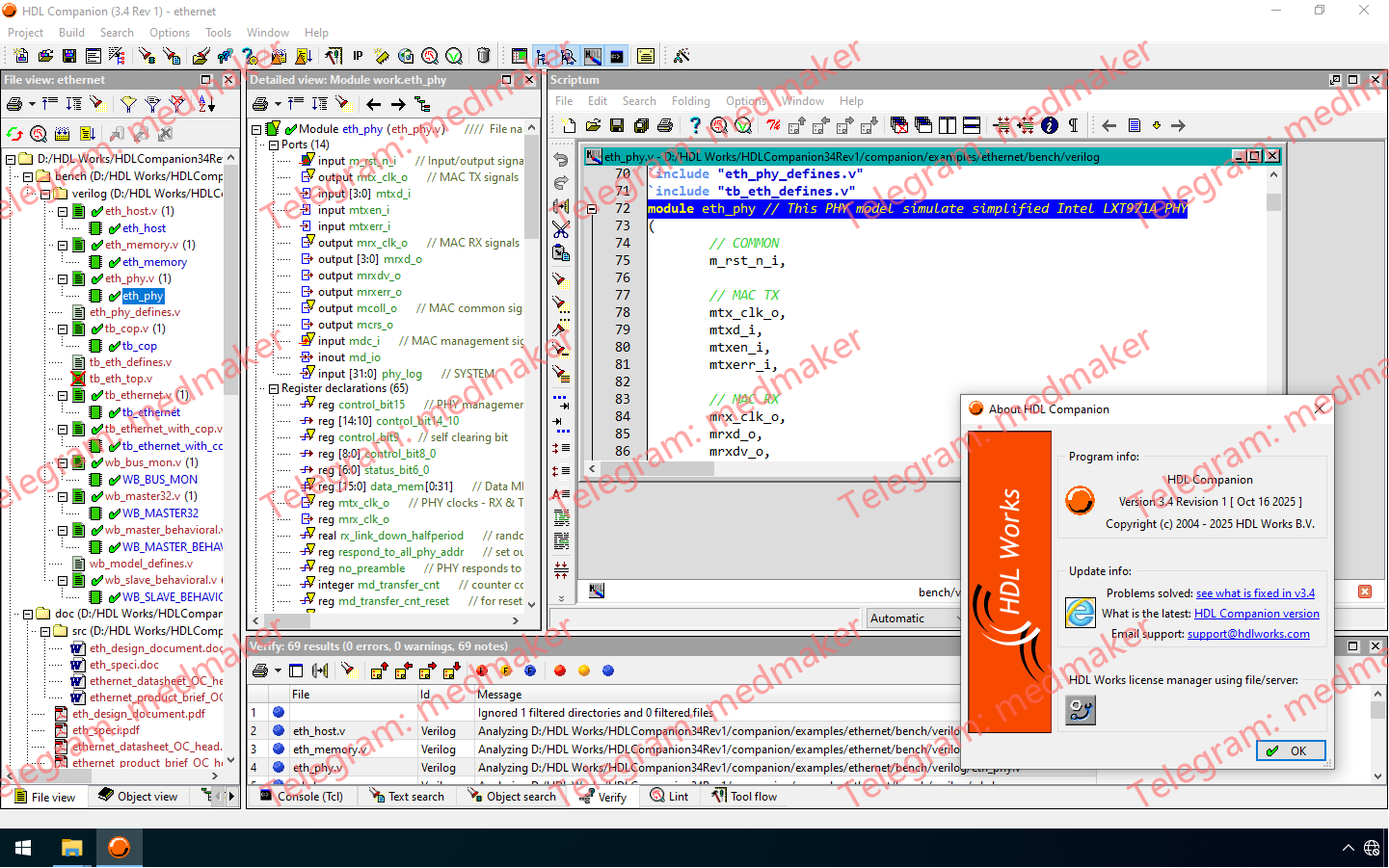

HDL Companion 是 HDL 设计师的瑞士军刀。它能帮助您快速掌握并维护任何 HDL 设计的概览,包括第三方 IP、遗留代码和其他 HDL 源文件。只需将完整的设计目录和设计文件拖入 HDL Companion,即可在几秒钟内生成完整的设计概览,揭示设计的各个方面。其图形用户界面 (GUI) 提供了多种导航方式,方便您浏览设计并查找所需细节。 可用版本: 3.4.x , 3.3.x ,… HDL Works HDL Companion 3.4 Rev1 Win/Linux Tested Picture 内置的模糊解析器可以接受任何 SystemVerilog、VHDL 或混合 HDL 设计代码;即使代码不完整或包含错误。语法正确的 HDL 代码也可以进行代码检查,以发现编译器未报告的问题。 HDL Companion 采用独特的布局,包含三个主窗口和一个控制台窗口,它们共同提供从高层结构到源代码细节的完整设计概览。其出色的导航功能(包括信号跟踪)使您可以轻松查找对象并查看其详细信息。 控制台窗口显示所有语法错误和警告,您可以使用从控制台窗口到 Scriptum 窗口的热链接轻松地在 HDL 源代码中找到它们。控制台窗口还可以用作 Tcl 解释器,可以在其中执行任何 Tcl 脚本或 shell 命令。 What is new in 3.4 More Information in English: HDL Works HDL Companion 3.4

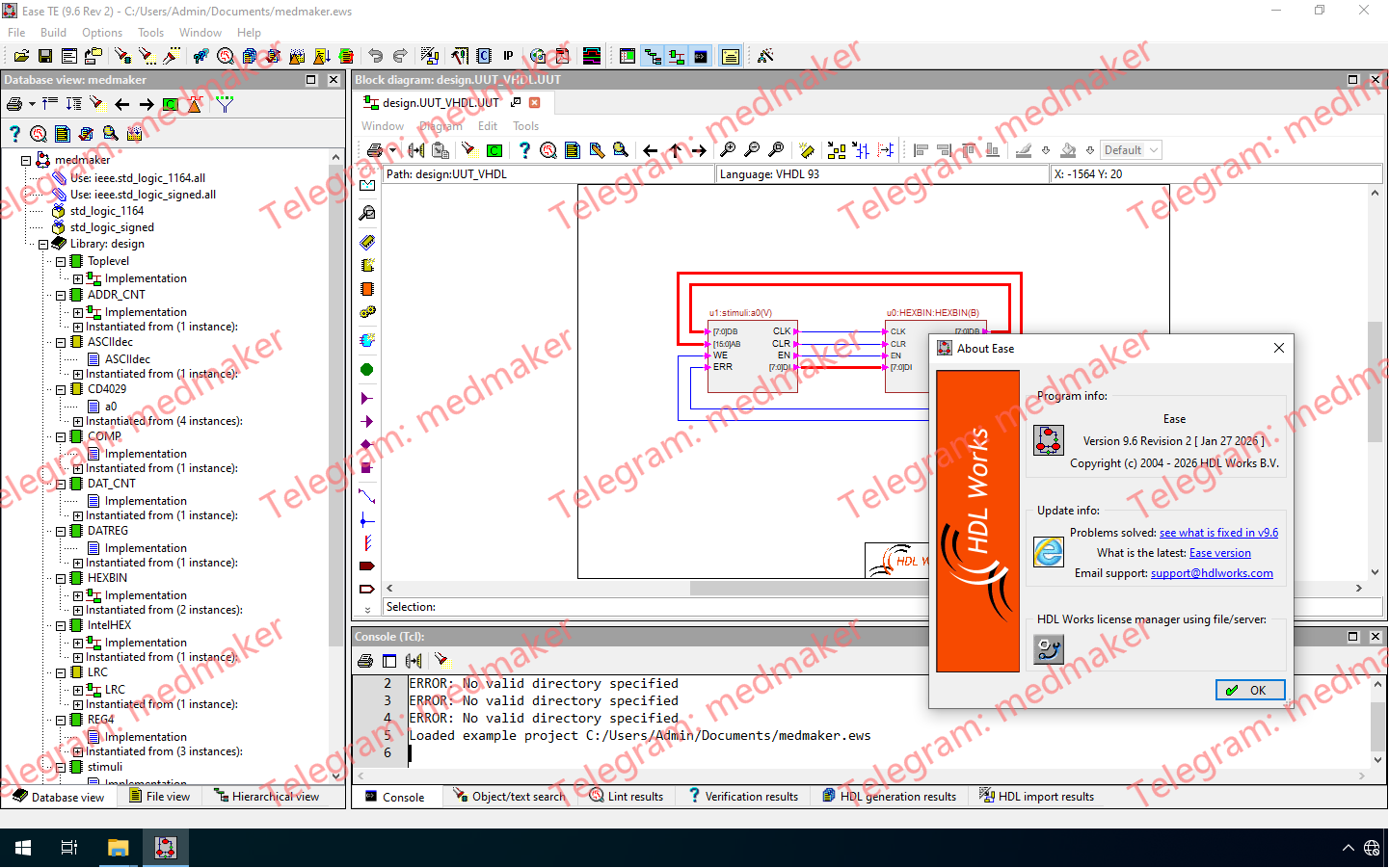

EASE 兼具图形化和文本化两种 HDL 输入方式,让您可以自由选择。您无需精通 Verilog 或 VHDL。创建新设计时,只需使用图形和文本混合方式输入即可。EASE 会自动为您生成所选语言(VHDL 或 Verilog)的优化 HDL 代码。行业标准的版本控制环境可处理设计和配置管理,支持多个用户同时在同一个 EASE 项目中工作。 可用版本: 9.6.x , 9.5.x ,… HDL Works EASE 9.6 Rev2 Win/Linux Tested Picture 功能与优势 图形化设计环境,可自动生成分层 VHDL 或 Verilog 代码 符合以下标准: – VHDL:IEEE-1076 87、93 等2008 – Verilog:IEEE-1364 95、2001、2005 – SystemVerilog:IEEE-2005、2009、2012、2017 虚拟记录可降低图表复杂性并提高灵活性 真正的多用户设计环境和相关的版本控制,由功能强大的设计环境浏览器管理 一键导入旧版 Verilog 或 VHDL 设计并提取图形层次结构 与业界最流行的仿真器和综合工具无缝集成 平台无关的数据库 集成 HDL 语言编辑器 实时错误报告 What is new in the 9.6 release More Information in English: HDL Works EASE 9.6

.2026.png)