CAD-Earth 旨在轻松地在 Google Earth 和主要 CAD 程序之间导入/导出图像、对象和地形网格,并创建动态等高线和剖面图。

可用版本: 8.x , …

支持CAD版本: AutoCAD2021-2027.exe , BricscadV25Pro , ZWCAD2025

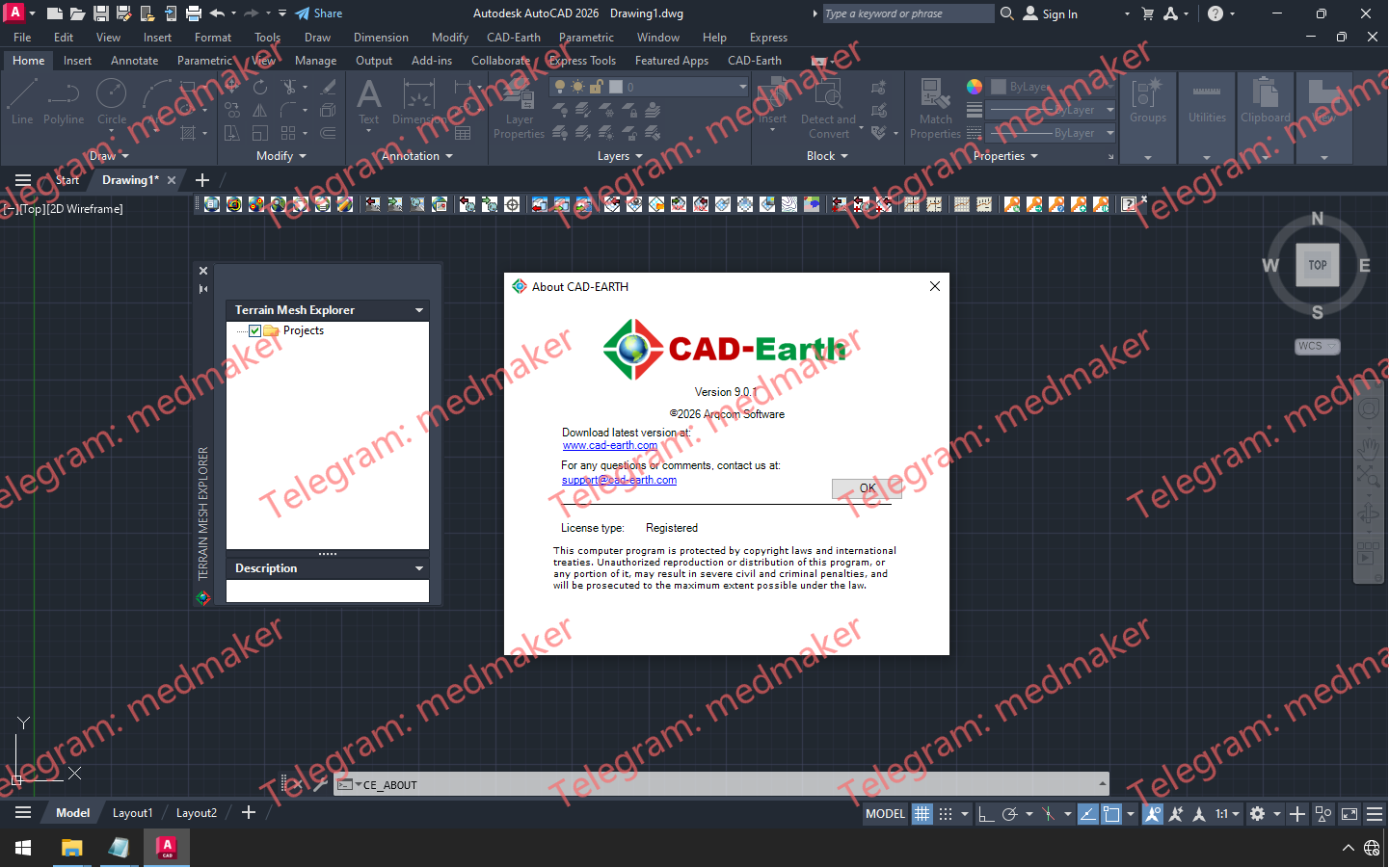

Arqcom CAD-Earth Premium 2026 v9.0.1

CAD-Earth 9 新增功能:

• 3D 模型导出到 SketchUp 无缝地将 AutoCAD、Civil 3D 和 BricsCAD 中的 3D CAD 模型直接导入 SketchUp,以便进行可视化和演示。

• 专业的地形网格编辑 新增专用命令,可更精确、更有效地插入、删除、移动、调整高程和编辑地形网格顶点。

• 优化的计算算法 采用优化的算法,显著提升地形分析、体积计算和等高线生成的处理速度。

• 增强的 AI 图像处理 改进的 AI 神经网络可显著提升图像清晰度、色彩平衡和分辨率——最高可实现 4 倍放大,并呈现自然效果。

• 更快的图像预览 导入卫星图像前即可即时预览,确保定位正确,并为您的项目选择最佳的供应商。

CAD-Earth 能做什么?

• 插入来自 Google Earth 和其他提供商的图像。您可以选择不同的服务提供商(Google Earth、Google、Bing、ESRI、Mapbox)、图像分辨率(普通、中、高、最高)和图像模式(卫星、地图、混合)。图像可以以全彩或灰度格式导入到 AutoCAD 中,支持主流图像格式(BMP、JPEG、TIFF),并且可以裁剪到闭合折线内。您可以创建一个包含空间数据信息的世界文本文件,用于对导入的图像进行地理配准。在将图像导入 AutoCAD 之前,您可以选择不同的图像提供商来预览图像。

• 将 Google Earth 对象导入到 AutoCAD。您可以将 Google Earth 中的多边形、路线和地标导入到 AutoCAD 和基于 AutoCAD 的产品,例如 Civil 3D。多边形可以作为投影到地形的 2D 或 3D 折线导入,并可选择应用填充颜色。地标可以作为包含高程的块导入,包括地标名称和描述。内置符号库,您可以在其中选择要插入的地标块,也可以添加自己的块。块和嵌套块中包含的实体可以导出到 Google Earth。系统将创建一个 KMZ 文件,其中包含在 Google Earth 中显示对象所需的所有信息。

• 从 DAE、3DS、FBX 和 OBJ 文件导入和导出 3D 模型到 AutoCAD,并将其以及其他 3D 实体(例如 3D 实体、区域、网格或多边形网格)导出到 Google Earth。包含在常规块或嵌套块中的 3D 实体也可以导出。

• 插入地理参考图像。如果您拥有包含空间数据信息的相应世界文件的图像文件,则可以自动应用 XY 比例和平移变换,将其精确地放置在图形中。

• 将 CAD 对象导出到 Google Earth。线、折线、圆弧、圆、点可以作为多边形、路径或地标导出到 Google Earth。可以调整对象的线粗、轮廓、填充颜色和不透明度。可以通过指定最大线段长度和偏转角来控制曲线平滑度。还可以设置地标名称、描述、比例和图标。

• 将 CAD 屏幕截图导出到 Google Earth。AutoCAD 图形可以作为图像叠加层导出到 Google Earth。图像捕获可以是全彩色、灰度或黑白,并支持所有主流图像格式(BMP、JPEG、TIFF、PNG、GIF)。背景颜色可以完全透明,也可以根据需要更改为其他颜色。屏幕截图还可以分段拍摄,以提高最终图像分辨率。系统将创建一个包含图像文件的 KMZ 文件,以避免在找不到文件时显示空白图像。

• 从 Google Earth 获取等高线、纵断面和剖面图(Plus 版本)。可以在现有闭合折线内或沿折线路径创建地形配置网格,方法是计算 Google Earth 中的点高程。通过指定旋转角度和分辨率,可以调整网格密度和精度。生成的网格可用于获取等高线、动态纵断面和带有注释的剖面图。地形网格可以导出为 LandXML 文件,以便导入到其他能够从 LandXML 文件创建曲面的应用程序,例如 Civil 3D。

在网格查看器(Premium)中,您还可以执行以下操作:

• 即时获取挖填体积计算结果,并与网格上选定的点或图形中选定的现有闭合折线所定义的区域内的另一个网格进行比较。您可以预览挖填区域的颜色和透明度,并在图形中插入挖填体积汇总表以及分析区域的平面图。

• 按高程或坡度范围查看曲面,为每个范围定义颜色和最小值/最大值,并在图形中插入包含相应平面图的汇总表。

• 即时显示等高线,定义等高线颜色、间距和基准高程。

• 创建动画视频,定义摄像机位置、视角方向、速度和暂停时间。生成的文件可以使用任何兼容mp4格式的播放器打开,例如Windows Media Player。

• 直接在网格上沿任意 XYZ 轴和平面测量距离、坡度和角度。

• 打开网格横截面查看器,您可以在其中查看网格横截面的正交视图。

• 截取当前视图的屏幕截图,并将其保存为图像文件或将其作为栅格图像参考插入到当前图形中。

• 从 LandXML 文件导入曲面,该文件来自其他可以保存此文件格式曲面信息的软件应用程序,例如 Civil 3D。导入的网格与 CAD-Earth 命令完全兼容。

• 将图形中的现有图像链接到地形网格。如果在网格查看器中打开网格,图像将投影到网格上,而不是以纯色显示。将图像链接到地形网格后,如果移动、旋转或缩放网格,图像将相应更新。

• 通过选择图形中现有的 3D 面来创建网格。此命令可用于将先前 CAD-Earth 版本中的网格转换为新格式。

• 网格命令。

• 使用命令编辑网格,包括插入、删除、移动、调整高程、展平顶点以及反转、删除或切割三角形。可以插入断裂线来细化地形配置。可以平滑网格并将其调整到控制网格或控制点。

• 从现有实体(例如点、3D 面、等高线折线或 3D 折线)创建地形网格。

• 导入和导出地形网格。从 Lidar LAS 和 DEM 文件(TIFF、DEM、HGT、E00、MEM、CAT.DDF)导入网格,指定网格属性、细化选项和其他处理参数,可以选择处理整个文件或选择要处理的区域。将地形网格导出为文本 XYZ 文件或 GeoTIFF 文件。

• 网格可视化样式。显示一个或多个网格地形元素,例如顶点、三角剖分、边界、等高线、高程和坡度范围以及坡度箭头。您可以编辑、创建、删除和保存可视化样式,并选择要显示的元素。颜色、线型宽度和比例、文本样式和大小均可调整,参数值也可修改。

• 工具

• 地形网格浏览器。一个浮动调色板工具,用于组织您的项目,并提供网格导入、编辑和可视化命令。右键单击树节点,即可添加子项目文件夹和地形网格节点。右键单击节点,将显示上下文菜单,以便根据所选节点选择命令。

• 剖面查看器。通过定义一条指定两点的切割线,显示所选地形网格的剖面。您可以调整剖面的垂直比例,在剖面查看器中选择两点测量距离和坡度,缩放到范围或窗口,增大或缩小视图大小,平移视图,以及显示或隐藏参考网格。

• 土方量计算命令。

• 使用网格法进行挖填方量计算。在定义区域内的每个网格交点处,计算网格与对比网格之间的深度。网格的每个元素均可自定义,包括线型、颜色、图层和比例、文本大小、样式和颜色。

• 可生成体积汇总报告,显示每个网格点的平均挖填方深度、单元部分面积、挖填方面积和体积。报告还会显示网格单元的宽度和高度、收缩率、表土带深度以及净挖填方面积和体积。体积计算完成后,此电子表格将自动在 Excel® 中打开。

More Information in English: Arqcom CAD-Earth Premium 2026 v9.0.1